## THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## Models and Methods for Development of DSP Applications on Manycore Processors

Jerker Bengtsson

School of Information Science, Computer and Electrical Engineering HALMSTAD UNIVERSITY

Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY

Göteborg, Sweden, June 2009

#### Models and Methods for Development of DSP Applications on Manycore Processors

Jerker Bengtsson ISBN 978-91-7385-288-3

© Jerker Bengtsson 2009.

Doktorsavhandlingar vid Chalmers tekniska högskola Ny serie nr 2969 ISSN 0346-718X

Department of Computer Science and Engineering Chalmers University of Technology Technical Report No 62D.

#### **Contact Information:**

Department of Computer Science and Engineering Chalmers University of Technology SE-412 96 Göteborg, Sweden Telephone: +46 (0)31 772 1000 Fax: +46 (0)31 772 3663 URL: http://www.ce.chalmers.se

School of Information Science, Computer and Electrical Engineering Halmstad University Box 823 SE-301 18 Halmstad, Sweden Telephone: +46(0)35 16 71 00 Fax: +46(0)35 12 03 48 URL: http://www.hh.se/ide

Printed by Chalmers Reproservice Göteborg, Sweden, Maj 2009.

## Abstract

Advanced digital signal processing systems require specialised high-performance embedded computer architectures. The term high-performance translates to large amounts of data and computations per time unit. The term embedded further implies requirements on physical size and power efficiency. Thus the requirements are of both functional and non-functional nature.

This thesis addresses the development of high-performance digital signal processing systems relying on manycore technology. We propose building twolevel hierarchical computer architectures for this domain of applications. Further, we outline a tool flow based on methods and analysis techniques for automated, multi-objective mapping of such applications on distributed memory manycore processors. In particular, the focus is put on how to provide a means for tunable strategies for mapping of task graphs on array structured distributed memory manycores, with respect to given application constraints. We argue for code mapping strategies based on predicted execution performance, which can be used in an auto-tuning feedback loop or to guide manual tuning directed by the programmer.

Automated parallelization, optimisation and mapping to a manycore processor benefits from the use of a concurrent programming model as the starting point. Such a model allows the programmer to express different types and granularities of parallelism as well as computation characteristics of importance in the addressed class of applications. The programming model should also abstract away machine dependent hardware details. The analytical study of WCDMA baseband processing in radio base stations, presented in this thesis, suggests dataflow models as a good match to the characteristics of the application and as execution model abstracting computations on a manycore.

Construction of portable tools further requires a manycore machine model and an intermediate representation. The models are needed in order to decouple algorithms, used to transform and map application software, from hardware. We propose a manycore machine model that captures common hardware resources, as well as resource dependent performance metrics for parallel computation and communication. Further, we have developed a multi-functional intermediate representation, which can be used as source for code generation and for dynamic execution analysis.

Finally, we demonstrate how we can dynamically analyse execution using abstract interpretation on the intermediate representation. It is shown that the performance predictions can be used to accurately rank different mappings by best throughput or shortest end-to-end computation latency.

**Keywords:** parallel processing, manycore processors, high-performance digital signal processing, dataflow, concurrent models of computation, parallel code mapping, parallel machine model, dynamic performance analysis.

## Sammanfattning

Avancerade inbyggda signalbehandlingssystem kräver ofta specialiserade och högpresterande datorplattformar. Med högpresterande menas att stora datavolymer och beräkningsintensiva algoritmer måste processas inom ett begränsat tidsintervall. Inbyggda system har generellt oftast krav på att understiga en viss fysisk storlek och att de måste vara energieffektiva.

Denna avhandling fokuserar på användning av flerkärniga processorer för konstruktion av högpresterande signalbehandlingssystem. Vi föreslår en datorarkitektur, i form av en två-nivå hierarki, för denna typ av signalbehndlingssystem. Vidare presenterar vi ett verktygsflöde baserat på metoder och analystekniker för automatiserad mappning av sådana tillämpningar på flerkärniga processorer med distribuerat minne. Mer specifikt, vi fokuserar på flerkärniga strategier för kravstyrd mappning av beräkningsgrafer på flerkärniga processorer organiserade i en två-dimensionell matrisstruktur. Vi förespråkar automatiskt eller manuellt styrd reglering av mappingsdirektiv, där beslut baseras på återkoppling av prognostiserade exekveringsegenskaper.

Automatiserad parallellisering, optimering och mappning på en flerkärnig processor kan förenklas avsevärt genom att utgå ifrån en lämplig parallell programmeringsmodell. En sådan modell tillåter en programmerare att uttrycka olika typer och olika kornigheter av parallellism samt beräkningskarakteristik, typiska för de typer av tillämpningar som adresseras. En sådan programmeringsmodell måste också abstrahera bort processorspecifika hårdvarudetaljer. En analys av basbandsprocessning i WCDMA radiobasstationer, som presenteras i denna avhandling, pekar ut dataflödesmodeller som mycket lämpliga för att programmera denna typ av tillämpningar, samt som exekveringsmodeller för program mappade på flerkärniga processor.

För att kunna konstruera portabla utvecklingsverktyg krävs det en lämplig modell av flerkärniga processorer samt en mellanrepresentation. Processormodellen behövs för att kunna utveckla maskinoberoende algoritmer för transformering och mappning av program. Vi föreslår en flerkärnig processormodell som fångar typiska hårdvaruresurser, såväl som dess grundläggande, parallella beräkningsoperationer. Vidare har vi utvecklat en multifunktionell mellanrepresentation, vilken kan användas som utgånspunkt för kodgenerering och för dynamisk exekveringsanalys.

Slutligen, denna avhandling visar ytterligare hur vi kan prognostisera dynamiska programegenskaper vid exekvering på flerkärniga processorer, genom att tillämpa abstrakt tolkning av mellanrepresentationen. Vi demonstrerar hur resultatet av dessa prognoser kan användas för att rangordna programmappningar enligt bäst periodisk genomströmning av data eller kortast svarstid.

### Acknowledgements

There are several people who more or less have had some influence on my work and the decisions I have made during the very crooked path leading to completion of this thesis.

My main supervisor Bertil Svensson ( $Duracell^{TM}$  Inside) for his encouragement, experienced advices and never fading enthusiasm and positiveness. Not to forget, for all the time (weekends and evenings) spent reading papers, reports and my theses produced during these years.

My assistant supervisor, Verónica Gaspes for providing constructive criticism, concrete inputs and suggestions, and for being a good source for moral support and advices in issues of non-functional character in life and work.

Professor Edward Lee, for hosting and inspiring me greatly and giving me very valuable advices and suggestions during my very fruitful visit at University of California at Berkeley. Also, thanks to Man-kit "Jackie" Leung for discussing and providing solutions to problems that popped up during my first close encounter with Ptolemy and the code generator framework during my stay in Berkeley.

A large deal of this work has been done in various forms of cooperation and discussions with with Ericsson AB. I am very greatful to Anders Wass who got the leading role in the Ericsson relay race and hosted me and spent valuable time discussing and supporting me during and after my stays in Kista. The baton was later handed over to Henrik Sahlin and Peter Brauer who continued guiding me through the LTE jungle, which greatly helped me when struggling with how to find an academic entry point to real problems, finding the right levels of abstraction and to obtain valuable insights into the industrial world. These industrial connections have provided me with a great deal of insights and experiences which can only be read between the lines in this thesis.

Professor Marina Papatriantafilou, for being actively committed as external advisor in my support committee. Despite the limited room for meetings, there has always been a positive and friendly attitude, and a good use of this limited time leading to useful outcome.

Roland Thörner, who have absolutely nothing at all to do with this thesis, but who is a very nice bloke and friend in his best years having a rarely good sense of humor.

Finally, last but not least, my wife and constant brother in arms Hoai. Con kiên công con voi. Anh yêu em.

The work presented in this thesis has been funded by research grants form the Knowledge Foundation and Ericsson AB.

## Contents

| $\mathbf{A}$ | bstra           | $\operatorname{ct}$                                  | iii                    |

|--------------|-----------------|------------------------------------------------------|------------------------|

| A            | ckno            | wledgements                                          | $\mathbf{v}$           |

| Τa           | able (          | of Contents                                          | $\mathbf{vi}$          |

| Li           | sts o           | f Appended Papers                                    | x                      |

| O            | $\mathbf{ther}$ | publications                                         | $\mathbf{x}\mathbf{i}$ |

| 1            | INT             | TRODUCTION                                           | 1                      |

|              | 1.1             | Microprocessor evolution: multicore versus manycore  | 2                      |

|              | 1.2             | High-performance digital signal processing           | 2                      |

|              | 1.3             | Scope of the thesis                                  | 3                      |

|              | 1.4             | Problem description                                  | 4                      |

|              | 1.5             | Research goals and approach                          | 5                      |

|              | 1.6             | Contributions of the thesis                          | 6                      |

|              | 1.7             | Outline of the thesis                                | 8                      |

| <b>2</b>     |                 | CRARCHICAL ARCHITECTURE FOR EMBEDDED HIG             |                        |

|              |                 | RFORMANCE SIGNAL PROCESSING                          | 11                     |

|              | 2.1             | Embedded high-performance DSP systems                | 12                     |

|              | 2.2             | A hierarchical manycore architecture                 | 13                     |

|              | 2.3             | Reconfigurable micro level structures                | 13                     |

|              | 2.4             | Evaluation of a reconfigurable micro level structure | 15                     |

|              |                 | 2.4.1 Evaluating area performance                    | 16                     |

|              |                 | 2.4.2 Evaluating resource utilisation                | 18                     |

|              | 2.5             | Implications for the further work                    | 19                     |

| 3            | AN              | ALYSIS OF WCDMA BASEBAND PROCESSING                  | 21                     |

|              | 3.1             | WCDMA and the UTRAN architecture                     | 22                     |

|              |                 | 3.1.1 The RBS                                        | 22                     |

|          |     | 3.1.2           | Downlink transport channel multiplexing         | 23              |

|----------|-----|-----------------|-------------------------------------------------|-----------------|

|          | 3.2 | Downli          | ink processing analysis                         | 23              |

|          |     | 3.2.1           | Types of parallelism                            | 25              |

|          |     | 3.2.2           | Real-time characteristics                       | 25              |

|          |     | 3.2.3           | Parameter configuration                         | 26              |

|          |     | 3.2.4           | Function level parallelism                      | 27              |

|          |     | 3.2.5           | Intra function characteristics                  | 27              |

|          |     | 3.2.6           | 3G service use cases                            | 28              |

|          |     | 3.2.7           | Mapping study of the use cases                  | 29              |

|          | 3.3 | Summa           | ary and implications                            | 30              |

| 4        | STI | REAM            | ING MODELS OF COMPUTATION                       | <b>31</b>       |

|          | 4.1 | Introdu         | uction                                          | 32              |

|          |     | 4.1.1           | Domain specific programming solutions           | 32              |

|          |     | 4.1.2           | Stream processing                               | 33              |

|          | 4.2 | Synchr          | conous dataflow                                 | 34              |

|          |     | 4.2.1           | Description of SDF                              | 35              |

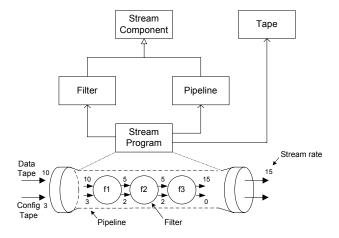

|          | 4.3 | Stream          | hIt: a language implementing SDF                | 37              |

|          |     | 4.3.1           | Limitations in StreamIt                         | 37              |

|          | 4.4 | A mod           | lelling framework for SDF languages             | 38              |

|          |     | 4.4.1           | The StreamBits language                         | 38              |

|          | 4.5 | Relate          | d work                                          | 39              |

| <b>5</b> |     |                 | E MODEL, INTERMEDIATE REPRESENTATION            |                 |

|          |     |                 | STRACT INTERPRETATION                           | 41              |

|          | 5.1 |                 | ore code mapping tool                           | 42              |

|          | 5.0 | 5.1.1           | Target processors                               | 43              |

|          | 5.2 |                 | set                                             | 44              |

|          |     | 5.2.1           | Application model                               | 44              |

|          | 5.0 | 5.2.2<br>Time d | Machine model                                   | 45<br>46        |

|          | 5.3 | 5.3.1           | configuration graphs                            | $46 \\ 47$      |

|          | 5.4 |                 | to interpretation of timed configuration graphs | $\frac{47}{47}$ |

|          | 0.4 | 5.4.1           | Interpretation using Process Network            | 48              |

|          |     | 5.4.2           | Modelling limitations of the IR                 | 40<br>50        |

|          | 5.5 | 0.1.1           | ating modelling accuracy                        | 50              |

|          | 0.0 | 5.5.1           | Experimental mapping cases                      | 51              |

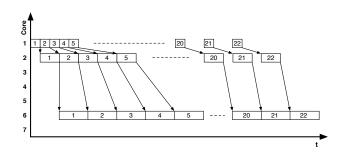

|          |     | 5.5.2           | Execution strategy                              | 52              |

|          |     | 5.5.3           | Comparing communication costs                   | 52              |

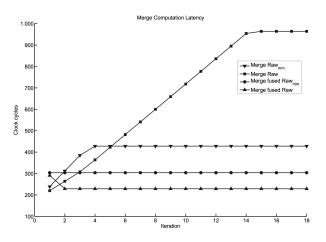

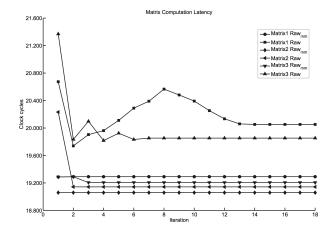

|          |     | 5.5.4           | Latency and throughput measurements             | 54              |

|          | 5.6 | Discuss         | sion of the results                             | 56              |

|          | 5.7 |                 | d work                                          | 57              |

|          |     |                 |                                                 |                 |

| 6   | $\mathbf{CO}$ | NCLUSION    | $\mathbf{S}$ | A] | NI | ) | $\mathbf{F}$ | U' | ΓU  | J | RE | C | W | 70 | )] | RI | K |   |   |  |  |   |  |   | <b>61</b> |

|-----|---------------|-------------|--------------|----|----|---|--------------|----|-----|---|----|---|---|----|----|----|---|---|---|--|--|---|--|---|-----------|

|     | 6.1           | Conclusions |              |    |    |   |              |    |     |   |    |   |   |    |    |    |   |   |   |  |  |   |  |   | 62        |

|     | 6.2           | Future work |              |    |    | • |              |    | • • |   |    | • | • |    |    | •  |   | • | • |  |  | • |  | • | 63        |

| Bi  | bliog         | graphy      |              |    |    |   |              |    |     |   |    |   |   |    |    |    |   |   |   |  |  |   |  |   | 64        |

| Lis | st of         | Figures     |              |    |    |   |              |    |     |   |    |   |   |    |    |    |   |   |   |  |  |   |  |   | 71        |

| Lis | st of         | Tables      |              |    |    |   |              |    |     |   |    |   |   |    |    |    |   |   |   |  |  |   |  |   | 73        |

## Lists of Appended Papers

This thesis is based on the work contained in the following papers:

- Paper A Johnsson, D., Bengtsson, J., and Svensson, B. (2004). Two-level reconfigurable architecture for high-performance signal processing. In Proc. of Engineering of Reconfigurable Systems and Algorithms (ERSA'04), pages 177-183, Las Vegas, USA.

- Paper B Bengtsson, J. (2006). Baseband processing in 3G UMTS radio base stations. Technical Report IDE0629, School of Information Science, Computer and Electrical Engineering, Halmstad University, 2006.

- Paper C Bengtsson, J., and Svensson, B. (2006). A configurable framework for stream programming exploration in baseband applications. In Proc. of The 11th Int'l Workshop on High-Level Programming Models And Supportive Environments (HIPS'06) in conjunction with IPDPS (IPDPS 2006), Rhodes, Greece.

- Paper D Bengtsson, J. and Svensson, B. (2008). A domain-specific approach for software development on manycore platforms. ACM Computer Architecture News, Special Issue: MCC08 - Multicore Computing 2008, 39(6):2-10.

- Paper E Bengtsson, J., and Svensson, B. (2009). Manycore performance analysis using timed configuration graphs. To appear in *Proc of. Int'l Symp.* on Systems, Architectures, Modeling and Simulation (SAMOS IX 2009), Samos, Greece.

## **Other Related Publications**

- Bengtsson, J. (2006a). Efficient Implementation of Stream Applications on Processor Arrays. Licentiate Thesis, Chalmers University of Technology, March 30, 2006.

- Bengtsson, J., Gaspes, V., and Svensson, B. (2007). Machine assisted code generation for manycore processors. *Real-time in Sweden, Västerås (RTIS* 2007).

- Bengtsson, J. and Svensson, B. (2008a). A set of models for manycore performance evaluation through timed configuration graphs. Technical Report IDE0856, School of Information Science, Computer and Electrical Engineering, Halmstad University, 2008.

- Bengtsson, J. and Svensson, B. (2008b). Methodologies and tools for development of signal processing software on multicore Platforms. Workshop on Streamings Systems in conjunction with 41st Annual IEEE/ACM International Symposium on Microarchitecture (MICRO 41).

- Bengtsson, J., and Svensson, B. (2008c). A domain-specific approach for software development on manycore platforms. In Proc. of First Swedish Workshop on Multicore Computing (MCC08).

Chapter 1 INTRODUCTION

## 1.1 Microprocessor evolution: multicore versus manycore

The microprocessor industry has long been able to deliver increased performance of processors incited by Gordon Moore's predictions. This has to a large extent been possible through technology scaling of transistors and wires, continuously increased clock frequencies and adding more specialised functional units around a centralised processor architecture. However, an undesirable side effect of the technology scaling and the clock frequency race has been a rapid increase in power dissipation, which started to push cooling technology to its limit in the first years of 2000 [Carmean and Hall, 2001]. In 2005, Intel and AMD made a significant change in their directions on the chase for more power efficient performance, starting from a single core architecture and then doubling the amount of cores per semiconductor process generation. The term multicore has become highly associated with this concept. There are many arguments for why this rather narrow minded design shift will unlikely be the ideal solution for dramatic improvements in power performance [Asanovic et al., 2006]. Sustainable and evolutionary solutions for parallel processing must be sought from a broader perspective. As a response to this, the term *manycore* was coined at the University of California at Berkeley to distinguish new and innovative parallel processor architectures from the more limiting core doubling convention.

## 1.2 High-performance digital signal processing

High-performance signal processing systems, such as advanced radar systems, has long required computer architectures capable of delivering performance largely exceeding the performance of general purpose computer systems. Parallel embedded computer architectures were early been a must to manage the processing requirements in such systems, and future generations will keep pushing these requirements higher [Åhlander, 2007]. Another similar example is the signal processing required in radio base stations (RBS). In practice, an RBS is a highly advanced parallel computer system. A state-of-the-art platform for 3G WCDMA RBSs is typically designed using the latest ASIC and FPGA technologies to maximise the capability of serving as many number of concurrent lines as possible [Zhang et al., 2003]. Further, each RBS site typically contains many such parallel platforms.

Although there are many dissimilarities between these two examples of high-performance signal processing systems, there is at least one very important common denominator: development complexity and manufacturing cost. Radar systems are typically produced in smaller series, which makes the cost per system for ASIC development very high. In the telecommunication industry, the production series are much longer, which therefore makes the ASIC cost per system much lower compared to radars. However, the cost of developing ASICs increases dramatically for each semiconductor technology generation. Furthermore, new and more complex functionality keeps being added to each system generation. Thus, reducing manufacturing costs is one argument for industry's interest in using more commercial-of-the-shelf (COTS) manycore hardware.

Taking wireless telecommunication industry as example, the trend is that a growing part of the baseband platforms are implemented using programmable hardware technology. An RBS typically has a life expectancy counted in decades. Using programmable technology enables performance upgrading and forward-compatibility; new standardised functionalities and improved algorithms can be integrated after system roll-out. Moreover, different customers need different system solutions to meet their specific site requirements and have the ability to modify the network with respect to communication. This puts further requirements on platform scalability.

## **1.3** Scope of the thesis

This thesis addresses a few of the many problems related to system and software development for using manycore technology in embedded computer architectures for high-performance signal processing applications. We focus on array structured, software cached, distributed memory manycore processors. We believe that such machines provide good hardware scalability and good means for predictable timing.

We address a certain class of high-performance digital signal processing systems. We translate the term high-performance to real-time constrained processing of large amounts of data and computation intensive algorithms. We focus on embedded systems, thus there are further requirements on physical size and power efficiency. Therefore, the requirements are of both functional and non-functional nature. Applications that fit within this class are, e.g. baseband processing in radio base stations and signal processing in modern radar systems. Applications not belonging to this class are, e.g. weather simulations and scientific computations, since there typically is no strict requirements on response time.

Multi-processors have been widely explored in research since the 1980s and early 1990s. There has also been a great deal of research on parallel programming models. We have focused on finding solutions for manycore programming and code mapping based on this earlier work; more specifically, we have investigated methods and techniques based on dataflow models of computation.

The problem of mapping task graphs to a parallel processing hardware is well studied, and many solutions for automation of that problem exist. Given such a mapping, we focus on analysis techniques for the prediction of run-time properties of such task graphs on the category manycore targets addressed.

## 1.4 Problem description

We are interested in performance efficient DSP task graph mapping on highly parallel, generic manycore hardware. We are especially interested in self-timed task graph mappings, which put minimal requirements on run-time overhead for execution on manycore hardware [Lee and Ha, 1989]. To find solutions to this overall problem, we were motivated to address the following questions:

- What are the trade-offs concerning system development using different paradigms of manycore processors? Fine-grained manycores with reconfigurable interconnections theoretically offer a larger area performance compared to more coarse-grained manycores. However, reducing core hardware implemented functionality means that a certain part of the hardware resources must be used to configure corresponding functionality through software. Examples of such functionality can be memory address and cache logic and configuration of data paths (switching/routing functionality). How does this strategy of moving certain functionality to software normally implemented in hardware impact on practically achievable area performance?.

- What are the typical computation characteristics and processing requirements in embedded high-performance DSP systems? Embedded high-performance DSP systems typically contain large amounts of logical parallelism. These kinds of embedded systems are usually also associated with a set of non-functional constraints, for example real-time constraints. Furthermore, the hardware resources must be shared for many concurrent processing tasks. To be able to determine requirements on programming models, target hardware and mapping strategies for such hardware, it is necessary to analyse typical algorithm characteristics, logical parallelism etc. from a system perspective.

- What is a suitable parallel model of computation for DSP applications? Automated mapping of application software requires well-defined parallel models of computation. Fewer and fewer are those who still believe that the non-concurrent, shared memory programming model offered by the C language is a good starting point for automated mapping to parallel hardware. A suitable parallel model of computation must offer concurrency but also provide means for manycore hardware independence.

• What is a suitable machine abstraction for manycore processors? Tools and application software must be portable. This requires suitable intermediate representations for modular tool building. Further, the target embedded systems are also associated with constraints of a non-functional nature. Thus, the optimisation of DSP task graphs to manycore hardware is a complex, multi-objective task with many trade-offs. To deal with optimisation coupled to non-functional constraints, we believe that such intermediate representations need to capture time and offer means for analysis of dynamic execution costs.

## 1.5 Research goals and approach

The overall goals of this thesis work are:

- 1. to investigate trade-offs in signal processing implementation using different paradigms of manycore technology;

- 2. to investigate models, methods and techniques for computer assisted mapping of signal processing task graphs on manycore hardware; and

- 3. to develop techniques for analysing and predicting dynamic execution costs of DSP task graphs on manycores.

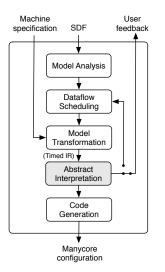

The research was initiated by studying and evaluating emerging manycore architectures [Bengtsson and Lundin, 2003]. To be able to analyse system design trade-offs related to the choice of hardware technology, we later conducted a study on parts of the physical layer processing in 3G radio base stations. For the parts of the system studied, we found the synchronous dataflow model of computation to offer a good match with the system and development requirements and with the manycore hardware addressed. Considering industrial requirements on tool and software portability, we further addressed methods and techniques for automated software mapping on parallel hardware. To abstract manycore hardware and to predict dynamic execution costs related to non-functional properties, we identified the need for a new manycore machine model providing realistic execution cost predictions and a multi-functional intermediate representation as an important research topic.

## **1.6** Contributions of the thesis

The contributions of this thesis are as follows:

## • Hierarchical processor architecture for high-performance signal processing

We propose a hierarchical manycore processor architecture for multidimensional signal processing platforms. We have investigated some of the trade-offs related to different core granularities by comparing two paradigms of existing manycore processors: a coarse-grained array of tightly coupled RISC cores and a fine-grained reconfigurable array of single instruction ALUs. In the latter, both control flow and data operations must be mapped spatially using one or several of ALUs. Given a certain chip area and assuming the same technology, our comparisons show that the finer grained array has a potential peak performance of almost a factor of 7 higher than the coarse-grained processor. Furthermore, we studied the impact on performance when large amounts of ALU resources need to be allocated for algorithm control flow. Our experiments shows that, even if using up to as much as 75 percent of the ALUs for algorithm control flow, it would still be competitive with the peak performance of the coarse-grained alternative.

#### • Processing requirements and characteristics in WCDMA baseband

We provide a comprehensive study of the complete set of processing functions specified for 3G WCDMA downlink baseband. In the study, we make an analysis of different types of potential parallelism. We discuss the functionality and characterise the intra-algorithm computations and data representations. On the basis of the study, we find that streamoriented models of computation constitute a very good match for describing the task and the pipeline parallelism that we identify on the function level in the WCDMA processing chain. On the intra-algorithm level, we also identify and discuss potential mapping on SIMD and MIMD parallel hardware. Moreover, we conclude that the requirements on instructionlevel computations are mostly of a logical, rather than an arithmetical, nature.

#### • Modelling framework for SDF based languages

We provide a framework specialised for the modelling of stream-oriented languages based on the synchronous dataflow model of computation. We used the StreamIt language in order to reason about implementation of WCDMA downlink processing using stream-oriented languages. On the basis of the WCDMA study, we identify a number of weaknesses related to expressiveness in the StreamIt language and propose language extensions related to data types and instruction level computations. Further, we introduce the notion of a control mode - for periodical reconfiguration of actors - and control streams - for distribution of actor reconfiguration parameters. We demonstrate language improvements by modelling an experimental language called *StreamBits*. In particular, we demonstrate how we can extend the StreamIt language with syntactic means to express computations on variable length bit-string data types.

#### • Models for manycore performance evaluation

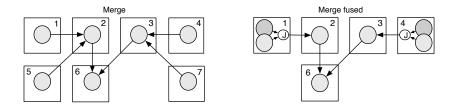

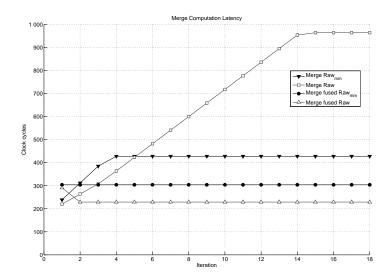

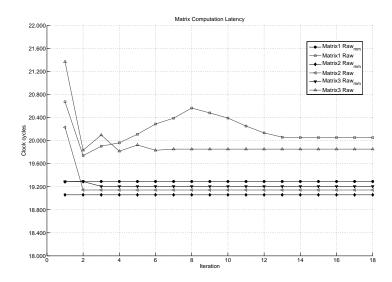

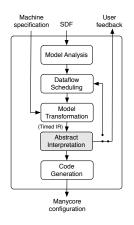

We developed a set of models to be used as a part of a manycore mapping and code generation tool. Manycore processors are described using a machine model that captures essential performance measures of array structured, tightly coupled manycore processors. Moreover, we developed a timed intermediate representation for manycore targets in the form of a heterogeneous dataflow model. We show how the intermediate representation is constructed for abstract interpretation, given a model of the application (SDF) and a specification of the machine as input. Thus, the use of the timed intermediate representation is two-fold: 1) we can by means of abstract interpretation obtain feedback about the run-time behaviour of the application and 2) we can use this IR as source for code generation to parallel targets. • Rank based feed back tuning using performance predictions We outline a design flow for iterative tuning of dataflow graphs on manycores using predicted performance feed back. The tool has two purposes: 1) to provide means for early estimates of application performance on a specific manycore and 2) to provide means for a programmer or an auto-tuner to tune mapping decisions on a manycore, based on feed back of predictions of a mapped application's dynamical behaviour. We evaluate the accuracy of the predictions calculated by our tool by making comparisons with measurements on the Raw processor. We show that we can fairly accurately predict both on-chip and off-chip communication costs. Furthermore, we show with our experiments that the tool's predictions can be used to correctly rank parallel mappings, by highest throughput and shortest end-to-end latency, when tuning an application implementation for such non-functional constraints.

## 1.7 Outline of the thesis

The thesis consists of two parts: a summary and a set of five appended papers. The six following chapters in the summary of the thesis are briefly summarised below.

- Chapter 2 summarises our work on investigating a domain specific computer architecture for embedded high-performance digital signal processing. We outline and motivate our proposal of a two level hierarchical architecture. Further, we make an analysis of area performance trade-offs associated with the choice of manycore structure and its core granularity.

- Chapter 3 presents a study of downlink baseband processing in 3G radio base stations. We summarise the function flow and its functional requirements, the inter as well as intra-function characteristics and we identify potential sources of logical parallelism. Further we discuss potential mapping of baseband use cases on common types of parallel processors.

- Chapter 4 introduces stream processing and dataflow models of computation in particular. Motivated by the baseband study in Chapter 3 and the type of manycore architectures discussed in Chapter 2, we especially focus on the synchronous dataflow model of computation. Furthermore, we briefly discuss data types and language constructions that we find useful for implementing baseband processing in languages based on the SDF model of computation. Finally, we end the chapter by discussing related work on stream-oriented languages.

- Chapter 5 presents our work on models for abstracting manycores and DSP applications. We further propose a manycore intermediate represen-

tation suitable for code generation and analysis of non-functional properties of SDF graphs when mapped on a particular manycore. The chapter is finalized with related work on techniques and methods for mapping task graphs on parallel processors. The chapter is ended by discussing further related work.

• Chapter 6 contains conclusions and suggestions for further work.

Chapter 2

# HIERARCHICAL ARCHITECTURE FOR EMBEDDED HIGH-PERFORMANCE SIGNAL PROCESSING

This chapter summarises our work on investigations of a domain specific computer architecture suited for embedded high-performance digital signal processing. We motivate and outline our proposal of a two level hierarchical architecture. Further, we focus on analysing area performance trade-offs associated with the choice of computation structure and its granularity in the lower abstraction level of our proposed architecture, as described in [Paper A].

## 2.1 Embedded high-performance DSP systems

We will first discuss some general system requirements that must typically be considered for a computer architecture for the targeted application domain. We discuss these requirements related to two examples of concrete applications within this domain: signal processing in RBS and in radar systems.

- **Parallelism** Embedded high-performance signal processing applications typically consist of several types and granularities of parallelism. From a system perspective, modern radars are developed to be capable of operating in different modes and using multiple parallel antenna inputs. In an RBS, the goal is to maximise the number of concurrent user channels having different requests on the types of services. The signal processing in a radar or an RBS constitutes pipelined function flows, exposing task, data and pipeline parallelism. Each function can further contain different amounts of fine-grained instruction level parallelism. We aim for an architecture that is flexible and that can be dimensioned for heterogeneous parallelism of variable amounts.

- Non-functional properties Both radar systems and radio base stations are real-time systems. Thus, one important type of non-functional constraints associated with such systems is time. New data are continuously streamed into the system by a certain periodicity (throughput) and its output must be produced within a certain time (end-to-end latency). A sufficient mapping of a function flow must also fulfil the specified system timing requirements. We must be able to offer appropriate parallel mapping strategies in order to process function flows of different structures and with different computation loads, with respect to some given timing requirements.

- Scalability A set of, often computationally demanding, functions is applied on multi-dimensional arrays of data collected from multiple antenna streams. Embedded high-performance systems are typically built using boards with multiple chips and even using multiple boards. The sizes and the dimensions of the data shapes processed by the function flows typically vary depending on for example the radar task or the number of connected users and the specific services each is requesting from the wireless

network. Thus, a domain specific computer architecture should be scalable in order to enable the designer to dimension a system for different requirements.

**System reconfiguration** A system must be able to dynamically adapt to periodically changing computation requirements. From a service scheduling point of view, the number of concurrent users and different types of service requests in an RBS can change frequently by a certain (often very short) periodicity. In practice, the size and the structure of the function flows and the workload for each function change. Since these changes are non-deterministic, the resource allocation must be done dynamically. In conclusion, the computer architecture should be able to allow for fast reconfigurations (dynamic resource allocation) of the processing resources to handle varying structures of the function flows and varying workloads of the functions.

## 2.2 A hierarchical manycore architecture

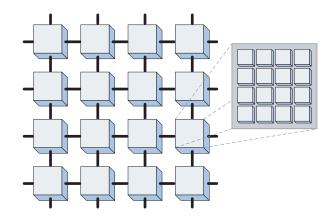

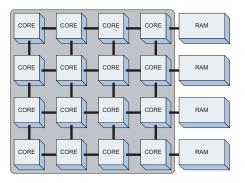

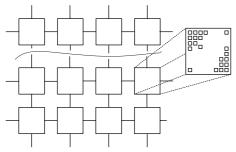

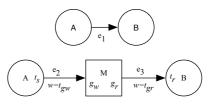

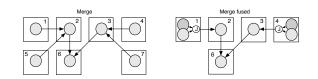

In [Paper A], we propose a mesh structured computer architecture using a two level hierarchical abstraction: a macro level structure and a micro level structure, see Figure 2.1. A mesh structure is easily scalable for different sizes of parallel structures, both on chip level as well as on the board level. Furthermore, the two level hierarchy provides an abstraction for both homogeneous and heterogeneous multiprocessor systems.

The macro level is a mapping abstraction for application and function level parallelism. A macro node can very well abstract, for example, a programmable manycore structure as well as a hardware implemented function accelerator.

The inside of a macro node constitutes the micro level structure. Depending on the type of micro level structure, the architecture allows exploitation of further task, pipeline, data and instruction level parallelism, in order to compute the mapped functions as efficiently as required.

In our work, we have primarily focused our investigations on micro level structures in the form of homogeneous manycore technology. This choice offers a highly flexible mapping space and also simplifies programmability and code mapping.

### 2.3 Reconfigurable micro level structures

In the most recent decade there has emerged a variety of different kinds of parallel and so called reconfigurable processor architectures. There is no well defined taxonomy for categorisation of such processors. Neither is there a good

Figure 2.1: A two level manycore hierarchy. Macro level nodes can be either specialised cores, dsp or, as illustrated by the figure, a micro level manycore structure.

definition, in our opinion, of what clearly distinguishes a "reconfigurable" processor from a "programmable" processor. Instead, such processors are usually coarsely compared by the granularity of the processing elements (PE), how the PEs (or cores) are networked to form a parallel computing structure and how computations and the mapping of programs are done [Mangione-Smith et al., 1997].

The probably most explored and also most fine-grained of (re)configurable structures are field programmable gate arrays (FPGA). However, such finegrained bit-level structures tend to require large amounts of logic to implement arithmetic operations, such as multiplication, on word length data. This issue has been addressed by the FPGA industry through embedding specialised word level arithmetic units, such as multipliers, in the fine-grained FPGA logic. However, the reconfiguration times in FPGAs are very long and therefore not fitted for system requirements of fast run-time reconfiguration.

Word level reconfigurable manycore processors represent one class of interesting manycore processors for signal processing functions. Interestingly, research investigations have shown that it is possible to achieve performances comparable with FPGAs for many applications requiring bit-level computations [Wentzlaff and Agarwal, 2004].

Many parallel processors have been designed in the form of an array structure, where the PEs (cores) are interconnected via a k-ary n-cubical network (that is, a network of n dimensions and k cores in each dimension). Considering wire densities in VLSI implementations of such networks, it was shown by William Dally in the early 1990s that low dimensional n-cubical networks yield lower communication latencies and higher hot spot throughput [Dally, 1990]. Research has later also suggested that it can be possible to build and efficiently utilise two dimensional array structures with thousands of coarse-grained cores [Moritz et al., 2001].

On the basis of these research findings and the characteristics of the application domain, which we described in Section 2.1, we have focused our interest on micro level structures in the form of mesh structured manycores.

# 2.4 Evaluation of a reconfigurable micro level structure

Regarding the type and design of micro level nodes, the main issue is to choose a manycore structure that offers a mapping space flexible enough for exploitation of different types and levels of potential parallelism within different functions. There are several aspects to consider, for example:

- What are the area performance trade-offs with respect to core granularity?

- What are the functional requirements at the micro level nodes?

- What is the cost for implementing control flows and address logic?

In [Paper A] we mainly addressed these three aspects to get some indicative answers. We chose to compare two different categories of existing manycore structures.

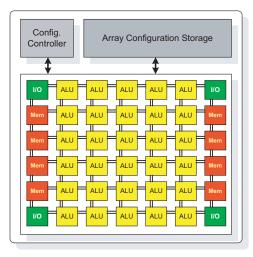

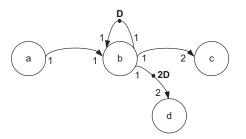

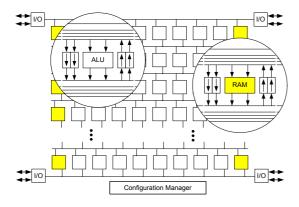

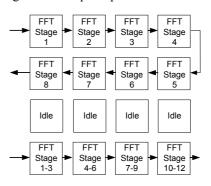

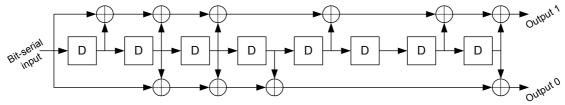

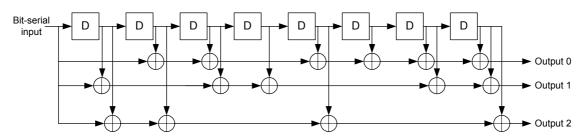

The first one, the XPP array architecture from PACT shown in Figure 2.2, is a homogeneous MISD (multiple instruction stream single data stream) array processor consisting of word length ALUs, which offers a spatial reconfigurable mapping space for algorithms [Baumgarte et al., 2001]. Using simple cores without instruction or data memory naturally enables a large amount of cores to be stamped out on a chip and thereby offers a large amount of instruction level parallelism. Similar to FPGAs, the array of cores must be reconfigured to switch from one algorithm to another. Further, each type of ALU operation is performed within one clock cycle. The output from a computing core is available for its nearest neighbours in the proceeding clock cycle. The XPP array has on-chip data memory distributed over a set of memory elements. These elements can also be combined to form larger logical memories, offering a larger address range when needed. The array has no dedicated controller logic to handle memory. Thus, memory read and write operations have to be implemented using one or a set of ALUs.

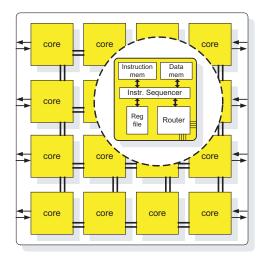

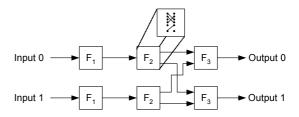

The other, the Raw micro processor, shown in Figure 2.3, is a more coarsegrained MIMD (multiple instruction stream multiple data stream) array of

Figure 2.2: The figure illustrates the XPP dataflow processing array, which is a reconfigurable MISD type of manycore.

fewer (16) cores, compared to the XPP array, but offers both temporal and spatial mapping of algorithms [Taylor et al., 2002]. The cores are MIPS processors with a slightly modified instruction set. Each core has instruction memory and a local (private) data cache. Moreover, Raw cores have floating point units. The cores are tightly coupled via four physical on-chip scalar operand networks - two statically and two dynamically routed - mapped via the register files. This means that the network can be treated as source and destination operands of an instruction (hence, the name scalar operand networks). The static network routers are programmable, so that static communication paths can be set up between cores. The dynamic networks are wormhole routed message passing networks, for core and memory communications of less deterministic nature.

#### 2.4.1 Evaluating area performance

We have studied a specific implementation of the XPP array architecture - the XPP-64A - and the first prototype implementation of Raw. It is difficult to make a fair area performance comparison between Raw and XPP-64A since they are of different types of architecture and are implemented in different process technology. For example, large parts of the area for each Raw tile is used for the floating point unit and for larger local data caches (Raw has in total 512 Kb compared to XPP's 12 Kb) and the processors are implemented in different silicon processes. Raw cores use 32 bit word length, while XPP-64As ALUs have 24 bit word length. Furthermore, the Raw processor and the

Figure 2.3: The figure illustrates the Raw micro processor, which is a MIMD type of manycore array.

| Processor  | Cores | Area $(mm^2)$ | Lithography ( $\mu m$ ) |

|------------|-------|---------------|-------------------------|

| Raw        | 16    | 250           | 0.15                    |

| XPP        | 64    | 32            | 0.13                    |

| XPP Scaled | 320   | 250           | 0.15                    |

Table 2.1: Comparison of instruction level parallelism per area for Raw with XPP and the scaled XPP.

XPP-64A run at different clock frequencies. It should also be mentioned that Raw has not in the first hand been implemented with the aim to maximise the number of cores. However, we still find it very interesting to make a coarse estimation of instruction level parallelism and performance per area to be able to reason about trade-offs between core complexity (size), performance and resource utilisation.

In the first part of our study, we evaluated area performance. Table 2.1 shows the number of cores on XPP-64A, the chip area and the lithography before and after up-scaling it to the same chip area and lithography used for Raw. We denote the scaled XPP array XPP Scaled. In our estimates, we calculated with a linear scaling from  $13\mu m$  lithography up to  $15\mu m$ , which was used for the first implementation of the Raw prototype. The result is naturally a much larger spatial computation space, offering 320 parallel instructions compared to the 16 of Raw.

| Processor  | <b>Frequency</b> $(MHz)$ | Peak Perf. $(GOPS)$ |

|------------|--------------------------|---------------------|

| Raw        | 225                      | 3.6                 |

| XPP        | 64                       | 4.1                 |

| XPP Scaled | 64                       | 24.5                |

Table 2.2: Comparison of peak performance for Raw with XPP and the scaled XPP.

Further we compared peak performances for Raw, XPP-64A and XPP Scaled, see Table 2.2. Due to the uncertainty regarding how fast it is physically possible to clock XPP Scaled, we chose to use the same clock frequency, 64 MHz, as is documented for the XPP64-A. However, earlier and larger implementations of the XPP array have been clocked at least at 100 MHz. It should also be mentioned that PACT has aimed for a low clock frequency for the XPP-64A in order to provide a low power performance ratio. Similarly, for the Raw prototype, the reported clock frequency was 225 MHz.

#### 2.4.2 Evaluating resource utilisation

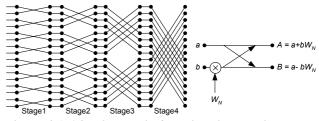

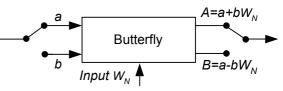

An obvious trade-off, by making cores simpler as in the XPP architecture, is that some amount of cores has to be used to implement algorithm control flows and memory control logic. In the second part of our study, we evaluate the resource utilisation ratio between control flow and data computations and what impact this ratio has on reachable performance. To evaluate resource utilisation, we implemented a Radix-2 FFT on the XPP-64A. FFT is an important class of algorithms used in DSP. The Radix-2 was chosen because it has a fairly complex dataflow pattern, requiring a large amount of control flow [Proakis and Manolakis, 1996].

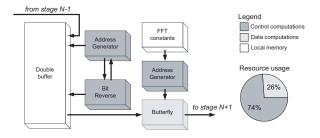

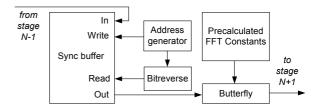

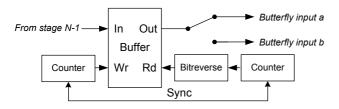

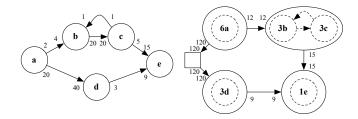

The Radix-2 FFT is logically computed in log n stages. We implemented an FFT module on the XPP-64A array, optimised for a stream throughput of one complex sample per clock cycle. This module can either be spread out in ninstances, to create pipelined computation of the FFT, or as a single instance, where the n stages are iteratively computed by a single FFT module. Figure 2.4 shows a high level block schematic of the implemented Radix-2 FFT module and how the utilised ALU resources are distributed in the form of control flow and of data computations.

A considerable part, 76% of the resources used, is used to implement algorithm control flow and memory management (address generation, double buffer synchronisation etc.). The remaining 26% used for computations corresponds to the butterfly computations. This relation in resource utilisation might seem highly inefficient, but it is important to bear in mind that ordinary micro processor program code requires portions of the code to do address calculations,

Figure 2.4: The block diagram to the left illustrates the implemented FFT module. The diagram to the right shows the amount of cores used for control flow and data flow respectively. Local memory was needed to be used for both double buffering, in order to relax synchronisation between FFT modules when mapped in a pipelined fashion, as well as for storing pre-calculated FFT constants

control flow (loops and conditional statements etc.) and synchronisation. Turning back to our calculations presented in Table 2.2, we can quickly establish that using only 15% of the XPP Scaled's resources still means that the XPP array is competitive compared to the peak performance of a more traditional CMP (chip multi processor) architecture (3.6/24.5). Even if it would probably be easier in practice to come close peak performance on Raw than on XPP, a part of the computations would still be temporal control flow, which will naturally decrease the throughput. Furthermore, our FFT implementation is capable of computing one complex valued sample per clock cycle, which, if not impossible, would at least be very difficult to achieve on a CMP due to longer communication latencies and a much more limited spatial mapping possibility.

## 2.5 Implications for the further work

Many algorithms in the DSP domain require less complex control flow compared to the FFT algorithm and can be mapped with good resource utilisation, thus reaching high performance. Other algorithms will need to utilise runtime reconfiguration when using micro level structures such as the XPP array. Johnsson et al. addressed the run-time reconfiguration aspects by analysing the requirements on speed of run-time reconfigurability from the perspective of a radar application [Johnsson et al., 2005]. This study concluded that reconfigurable array processors, like the PACT XPP, have the potential of managing the reconfiguration times as required in the radar use cases.

In our opinion, a more serious issue with manycore processors, such as the XPP and Raw, is that the programming complexity rapidly increases with the

number of cores. The implementation of the Radix-2 FFT required hardwarenear programming (using the native XPP assembly language) in order to optimise the dataflow (throughput) with respect to maximum I/O capacity. Further, the spatial placing and routing of the algorithm in whole was needed to be done fully manually. This low level programming proved to be very time consuming, error prone and very difficult in terms of debugging. Moreover, for industry, it would be strategically very risky to introduce such tight dependencies to a specific processor architecture. This is one of the main reasons why industry has been unwilling to use commercially available manycore technology.

The results of the experiments conducted in this study further motivated us to focus our research on parallel models of computation and programming methodologies for machine independent application development for array structured manycores. Chapter 3

# ANALYSIS OF WCDMA BASEBAND PROCESSING

This chapter is based on the contents of [Paper B], which is a study of one concrete, complex and relevant, industrial application: baseband processing of the WCDMA downlink in 3G radio base stations. The study has three main goals and contributions: 1) to summarise and provide a complete overview (abstraction) of the functional requirements in downlink baseband processing, 2) to characterise function level characteristics (such as data dependencies), intra function characteristics (such as data representation and instruction level computations) and, finally, 3) to identify potential exploitation of parallelism. The chapter will summarise the more important contents of the study and a give concluding discussion of the matching potential with stream/dataflow models of computation.

### 3.1 WCDMA and the UTRAN architecture

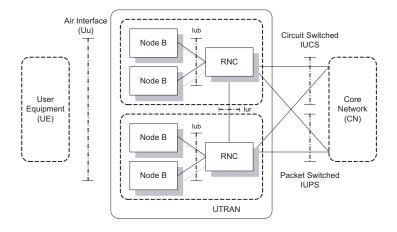

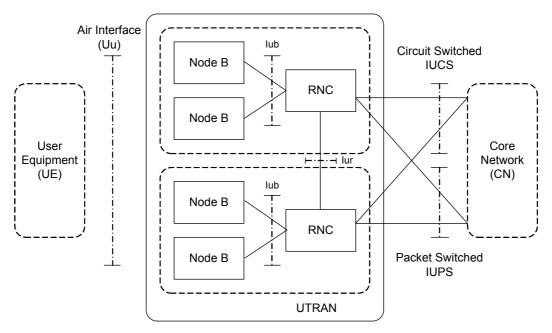

There are several 3G enabling technologies, such as EDGE, CDMA 2000 and WCDMA. The wideband code division multiple access (WCDMA) radio technology is the universal standard chosen by the 3GPP standardisation organisation for 3G mobile networks [Holma and Toskala, 2004]. The WCDMA technology constitutes the core of the UMTS terrestrial radio access network (UTRAN) architecture shown in Figure 3.1. The UTRAN architecture is built upon one or several radio network subsystems (RNS). An RNS is a sub-network comprising a radio network controller (RNC) and one or several Node B's. Node B is the terminology used by the 3GPP for a radio base station (RBS). At service requests from users, the RNC is responsible for setting up physical radio channels provided by the Node B.

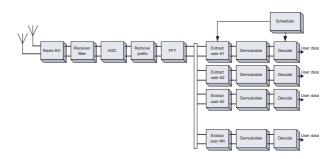

#### 3.1.1 The RBS

The RBS<sup>1</sup> implements the lowest layer of the UTRAN layers, i.e. the physical layer and the radio. The functionality of the RBS can generally be described as a mapping procedure of logical channels from higher layers (L2 and above) to the physical radio channels (L1). In the downlink (from the RBS to the user equipment), data frames from higher layers are encoded, multiplexed and modulated before radio transmission. In the uplink (from the user equipment to the RBS), physical channels are demodulated, de-multiplexed, decoded and mapped onto higher layer frame structures. More briefly, an RBS can be viewed as the modem in wireless telecommunication networks.

<sup>&</sup>lt;sup>1</sup>In the rest of the thesis we will use the term RBS when referring to Node B.

Figure 3.1: Utran.

#### 3.1.2 Downlink transport channel multiplexing

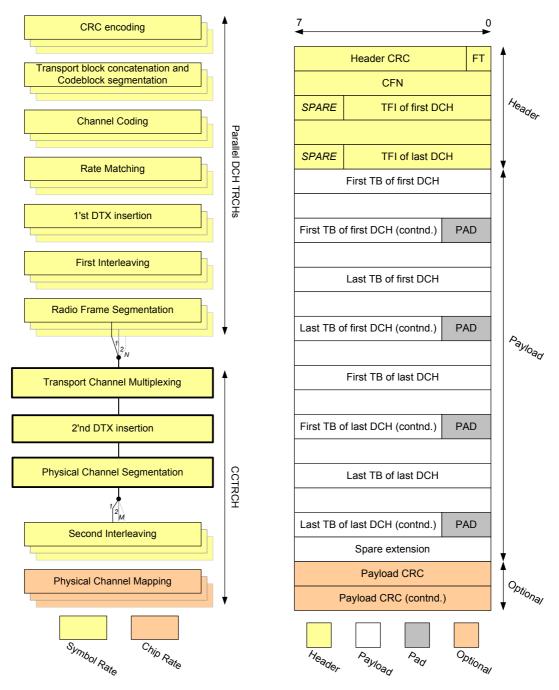

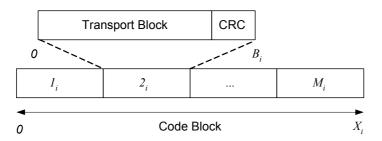

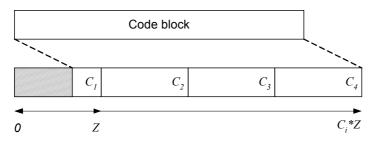

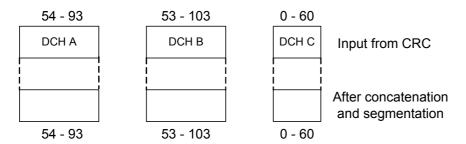

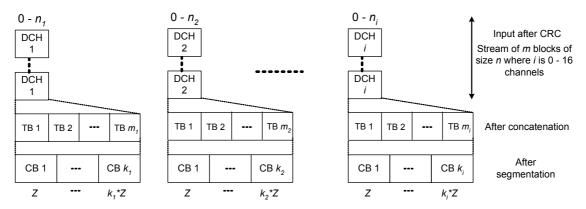

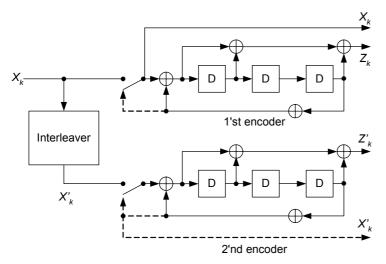

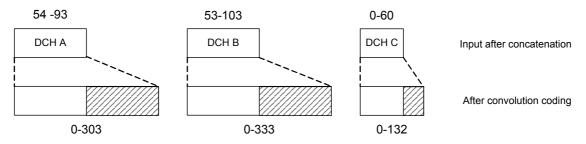

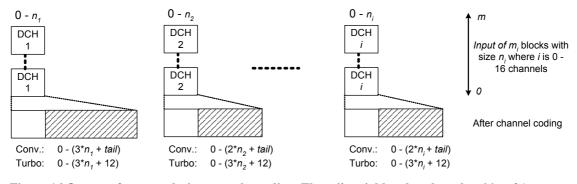

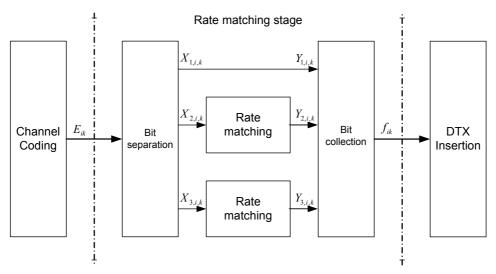

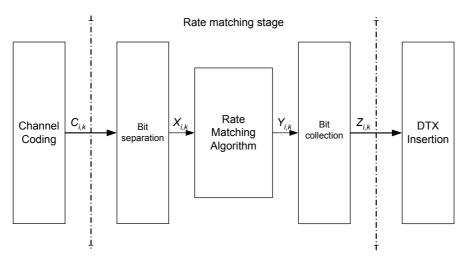

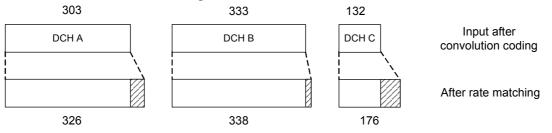

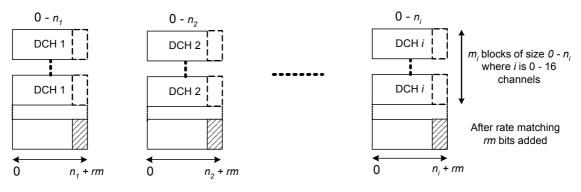

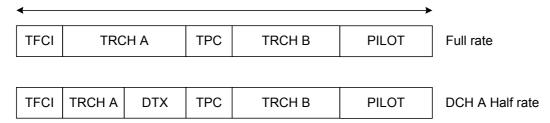

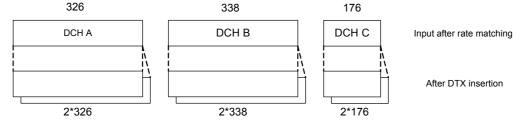

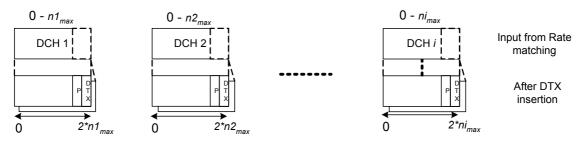

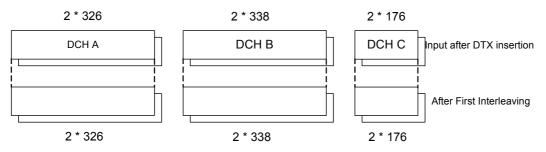

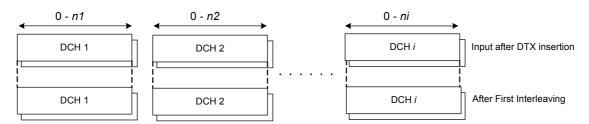

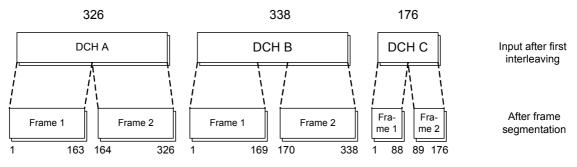

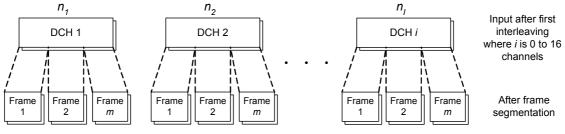

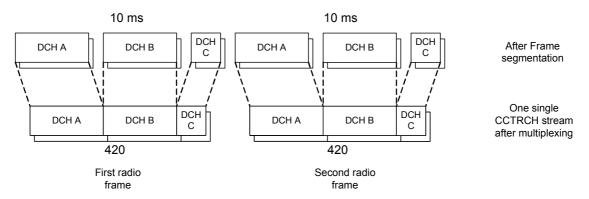

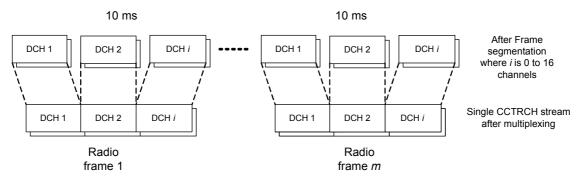

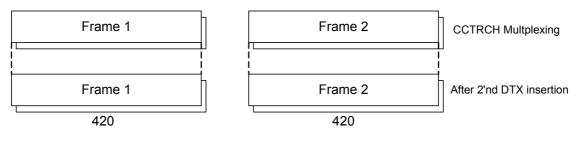

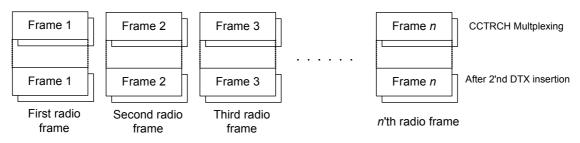

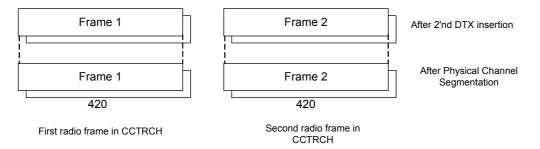

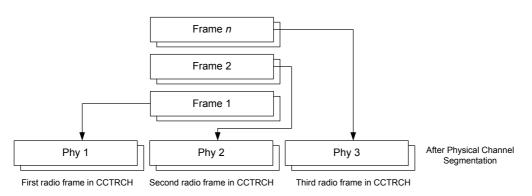

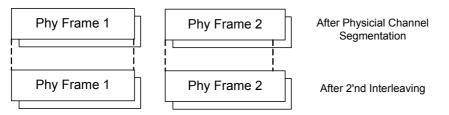

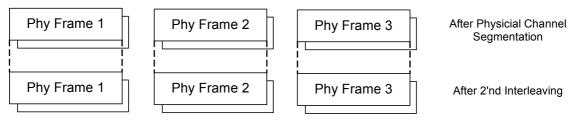

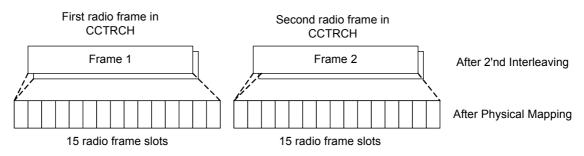

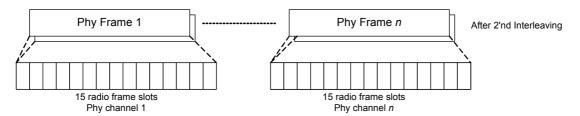

The baseband processing of the downlink in an RBS constitutes a pipelined function flow, see Figure 3.2. There are several types of transport channels: control, shared and dedicated user channels. The analysis in our study is limited to the processing of user dedicated transport channels (DCHTRCH). Furthermore, the processing is performed with different processing rates at different stages in the baseband: symbol rate and chip rate. Symbol rate corresponds to the rate of information bits, i.e. each information bit in the user data streams corresponds to one symbol. At the chip rate, each information bit (symbol) has been spread out on a longer code bit sequence. Our study covers only the symbol rate functions, i.e. we do not cover functionality such as code spreading, modulation and the radio.

## 3.2 Downlink processing analysis

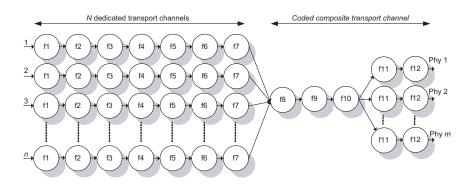

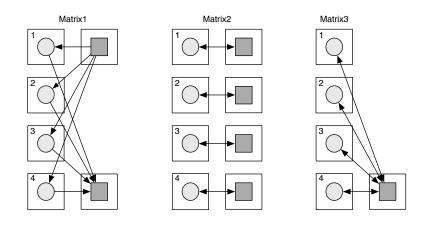

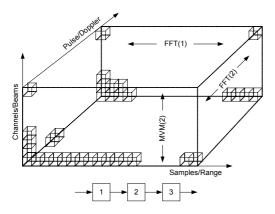

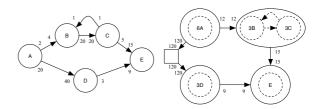

A single user can be allocated one or several dedicated transport channels (as illustrated by the 1 to n branches in the abstract task graph in Figure 3.2), depending on the type of service requested. In the mid stage in the graph, the user channels are multiplexed into a single composite transport channel (CC-TRCH). Then, depending on the required bandwidth, the composite channel is segmented and mapped on a number of physical channels (the 1 to m output branches in the figure). The structure of the task graph for each individual user is static during the service session.

Figure 3.2: Abstract task graph describing the symbol rate function flow in WCDMA downlink. The input of N user transport channels is multiplexed (at f8 in the figure) and mapped to M physical channels (at f10).

| ID  | Function                             |

|-----|--------------------------------------|

| f1  | Cyclic redundancy check (CRC)        |

| f2  | Block concatenation and segmentation |

| f3  | Channel coding                       |

| f4  | Rate matching                        |

| f5  | First DTX insertion                  |

| f6  | First interleaving                   |

| f7  | Frame segmentation                   |

| f8  | Channel multiplexing                 |

| f9  | Second DTX insertion                 |

| f10 | Physical channel segmentation        |

| f11 | Second interleaving                  |

| f12 | Physical channel mapping             |

Table 3.1: The table lists the types of downlink functions corresponding to the graph in Figure 3.2. These functions are described in [Paper B].

## 3.2.1 Types of parallelism

To avoid confusion about what we mean with certain types of logical parallelism in an application, we start by making a few definitions of such types. We refer to the abstract program implementing the downlink processing as the task graph. Nodes in the task graph correspond to functions, having a private address space, and edges represent the data dependencies between the functions (communication). The functions are considered to be infinitely repeated. We make the following definitions of logical program parallelism, using a function as the basic unit of computation:

**Task parallelism.** Two functions that are on separate branches in a task graph, in a way such that the output of one function never reaches the input of the other, are said to be *task parallel*.

**Data parallelism.** Any function that can be instantiated in multiple copies, such that no data dependency exists between the instances, is said to be *data parallel*.

**Pipeline parallelism.** Chains of functions having a producer consumer dependency are said to be *pipeline parallel*.

## **3.2.2** Real-time characteristics

An RBS is a real-time system. The correctness of the functionality is not only dependent on the logical correctness of its computations but also on at which point in time the system is able to consume and produce input and output data. In the case of an RBS, it means that certain processing requirements must be fulfilled to manage air and RNC interface compatabilities and to provide a certain level of quality-of-service.

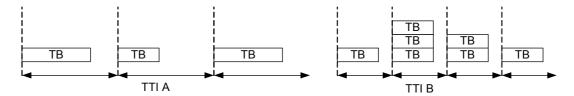

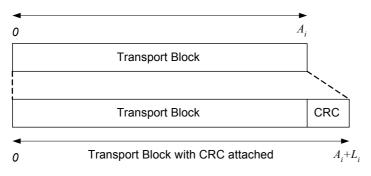

The system's input data rate is determined by the transmission time interval (TTI), see Figure 3.3 and the size and number of transport blocks carrying payload data. The output must be produced with respect to the given radio frame rate (10 ms in WCDMA), at which information is transmitted over the air. Services such as voice transmissions naturally put requirements on computation end-to-end latencies for user comfort. Furthermore, since re-transmission requests are handled by higher layers, there is naturally also a requirement on end-to-end computation latency, in order to meet a certain quality-of-service (effective bandwidth) for varying radio conditions.

**Remarks on the real-time aspects** Considering mapping of different task graphs on parallel hardware, we see a need to explore different parallel mapping strategies, allowing optimisation not only with respect to workload (number of concurrent users and services) but also with respect to the given timing requirements.

Figure 3.3: The transmission time interval (TTI) is always fixed during a transmission. For transmission of single transport blocks (TB), the length of transport blocks can be variable, as can be seen to the left in the figure. For transmission of transport block sets, all transport blocks must be of the same length, as can be seen to the right.

| Dynamic     | Transport block size       | 0-5000 bit                    |

|-------------|----------------------------|-------------------------------|

|             | Transport block set size   | 0-200000 bit                  |

| Semi-static | Transmission time interval | 10,20,40,80 ms.               |

|             | Channel coding type        | no coding, convolution, turbo |

|             | Code rates (convolution)   | 1/2  or  1/3                  |

|             | CRC size                   | 0,8,12,16,24                  |

Table 3.2: Transport format attribute options used to configure the baseband functions at the sender and the receiver.

## 3.2.3 Parameter configuration

The processing functions are individually configured using a set of transport format attributes. Table 3.2 shows these parameters. The dynamic attributes can be altered each TTI and are mainly used for configuring the functions to adjust to the current data to be processed. However, all transport blocks belonging to the same transport block set within the same TTI must be of the same size. We will make use of this information when discussing mapping of the logical parallelism on certain types of parallel hardware. The semi static attributes are configured once when setting up a service session. These parameters mainly configure the mode of functions and the TTI.

**Remarks on Parameter configuration** It is important to consider the configuration of parameters from at least two aspects. Firstly, considering a distributed software implementation on parallel hardware, there will be a need for a suitable representation of configuration data, and especially how to efficiently deal with distribution of the configuration data. Secondly, different configurations of functions in parallel transport channels indicate a limitation on certain data parallel hardware (SIMD).

## 3.2.4 Function level parallelism

When studying the abstract task graph for the downlink, as was shown in Figure 3.2, two types of coarse-grained parallelism are naturally exposed: task parallelism and pipeline parallelism. All data dependencies between functions are of the producer consumer type. The channel multiplexing function (node f8 in Figure 3.2) constitutes the first logical point of synchronisation in the downlink task graph. Before the multiplexing function, each branch of the graph (nodes f1 to f7) can be computed in a task parallel way, and the functions within each branch can be computed in a pipeline parallel way. The functions processing the composite transport channel (nodes f8 - f10) are pipeline parallel. After physical channel mapping (node f10), the functions (nodes f11-f12) can be mapped task parallel (if several physical channels are used) and pipeline parallel within each physical channel flow.

**Remarks on task and pipeline parallelism** On an abstract level, both potential task and pipeline parallelism are naturally exposed. To further determine potential data parallel mappings of the downlink task graph, it is necessary also to analyse intra-function data dependencies.

### **3.2.5** Intra function characteristics

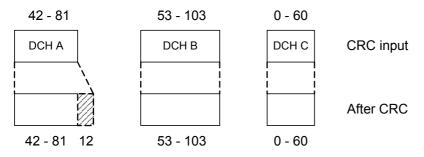

In our analysis we mainly consider logical parallelism exposed in the specification of the standard. To examine potential intra algorithm parallelism, we need to analyse the computation characteristics of the standardised processing functions. For a more detailed analysis of the functions, the reader is referred to [Paper B]. Here we give a short summary of the characteristics.

**Data dependencies** The data streaming through the functions have the form of logically serial streams of binary information symbols. The functions specified for the downlink functions are therefore, to a large extent, performing bit serial computations. This means that there is in general no obvious fine-grained data parallelism exposed within the algorithms. However, most of the functions allow bit parallel mapping and computation of the data using word length data types. None of the symbol rate functions has data dependencies between iterations, i.e. between the processing of consecutive TTIs. This means that most of the task parallel functions in the downlink computation graph potentially also, from a logical point of view, are data parallel.

**Instruction level computations** The computations on the data are primarily of a logical nature. The functions performing different kinds of data coding, such as CRC, convolution and turbo coding, are dominated by logical arithmetic and shift operations. Computing such functions bit serially using bit parallel hardware is not an efficient usage of the hardware. Therefore, software implemented solution of such algorithms typically make use of pre-calculated look-up tables whenever possible. Bit serial calculations are thus transformed to bit parallel masking and memory reads and writes. Other functions mainly reshape the block representations of the data streams, for example the block concatenation and the segmentation functions. Further, another category is the interleaving and rate matching functions, where data are either scrambled or modified on a bit level basis.

**Remarks about intra function characteristics** We have studied the downlink computation graph from a logical point of view, given by the 3GPP specifications. We conclude that logical parallelism is dominates a on function level. On the intra function level, performance gain is related more to an acceleration of computations. However, a thorough analysis of opportunities for instruction parallel computations requires implementation studies of the complete task graph.

#### 3.2.6 3G service use cases

We selected two service use cases (given by the 3GPP standard) that have different processing requirements on the baseband: one service configuration for voice transmission and the other for arbitrarily high bit rate data transmissions. These use cases are used to analyse the processing characteristics of the downlink functions.

Adaptive Multi Rate voice transmission Adaptive multi rate (AMR) is the technique for the coding and decoding of dynamic rate voice data included in the UMTS<sup>2</sup>. This technique allows dynamic alternations of the bit rate for voice transmissions during the service session. The output of the AMR encoder is arranged in three classes of bit streams (A,B and C), depending on how important specific bits are for quality. The A bits are the most important and the C bits are the least important. In this use case, each of the three bit stream classes is mapped on its own dedicated user transport channel. The output stream is mapped on a single physical channel.

**High bit rate data transmission** The 3GPP standard specifies a set of user equipment (UE) classes with different radio access capabilities<sup>3</sup>. These capability classes define the data rates and services that must be supported for a UE of a certain class. We used the requirements for the highest capability

$<sup>^2{\</sup>rm Technical}$  Specification Group Radio Access Network; Services provided the physical layer, TS 25.302 (Release 5), www.3gpp.org

$<sup>^3{\</sup>rm Technical}$  Specification Group Radio Access Network; UE Radio Access capabilities, TS 25.306 (Release 5), www.3gpp.org

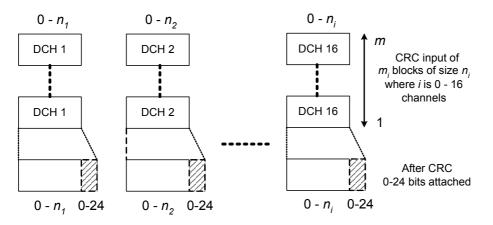

class supporting bit rates up to 2048 kbps<sup>4</sup>. In this use case, the input is mapped on 16 user transport channels (maximum in this UE class) and the output is mapped on 3 (maximum) physical channels.

### 3.2.7 Mapping study of the use cases

In [Paper B] we discuss mapping of the service use-cases on different types of common parallel hardware. We studied how the services are mapped on transport channels and what the required parameter configurations are for the two use cases. Function by function, we reason about possibilities and complications for exploiting hardware supported SIMD and MIMD processing when mapping the downlink task graphs for each service.

**SIMD mapping** One possible mapping option we have studied is to logically group multiple transport channels (which are logically task parallel) to be computed using data parallel hardware. Thus we use one single instruction stream for processing n transport channels, where the user data are partitioned, mapped and computed on an n-words wide SIMD unit.

Efficient SIMD processing of multiple user channels requires that the channels are uniformly configured and that the transport blocks are of equal size. For the AMR use case, this is unfortunately not the case. The transport blocks mapped on their respective transport channels are not of equal length. To compute the bit streams on word length hardware, the algorithm control flow naturally becomes dependent on the length of the transport blocks (recall that many of the functions logically compute bit serially). In the AMR case, the algorithm control flow becomes asymmetric. Another complication is that different CRC polynomials and convolution coding rates are used for each of the three channels.

For the high bit rate data service, the transport blocks are of equal size. Furthermore, the configuration parameters for all transport channels can be configured equally. However, SIMD mapping on a transport channel basis still introduces complications for this use case as well. For example, algorithms based on look-up table techniques need to be serialised (for example, the CRC and the coding functions).

In conclusion, SIMD parallel computation on a task/data parallel user transport channel basis introduces many complications. However, it is an open question whether certain functions for certain services could be beneficially (in terms of performance gain) SIMD computed. Implementation studies on a lower level will be required to answer this question.

$<sup>^4\</sup>mathrm{The}$  later addition of HSDPA and HSUPA to the 3G standard allows higher bit-rates.

**MIMD mapping** A MIMD processor enables asynchronous parallel computations of task, data and pipeline parallelism. The trade-off, compared to a SIMD parallel mapping, is a higher cost for parallel synchronisation and communication (moving the data between cores) at certain points in a program. The downlink task graph naturally constitutes a good match with MIMD hardware.

Considering parallel implementation of WCDMA baseband processing on a MIMD structure, there are many interesting issues related to the synchronisation of parallel computations and function configuration. First of all, how do we handle the synchronisation of functions processing different TTIs of data and how do we handle synchronised of distribution configuration parameters?

## 3.3 Summary and implications

This chapter provided a summary of our analysis of the WCDMA downlink processing in third generation wireless telecommunication systems [Paper B]. We have discussed different types of logical parallelism exposed in the WCDMA downlink symbol rate functions. The computations are primarily of a logical nature rather than of an arithmetical nature, further motivating expressing computations on variably sized bit streams of data. We have discussed possibilities and complications related to application mapping on certain types of common parallel hardware. Further, we find it motivated to investigate expressions of computations on SIMD parallel and bit level computations. For this application domain, it should be possible to express computations on variable bit fields of data as well as data parallelism on the word length of data. Real-time applications, such as the 3G baseband, require task graph mapping strategies with respect to non-functional properties such as computational timing constraints. Chapter 4

# STREAMING MODELS OF COMPUTATION

This chapter introduces streaming models of computation, and we describe the synchronous dataflow model of computation in particular. We motivate the focus on the synchronous dataflow model of computation with respect to the baseband study discussed in Chapter 3 and with respect to the type of manycore architectures we are investigating. Finally, we briefly describe the work presented in [Paper C], where we provide a small modelling framework for elaborating with domain specific SDF languages.

## 4.1 Introduction

A paradigm shift from centralised processor architectures to manycore architectures will naturally also require a paradigm shift in programming models, languages, compilers and development tools. Programs must be concurrent and malleable for highly parallel and communication exposed hardware interfaces of manycores. Sequential languages conventionally used in the embedded systems industry, such as C, and especially the supporting compiler technology, have been developed for sequential processor architectures exposing a global memory space. Especially considering non-coherent distributed memory manycores, C does not offer a suitable means for expressing concurrency and other knowledge that is important for such a machine target. Important parallel information present in the applications many times must be pruned and it is often not possible to automatically recover such knowledge.

The conventional way of describing concurrency in C programs is to use threads, which are sequential processes logically sharing memory. Relying on threads as a concurrent programming model for code generation to manycore processors is a bad approach for at least two reasons: 1) threads provide an illusion of a shared memory space, which becomes very complex and expensive to resolve when mapped to a distributed memory processor and 2) threads are highly non-deterministic in their nature [Lee, 2006]). A reliable and predictable implementation using threads is relying on programming style and well-defined thread overlay mechanisms, such as semaphores, locks, barriers etc. For automatised mapping to a manycore target, such a source constitutes a statespace that is highly complex to analyse (perhaps many times even impossible), in order to realistically predict its runtime behaviour.

#### 4.1.1 Domain specific programming solutions

We argue that domain specific development methods and tools will be needed to achieve development efficiency for manycore technology. The structure of computations and processing requirements is often quite different for different applications.