## **CHALMERS**

### **Chalmers Publication Library**

An array of 100 Al-Al2O3-CuSIN tunnel junctions in direct-write trilayer technology

This document has been downloaded from Chalmers Publication Library (CPL). It is the author's version of a work that was accepted for publication in:

Superconductor Science & Technology (ISSN: 0953-2048)

#### Citation for the published paper:

Otto, E.; Tarasov, M.; Pettersson, G. (2007) "An array of 100 Al-Al2O3-CuSIN tunnel junctions in direct-write trilayer technology". Superconductor Science & Technology, vol. 20(12), pp. 1155-1158.

http://dx.doi.org/10.1088/0953-2048/20/12/012

Downloaded from: http://publications.lib.chalmers.se/publication/82199

Notice: Changes introduced as a result of publishing processes such as copy-editing and formatting may not be reflected in this document. For a definitive version of this work, please refer to the published source. Please note that access to the published version might require a subscription.

Chalmers Publication Library (CPL) offers the possibility of retrieving research publications produced at Chalmers University of Technology. It covers all types of publications: articles, dissertations, licentiate theses, masters theses, conference papers, reports etc. Since 2006 it is the official tool for Chalmers official publication statistics. To ensure that Chalmers research results are disseminated as widely as possible, an Open Access Policy has been adopted. The CPL service is administrated and maintained by Chalmers Library.

# An array of 100 Al–Al<sub>2</sub>O<sub>3</sub>–Cu SIN tunnel junctions in direct-write trilayer technology

## Ernst Otto, Mikhail Tarasov, Gustav Pettersson, David Gustavsson and Leonid Kuzmin

Department of Microtechnology and Nanoscience, Chalmers University of Technology, SE-41296 Göteborg, Sweden

E-mail: ernst.otto@mc2.chalmers.se

Received 15 June 2007, in final form 3 September 2007 Published 28 September 2007 Online at stacks.iop.org/SUST/20/1155

#### **Abstract**

We present superconductor–insulator–normal metal (SIN) tunnel junction thermometers made of arrays of  $4{\text -}100~\text{Al-Al}_2\text{O}_3$ –Cu SIN tunnel junctions fabricated in direct-write technology. The technology is based on *in situ* evaporation of the superconductive electrode followed by the oxidation and the normal counter-electrode as a first step and deposition of normal metal absorber as a second one.

This approach allows one to realize any geometry of the tunnel junctions and of the absorber with no limitation related to the size of the junctions or the absorber, which is not possible using the shadow evaporation technique.

Measurements performed at 300 mK showed the high quality of the fabricated tunnel junctions, low leakage currents, and that an  $R_{\rm d}/R_{\rm n}$  ratio of 500 has been achieved at that temperature.

The junctions were characterized as temperature sensors, and voltage versus temperature dependence measurements showed a dV/dT of 0.5 mV  $K^{-1}$  for each single junction, which is typical for this kind of tunnel junction. A temperature resolution of  $\pm 5~\mu K$  has been achieved which is much better than the previously reported value of  $\pm 30~\mu K$  for this type of thermometer.

#### 1. Introduction

A tunnel junction between a superconductor and normal metal or superconductor–insulator–normal metal (SIN) tunnel junction can be used for temperature measurements and detection of microwave radiation [1]. Both applications are based on the dependence of current–voltage characteristics of the SIN junction on the temperature [2, 3].

SIN tunnel junctions have traditionally been manufactured using the so-called shadow evaporation technique based on one-cycle deposition of both the superconducting electrode and the normal metal absorber. This technique has, of course, certain advantages and has therefore been used for years for SIN tunnel junction fabrication, especially in the laboratory and academic environments as it does not involve too advanced equipment. However, it is not the most appropriate technique

for thermometry application and it has many drawbacks and limitations.

First of all, the main limitation is related to the size of tunnel junctions which cannot be made as large as required due to the principle of shadow evaporation. This makes the shadow evaporation technique very useful for single-electronics where small size of tunnel junctions is advantageous. But for bolometer fabrication this approach can only be used within certain frequency ranges. Second, geometry considerations impose severe limitations on the layout and orientation of the structures on the chip. And, finally, this technique does not allow for use of magnetron sputtering which is commonly used for manufacturing of high quality tunnel junctions.

The motivation of our work was the necessity of developing a direct-write technology [4] for manufacturing Albased SIN tunnel junctions operating at 100–300 mK, which is

the temperature range in which the bolometer operation is most efficient in terms of responsivity (dV/dP) and sensitivity (low noise).

This technology allows us to manufacture SIN tunnel junctions for microwave detectors and cryogenic thermometers. In this technology, the deposition procedure and direct writing of both the superconductive layer and the absorber do not impose any requirements on the deposition of both layers in one vacuum cycle of evaporation. That simplicity of the technology gives us additional freedom in realizing any possible layouts in any geometry [4].

Currently, SIN junctions made in this technology are used for temperature measurement, which is also a part of bolometer operation [5, 6]. For example, the samples have been used for temperature stability measurements in a Heliox cryogenfree cryostat recently fabricated by the company Oxford Instruments.

The high accuracy, high speed of operation and wide temperature range of SIN thermometers make them very attractive for future utilization [2], e.g. for the temperature control inside the cryostats.

#### 2. Fabrication

Both the trilayer structure and the normal metal absorber were patterned by lithography followed by deposition and lift-off. As a final step, parts of the gold and normal metal covering the trilayer structure were removed by ion-beam etching [4].

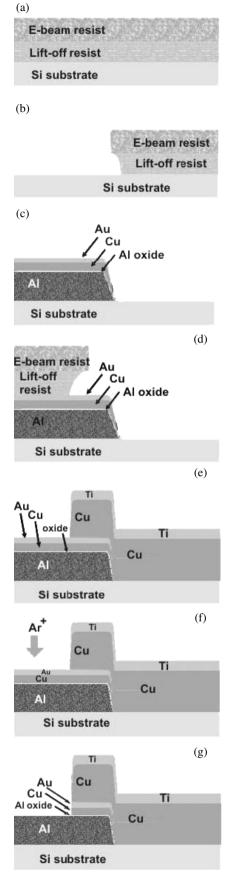

In each step of lithography, two resist layers were used in order to make the lift-off easier and to avoid any contact of deposited materials with the resist. The bottom resist layer is developed a bit more than the top one and in some cases overexposed, which results in slightly wider open windows in the bottom layer than in the top one, or so-called undercut (figure 1(b)). The deposited materials are only touching the top resist layer during the evaporation and are therefore patterned after the outline in the top resist layer. After deposition, the materials are not touching either resist layer. This allows avoiding uncertainty on edges of deposited materials which may arise due to probable contact with the resist when using only one resist layer. This is especially important for Al because it is oxidized after the deposition and any contact with the resist would introduce some uncertainty in the oxidation conditions. Al is deposited by thermal evaporation for lift-off, and in that case the edges are not very sharp, making an angle with the substrate close to  $50^{\circ}$ – $60^{\circ}$  (depending on the distance between the source of material and the sample). In this case we believe that oxidation on the edges will occur in a more or less similar way for flat regions of Al. However, we are planning to avoid open edges during oxidation of Al in the future. This will require one more layer of lithography to protect the edges from oxidation.

#### 2.1. Detailed description of the technology

A silicon wafer, oxidized thermally to obtain 400 nm oxide thickness, was covered by a lift-off layer and a photoresist and then baked. Then, contact pads were patterned by a standard process of photolithography and thermal evaporation followed by the lift-off.

Figure 1. Fabrication procedure.

**Figure 2.** Optical images of SIN junctions: (a) two  $4 \times 4 \mu \text{m}^2$  junctions; (b) two  $2 \times 2 \mu \text{m}^2$  junctions.

For patterning the superconductive electrode, a lift-off resist and e-beam resist were spun over the wafer (figure 1(a)), exposed in the e-beam lithography system, and developed (figure 1(b)). Then an Al layer was deposited at a pressure of  $4 \times 10^{-7}$  mbar and oxidized for 2 min in oxygen ambient at  $5 \times 10^{-2}$  mbar to create the tunnel junction. Then Cu was evaporated as a normal metal electrode of a tunnel junction and covered by Au for passivation (figure 1(c)).

Next, the normal metal Cu absorber was patterned by ebeam lithography and thermal evaporation (figures 1 (d) and (e)).

Finally, argon ion-beam etching was used to remove Cu and Au from the top of the trilayer structure; see figures 1(f) and (g).

The optical images of the final structures are shown in figure 2.

#### 3. Sample characterization

Arrays of 4, 10, 30, and 100 junctions of  $2 \times 2$  and  $4 \times 4 \mu m^2$  have been fabricated and tested at temperatures down to 300  $\mu$ K. It has already been shown [5] that using 10 junctions in series gives us temperature sensitivity much better than that for one single junction. In that work, an array of ten SIN junctions was fabricated using the shadow evaporation technique and characterized. The resolution in temperature of  $\pm 30 \ \mu$ K was achieved, and it was shown that this resolution is mainly determined by the noise of the amplifier in the read-out system. For an array of ten junctions, it was not

**Figure 3.** I-V curves of arrays of 30 (a) and 100 (b) SIN junctions at 305  $\mu$ K.

possible to measure the noise of the junctions as it does not exceed the noise of the amplifier. Therefore, increasing the number of the junctions, one can measure the noise of the junctions as soon as it exceeds the noise of the amplifiers. It has also been shown [3, 5] that the voltage drop across the array is proportional to the number of junctions, whereas the total voltage noise is linear in the square root of the number of junctions. Therefore, further increase of the number of junctions in series will allow us to achieve even higher sensitivity, which is fully confirmed in our work by measurements on the samples containing arrays of different numbers of SIN junctions up to 100. The noise of an array of 100 junctions can easily be distinguished from the noise of the read-out system, and one can estimate the temperature sensitivity of the thermometer.

Both the dynamic resistance at zero voltage  $R_{\rm d}$  and the normal resistance  $R_{\rm n}$  have been measured, and the ratio  $R_{\rm d}/R_{\rm n}$  is estimated as a measure of quality of the tunnel junctions. Measurements showed high quality of fabricated tunnel junctions, low leakage currents, and an  $R_{\rm d}/R_{\rm n}$  ratio of 500 achieved at 300 mK. I-V curves of arrays of 30 and 100 junctions are shown in figure 3.

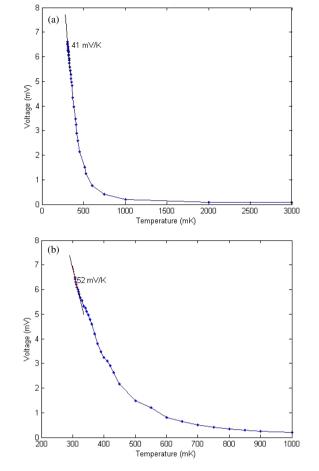

The voltage versus temperature dependence has also been measured, and a dV/dT of 52 mV K $^{-1}$  has been achieved for 100 junctions of 2 × 2  $\mu$ m $^2$  in series, which corresponds to 0.52 mV K $^{-1}$  for each junction (figure 4(b)).

**Figure 4.** Voltage versus temperature dependence for 100 junctions of  $4 \times 4 \ \mu \text{m}^2$  and  $2 \times 2 \ \mu \text{m}^2$  area.

The corresponding figure for larger junctions is  $40 \text{ mV K}^{-1}$  (figure 4(a)) due to higher leakage currents for larger junctions.

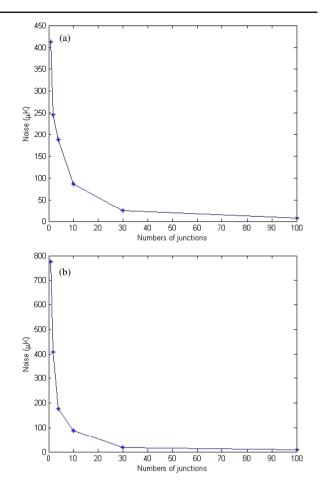

For an array of 100 junctions a temperature resolution of  $\pm 5~\mu \rm K$  has been achieved which is much better than the previously reported result of  $\pm 30~\mu \rm K$  [5]. The temperature resolution versus number of junctions is shown in figure 5. Increasing the number of junctions in series will allow us to achieve even higher sensitivity [3, 5], which enables use of SIN tunnel junctions fabricated in direct-write technology for thermometry application.

#### 4. Conclusions

We have developed an advanced process for fabrication of SIN tunnel junctions and fabricated SIN thermometers made of arrays of up to 100 junctions. The fabricated tunnel junctions show typical properties of SIN tunnel junctions with small leakage currents, and the measured voltage versus temperature dependence corresponds to a typical behavior of this kind of tunnel junction. The resolution in temperature of  $\pm 5~\mu \rm K$  has been achieved.

We have confirmed experimentally the theoretical assumption that increasing the number of junction in series allows us to achieve higher sensitivity, which enables the use of SIN tunnel

**Figure 5.** Temperature resolution versus number of junctions for arrays of up to 100 junctions of  $2 \times 2 \mu m^2$  (a) and  $4 \times 4 \mu m^2$  (b).

junctions fabricated in this technology for thermometry application.

#### Acknowledgments

This work was supported by the Swedish Space Agency and the Swedish Research Council. Sponsorship from The Royal Society of Arts and Sciences in Göteborg (Kungl. Vetenskaps- och Vitterhets-Samhället i Göteborg–KVVS) and the foundation Innovationsbron Väst AB is also acknowledged.

We are especially grateful to Vladimir Mikheev and Simon Mitchinson, Oxford Instruments, for supporting our development work.

#### References

- [1] Solymar L 1972 Superconductive Tunneling and Applications (London: Chapman and Hall)

- [2] Pekola J 2004 Trends in thermometry *J. Low Temp. Phys.*

- [3] Kuzmin L 2007 Ultra-sensitive cryogenic thermometer based on an array of the SIN tunnel junctions *Phys. Lett.* A submitted

- [4] Otto E, Tarasov M and Kuzmin L 2007 Direct-write trilayer technology for Al-Al<sub>2</sub>O<sub>3</sub>-Cu SIN tunnel junction fabrication J. Vac. Sci. Technol. B 25 1156-60

- [5] Agulo I J and Kuzmin L 2007 An array of SIN tunnel junctions as a sensitive thermometer Supercond. Sci. Technol. submitted

- [6] Kuzmin L 2004 Ultimate cold-electron bolometer with strong electrothermal feedback *Proc. SPIE* 5498 349–61