### THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## CARBON BASED MATERIALS SYNTHESIS AND CHARACTERIZATION FOR 3D INTEGRATED ELECTRONICS

SHUANGXI SUN

Department of Microtechnology and Nanoscience (MC2)

Chalmers University of Technology

Göteborg, Sweden 2017

## Carbon Based Materials synthesis and characterization for 3D Integrated Electronics Shuangxi Sun

ISBN: 978-91-7597-577-1

Copyright © Shuangxi Sun 2017

Doktorsavhandlingar vid Chalmers tekniska högskola

Ny serie nr 4258

ISSN 0346-718X

Chalmers University of Technology

Department of Microtechnology and Nanoscience (MC2)

Electronics Material and Systems Laboratory

SE-412 96 Göteborg, Sweden

Phone: +46 (0) 31 772 1000

ISSN 1652-0769

Technical Report MC2-361

## **Abstract**

3D IC packaging technology extends Moore's law and shifts the IC field into a new generation of smaller, but more powerful devices. Interconnection and thermal management as two critical parts of 3D IC integration packaging, are facing harsh challenges due to the miniaturization of IC devices. This thesis focuses on improving the heat dissipation effect and interconnect performance for 3D IC integration packaging by developing carbon based nanomaterials.

Thermal management has been identified by the semiconductor industry as one of the major technological bottlenecks to hinder the further miniaturization of 3D IC devices, particularly in high power devices. The first part of thesis presents a comprehensive thermal management solution including nanocomposite thermal interface material (Nano-TIM), hexagonal boron nitride (hBN) heat spreader and graphene-CNT (G-CNT) hybrid heatsink to address heat issue existing in high power IC devices. To decrease the thermal interface resistance, a smart Nano-TIM is developed through combining a silver-coated nanofiber network and an indium matrix. The matrix contributes to the heat conduction, while the nanofiber network defines the geometry and improves the mechanical performance. The thermal and mechanical performance of Nano-TIM is demonstrated in die attach applications in IC packaging. In addition to improve thermal interface resistance by Nano-TIM, an hBN heat spreader was synthesized by liquid exfoliation method to spread and dilute the heat energy generated in power chip for further cooling. This spreader potentially broadened the heat spreader application scenario in IC packaging due to its insulating performance. Moreover, in order to dissipate heat energy from IC microsystem, a 3D carbon based heat sink consisted of CNTs and graphene was synthesized using CVD method. The carbon based heat sink combining 1D CNTs with 2D graphene extended the excellent thermal property to three dimensions through covalent bonding.

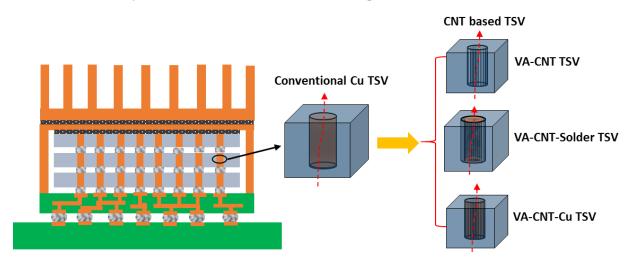

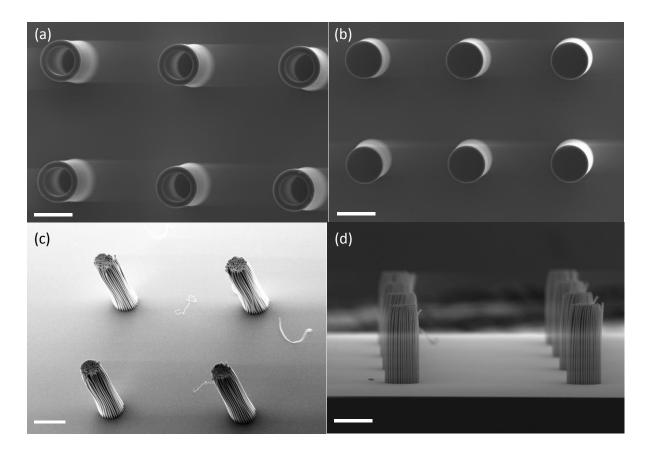

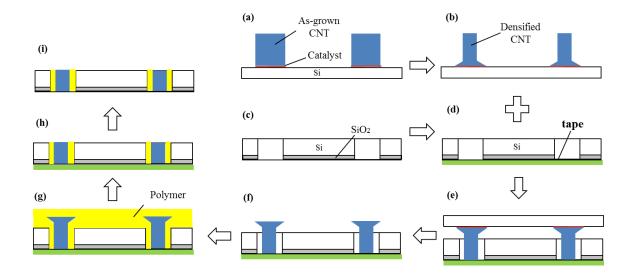

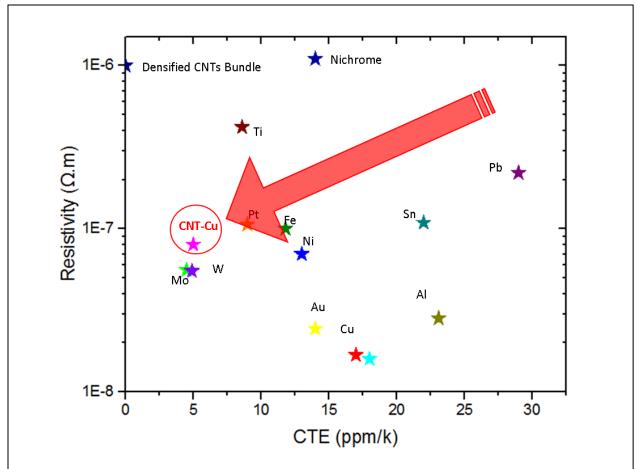

In the second part of thesis, it is devoted to the development of CNT-based through silicon vias (TSVs) for interconnects in 3D IC packaging. Vertically aligned carbon nanotubes (VA-CNTs) with different structures were synthesized by the thermal chemical vapor deposition (TCVD) method. In order to address the incompatibility with IC manufacturing processes and relatively lower electrical conductivity than metal, a series of processes including tape assisted transfer, filling solder balls into hollow structures and electroplating Cu into CNTs bundles were developed. Accordingly, different types of CNT-based TSVs were fabricated: densified VA-CNT TSV, VA-CNT-Solder TSV and VA-CNT-Cu TSV. The electrical conductivity performance of the TSVs was measured using the four-probe method. Among these different kinds of TSVs, VA-CNT-Cu TSV exhibits the best conductivity, around the same order of magnitude as copper. Meanwhile, the CTE of this kind of TSV is as low as that of silicon substrate, which can effectively decrease thermal stress of the interface between via and substrate. In addition, to broaden the TSV application scenario, a flexible CNT interconnect system was integrated to demonstrate potential carbon based application in future wearable microelectronics.

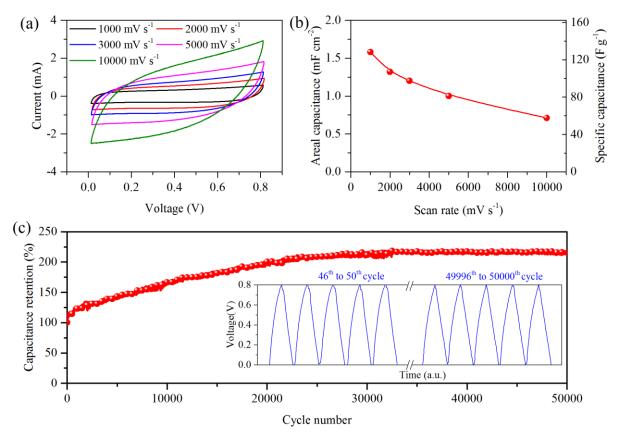

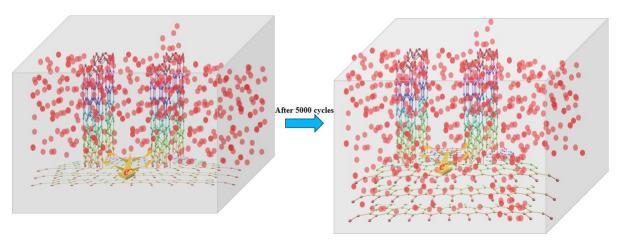

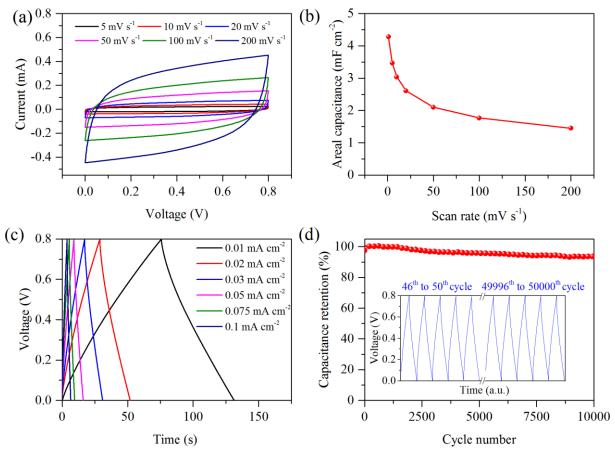

In addition, CNT-G material was developed for carbon based supercapacitors application, thanks to the huge surface area and high electrical conductivity of the CNT-G hybrid material. The results indicate a superior rate capability of the CNT-G material. This carbon hybrid material exhibited a great promise for supercapacitor applications particularly in high current density.

In summary, integrating the Nano-TIM, heat spreader and G-CNT heatsink together offered a comprehensive thermal management solution for 3D IC microsystem using carbon based materials. Carbon based TSV technology further shortens interconnection path and enhanced 3D IC integration. To some extent, these findings offer a potential solution for the further miniaturization of 3D IC microsystem.

Keywords: TIM, VA-CNTs, VA-CNT-Cu, VA-CNT-Solder, TSV, G-CNT, 3D IC integration, thermal resistance, electrical resistivity, graphene.

## List of appended papers

#### Paper A

## Mechanical and thermal characterization of a novel nanocomposite thermal interface material for electronic packaging

Shuangxi Sun, Si Chen, Xin Luo, Yifeng Fu, Lilei Ye, Johan Liu

Microelectronic Reliability, published online 4<sup>th</sup> November 2015. DOI: 10.1016/j.microrel.2015.10.028

#### Paper B

#### Tape-assisted transfer of carbon nanotube bundles for through-silicon-via applications

Wei Mu, Shuangxi Sun, Di Jiang, Yifeng Fu, Michael Edwards, Yong Zhang, Kjell Jeppson, Johan Liu *Journal of Electronic Materials, published online 17<sup>th</sup> April 2015. DOI: 10.1007/s11664-015-3752-2*

### Paper C

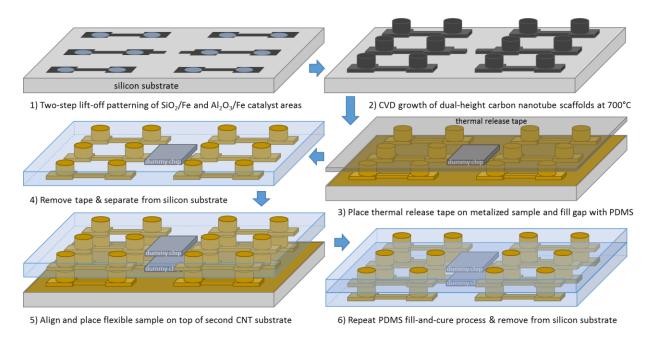

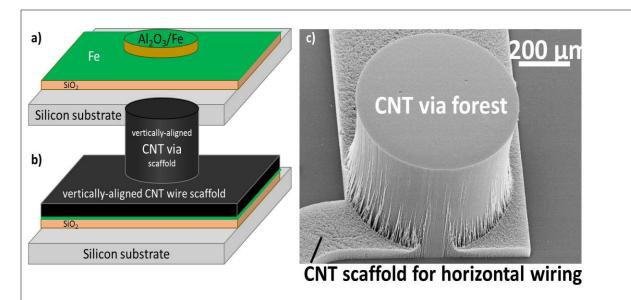

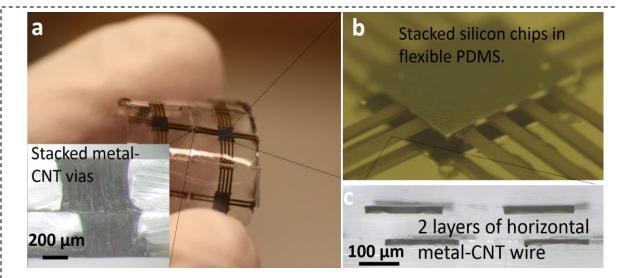

## A Flexible and Stackable 3D Interconnect System using Growth-Engineered Carbon Nanotube Scaffolds

Di Jiang, Shuangxi Sun, M. Edwards, K. Jeppson, Nan Wang, Yifeng Fu, Johan Liu *Flex. Print. Electron, Published online 2017, doi.org/10.1088/2058-8585/aa6a82*

#### Paper D

### A vertically-aligned CNT-Cu nanocomposite material for through-silicon-via interconnects

Shuangxi Sun, Wei Mu, Michael Edwards, Davide Mencarelli, Luca Pierantoni, Yifeng Fu, Kjell Jeppson, Johan Liu

Nanotechnology, vol. 27, no. 33, p. 335705, 2016

#### Paper E

#### Cooling hot spots by hexagonal boron nitride heat spreaders

Shuangxi Sun, Jie Bao, Wei Mu, Yong Zhang, Yifeng Fu, Lilei Ye, Johan Liu

The Proceeding - Electronic Components and Technology Conference, 2015, vol. 2015–July, pp. 1658–1663.

#### Paper F

## Controllable and fast synthesis of bilayer graphene by chemical vapor deposition on copper foil using a cold wall reactor

Wei Mu, Yifeng Fu, Shuangxi Sun, Michael Edwards, Lilei Ye, Kjell Jeppson, Johan Liu *Chem. Eng. J.*, vol. 304, pp. 106–114, Nov. 2016.

#### Paper G

#### Covalent bonding improved thermal transport at CNT-graphene interface

Shuangxi Sun, K. Majid Samani, Yifeng Fu, Tao Xu, Lilei Ye, Maulik Satwara, Kjell Jeppson, Torbjörn Nilsson, Litao Sun, Johan Liu

*Under review by ACS Appl. Mater. Interface, May.* 2017.

#### Paper H

#### A seamless CNT and graphene hybrid supercapacitor

Shuangxi Sun, Qi Li(Equal first author), Yifeng Fu, Per Lundgren, Peng Su, Peter Enoksson, Johan Liu *In Manuscript*, 2017.

Other contributions that are not included in the discussion due to being out of the scope of this thesis

- O. Cometto, Majid K. Samani, Bo Liu, Shuangxi Sun, Siu Hon Tsang, Johan Liu, Kun Zhao, Edwin H.T. Teo, "Control of Nanoplane Orientation in voBN for High Thermal Anisotropy in a Dielectric Thin Film: A New Solution for Thermal Hotspot Mitigation in Electronics," ACS Appl. Mater. Interfaces, vol. 9, no. 8, pp. 7456–7464, Mar. 2017.

- J. Daon, S. Sun, D. Jiang, G. Cibien, E. Leveugle, C. Galindo, A. Ziaei, L. Ye, Y. Fu, J. Bai, and J. Liu, "Electrically conductive thermal interface materials based on vertically aligned carbon nanotubes mats," in 2014 20th International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), 2014, pp. 1–4.

- J. Daon, S. Sun, D. Jiang, E. Leveugle, C. Galindo, S. Jus, A. Ziaei, L. Ye, Y. Fu, J. Liu, and J. Bai, "Chemically enhanced carbon nanotubes based Thermal Interface Materials," presented at the THERMINIC 2015 21th International Workshop on Thermal Investigations of ICs and Systems, Proceedings, 2015.

- 4 K Jeppson, J Bao, S Huang, Y Zhang, S Sun, Y Fu, J Liu, "Hotspot test structures for evaluating carbon nanotube microfin coolers and graphene-like heat spreaders," presented at the IEEE International Conference on Microelectronic Test Structures, 2016, vol. 2016–May, pp. 32–36.

- 5 Yong Zhang, Shirong Huang, Nan Wang, Jie Bao, Shuangxi Sun, Michael Edwards, Xuan Fu, Wang Yue, Xiuzhen Lu, Yan Zhang, Zhichao Yuan, Haoxue Han, Sebastian Volz, Yifeng Fu, Lilei Ye, Kjell Jeppson, Johan Liu, 2D heat dissipation materials for microelectronics cooling applications," presented at the China Semiconductor Technology International Conference, CSTIC, 2016.

- 6 Di Jiang, Shuangxi Sun, Wei Mu, Yifeng Fu, Johan Liu "Carbon nanotube/solder hybrid structure for interconnect applications," presented at the Proceedings of the 5th Electronics System-Integration Technology Conference, ESTC 2014, 2014.

- 7 Y. Fu, W. Mu, S. Sun, N. Wang, S. Huang, and J. Liu, "Post-growth processing of carbon nanotubes for interconnect applications a review," in 2016 6th Electronic System-Integration Technology Conference (ESTC), 2016, pp. 1–6.

- 8 Dongsheng Zhang, Jiawen Liu, Shuangxi Sun, Shirong Huang, Jie Bao, Ning Wang, Johan Liu, Xiuzhen Lu, "Thermal properties of TIM using CNTs forest in electronics packaging," presented at the 2016 17th International Conference on Electronic Packaging Technology, ICEPT 2016, 2016, pp. 1355–1359.

- 9 Wei Mu, Josef Hansson, Shuangxi Sun, Michael Edwards, Yifeng Fu, Kjell Jeppson, Johan Liu "Double-Densified Vertically Aligned Carbon Nanotube Bundles for Application in 3D Integration High Aspect Ratio TSV Interconnects," presented at the Proceedings - Electronic Components and Technology Conference, 2016, vol. 2016–August, pp. 211–216.

## Abbreviations

CNT Carbon nanotube

CTE Coefficient of thermal expansion

CVD Chemical vapor deposition

DRIE Deep reactive ion etching

EDX Energy dispersive X-ray spectroscopy

ENIG Electroless nickel immersion gold

G-CNT Graphene and CNT hybrid structure

hBN Hexagonal boron nitride

IC Integrated circuit

IHS Integrated heat spreader

Nano-TIM Nanocomposite thermal interface material

SEM Scanning electron microscope

TCR Thermal coefficient of resistance

TCVD Thermal chemical vapor deposition

TIM Thermal interface material

TSV Through silicon via

VA-CNT Vertical aligned carbon nanotube

3D Three dimensional

### **Table of Contents**

| 1. Introduction                                                                      | 1  |

|--------------------------------------------------------------------------------------|----|

| 1.1 Background                                                                       | 1  |

| 1.11 Thermal Management in 3D IC packaging                                           | 3  |

| 1.12 Interconnect in 3D IC packaging                                                 | 4  |

| 1.13 Supercapacitors                                                                 | 4  |

| 1.2 Scope and Outline                                                                | 5  |

| 2. Carbon Materials                                                                  | 7  |

| 2.1 Carbon Nanotube                                                                  | 7  |

| 2.2 Graphene                                                                         | 9  |

| 2.3 Applications in 3D IC packaging                                                  | 12 |

| 2.3.1 Carbon material for thermal management application                             | 12 |

| 2.3.2 Carbon material for interconnect application                                   | 13 |

| 3. Carbon based material for Thermal management application in 3D IC packaging       | 15 |

| 3.1 A Novel nanocomposite thermal interface material (Nano-TIM) for heat dissipation | 15 |

| 3.1.1 Fabrication of the Nano-TIM                                                    | 18 |

| 3.1.2 Performance evaluation of the Nano-TIM                                         | 20 |

| 3.1.3 Reliability test of the Nano-TIM                                               | 23 |

| 3.2 CNT-Graphene hybrid material for heat dissipation application                    | 24 |

| 3.2.1 Synthesis of graphene material                                                 | 25 |

| 3.2.2 Synthesis of Graphene-CNT hybrid material                                      | 28 |

| 3.2.3 Thermal Performance characterization of CNT-Graphene hybrid material           | 32 |

| 3.3 Boron Nitride based film for heat spreader application                           | 39 |

| 3.3.1 Fabrication of Boron Nitride based film                                        | 39 |

| 3.3.2 Microstructure characterization                                                | 40 |

| 3.3.3 Thermal performance characterization                                           | 43 |

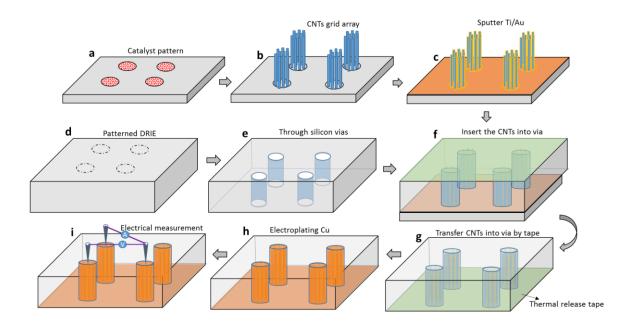

| 4. CNT based TSV for 3D IC packaging                                                 | 45 |

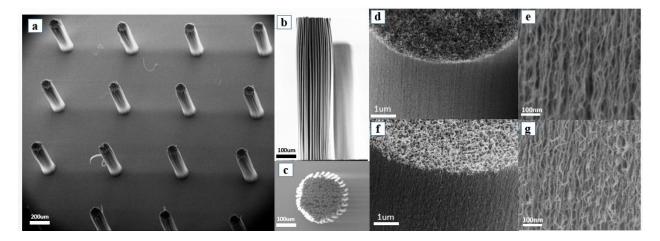

| 4.1 Synthesis of VA-CNTs                                                             | 46 |

| 4.2 VA-CNTs TSV for interconnect                                                     | 48 |

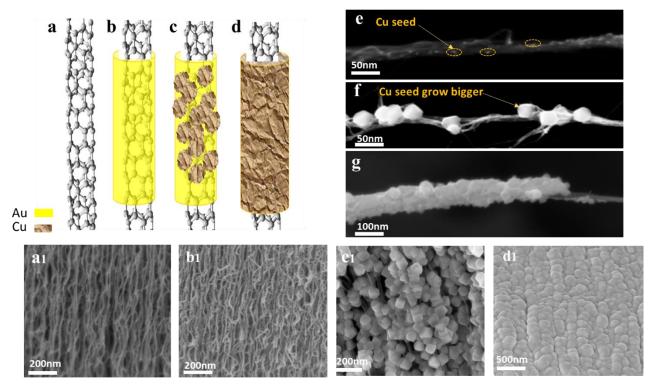

| 4.3VA-CNT-Solder TSV for interconnect                                                | 52 |

| 4.4 VA-CNT-Cu TSV for interconnect                                                   | 55 |

| 4.5 Flexible TSV for interconnect                                                    | 65 |

| 4.6 Summary and discussion                                                           | 68 |

| 5. Carbon hybrid supercapacitors                                                     | 71 |

| 5.1 Carbon hybrid material characterization                                          | 72 |

| 5.2 Electrochemical measurements                                                     | 74 |

| 6. Conclusion and Outlook                                                            | 79 |

| Acknowledgements                                                                     | 81 |

| Bibliography                                                                         | 82 |

### Chapter 1

#### 1. Introduction

#### 1.1 Background

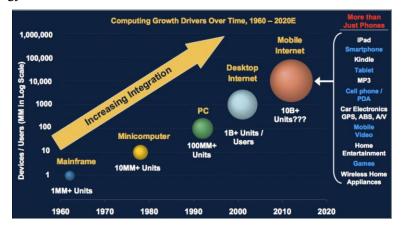

Over the past few decades, the rate of progress in the semiconductor industry has roughly followed Moore's law, determined by Gordon Moore in 1965 [1]. Dating back over the past 30 years, the quantity of transistors has dramatically increased from thousands to billions in just a single microchip. This is why a desktop computer a decade ago has the same or even less functions than a current smart phone. However, the amount of energy consumer by mobile phone is much smaller than a computer. More importantly, this kind of high-integrated microchip has brought digital electronics including cellphone, iPad, Kindle and Tablet into our life, totally changing our daily lifestyle. Fig. 1.1 shows that increased integration degree in technology has brought human from desktop internet era to mobile internet era (MonolithIC 3D Inc. Report). This is due to both academia and industry keeping up with Moore's law and the ability of semiconductor manufacturer to advance technology.

Fig. 1.1. The development trend of digital electronics devices from 1960 to 2020.

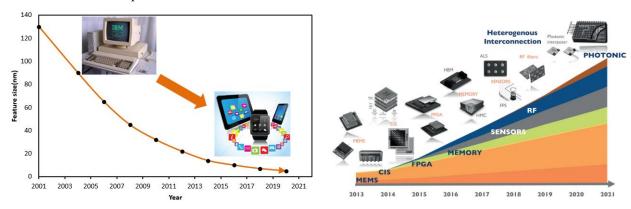

However, over the past five years the performance of microchip has been fallen behind the exponential growth that Moore predicted. International Technology Roadmap for Semiconductor (ITRS) reported that the pace of advancement and the miniaturization trend of manufacturing size has slowed down since reaching 14 nm in 2013, as shown in Fig 1.2. Gordon Moore himself also foresaw that the rate of progress of semiconductor development would eventually reach saturation [2]. The reasons for falling behind Moore's law are mainly from two aspects, which are the fundamental limit and engineering manufacture limit respectively. For the fundamental limit, if the microprocessors feature size decreases to 4 nm, as is

scheduled to occur in around 2020, then transistor performance will be substantially affected by quantum tunneling [3]. For the engineering limit, there are obstacles in the integrated circuit (IC) manufacturing process, where accuracy at the 4 nm scale is a huge challenge. In order for Moore's law to continue, the semiconductor industry has invested many efforts in IC packaging. In order to integrate so many transistors in the microchip, IC manufacturer invented three-dimensional IC (3D IC) concept to continue the trend of faster and smaller IC products.

Fig. 1.2. Left diagram shows the decrease in feature size with respect to time [4]; Right diagram describe the 3D IC market distribution from 2013 to 2021.

3D IC is an integrated circuit manufactured by stacking silicon wafers and/or dies and interconnecting them vertically using through-silicon via (TSVs) so that they behave as a single device to achieve performance improvements at reduced power and smaller footprint than conventional two dimensional processes [5]. As shown in Fig 1.2, 3D IC packaging technology is becoming more and more important in the future microelectronics field. The market for 3D IC technology is expanding at a 22% compound annual growth rate. The growth is mainly driven by increased adoption of 3D IC devices in more and more fields including 3D memories with high performance computing, RF field, sensor filed like finger print sensor and photonic devices with high-end graphics. However, generally speaking, every new technology emerging in the market always brings some new issues in this field. The 3D IC packaging is not an exception. Because 3D IC packaging realizing higher density IC devices, thermal issue will be one of big challenges to manage to keep the devices working under an acceptable temperature. Another key technology to realize communication between chips in 3D IC is the TSV technology. High performance and smaller size interconnect is extremely important in the very limited silicon area. In this thesis, we mainly focus on improving heat dissipation and the performance of interconnects in 3D IC packaging to address these two challenges in developing this new IC packaging technology, as shown in Fig. 1.3.

<u>Chapter 1</u> Introduction

Fig. 1.3. The scheme of a typical 3D IC integration packaging.

#### 1.11 Thermal Management in 3D IC packaging

The trend of microelectronics system is towards to smaller size, higher integration density and more functionality [6]. A billion of transistors and CMOS cells are designed on centimeter sized chips [7]. Therefore, large amount of thermal energy will be generated in a limited space when a chip with billions of cells is in operation. For instance, the laser devices and systems which are used as power sources for fiber communication can generate heat flux up to 1000 W/cm<sup>2</sup> in less than 0.5 mm<sup>2</sup> area. LED devices also lead to high heat intensity between 300 and 600 W/cm<sup>2</sup> due to the high power loading in a small area. Moreover, if the power cannot be distributed uniformly on the chip, hot spots will be formed in a certain area of the chip, where tremendous power densities can be reached during the operation of the devices [8], [9]. Hot spots can be formed easier when the chip thickness is decreased [10]. Unfortunately, the hot spot will cause many problems in electronic devices, including fractures of circuits, delamination, melting, creep, corrosion, electro-migration and even combustion of packaging materials [11]. In other words, high temperature leads to the overheating of specific areas in electronic devices, which lowers the performance, and reliability of the devices. Therefore, it is of strategic importance that heat dissipation is well managed and controlled. In fact, poor thermal management solution is restricting the growth and further development of electronics systems according to the report of the industry consortia iNEMI and ITRS [12],[13]. Particularly in higher power electronics, the chips are often stacked or connected in parallel in a multichip module. As 3D IC chip solutions are incorporated into more and more applications, the urgent demand for efficient thermal management will push the fast development of heat dissipation technologies including using new material like carbon based material.

The methodologies of thermal management for 3D IC packaging can be categorized into passive cooling and active cooling. For active cooling methodologies, there are several approaches including using fans, thermal exchangers, low power loading and integrating thermoelectric material on the microchip for cooling

[14]. In contrast, passive methodologies strongly rely on material performance such as the heat sink material, heat spreader material and thermal interface material (TIM). In this thesis, we mainly focus on passive cooling material application in 3D IC packaging.

#### 1.12 Interconnect in 3D IC packaging

As previously mentioned, 3D IC technology is one of the main driving forces for the continuous down scaling of the IC devices [15] [16]. There are many interconnection technologies such as wire bonding, edge connect and capacitive or inductive coupling method to fabricate 3D-IC devices [17][18]. However, the most key technology for enabling 3D-IC package is through-silicon via (TSV) technology which acts as paths for signal exchange and power delivery between the stacked chips [19][20]. TSV technology has allowed great progress in reducing signal delay, enhancing the IC integration and decreasing the overall packaging volume [21]. Thus, the development of this technology is accelerating the miniaturization of 3D-IC devices as well as integration of I/O systems.

The filling materials used in the silicon via determine the key performance of TSVs. There are various materials that have been used for the TSV, such as tungsten (W) [22], copper (Cu) [23], and a Ag/polypyrrole composites [24]. The copper is the most commonly used filling material for TSV due to its excellent electrical conductivity and low process costs. However, the main limiting factor for Cu-TSV technology is the large difference in the coefficient of thermal expansion (CTE) between Cu and Si, which results in mechanical stress in the TSV and the surrounding Si [25]. In addition, the electro-migration and skin effects also limit the application of Cu TSV in high frequency application [26]. Moreover, it is currently not technologically possible to use Cu for high aspect ratio via structures [27]. However, CNT is the other potential filling material for TSV to address the problems encountered by Cu, since Carbon Nanotubes (CNTs) have very low thermal expansion coefficients [28], joule heating [29] and do not fail at high current densities due to electro-migration [30],. More importantly, CNTs can achieve high aspect ratios needed to continue 3D IC device miniaturization trends [31]. In addition, CNT bundles also exhibited excellent flexibility performance, which can be able to use in flexible electronics for interconnect [32]. Thus in this thesis, we will work on CNT based TSV to replace metal for 3D IC interconnect.

#### 1.13 Supercapacitors

Over the past ten years, the market of portable electronic devices and electric vehicles is expanding in a high speed. Consequently, energy storage devices with high energy density and high power density are becoming urgent demand. Although Li-ion batteries have exhibited a good energy performance in many electronic devices [33]–[37], the power performance is still not sufficient for many related applications due to the inherent limitation of Li-ion battery [38], [39]. It usually takes a long time to discharge and recharge, which seriously affects their ability to deliver power. However, supercapacitors are now attracting a lot of

attention due to the fact that most researchers believes that supercapacitors will be a critical enabling technology for much stricter application like the internet of things device. Actually the supercapacitors indeed can offer quite a lot of unique performances like pulse power supply, long cyclic life, combination of high power and high energy. In this thesis, a carbon hybrid material in supercapacitor application will be presented.

#### 1.2 Scope and Outline

This thesis addresses integration of carbon-based material into 3D IC microsystem to meet current challenges of interconnect technology and thermal management. In this thesis, a few integration processes were developed for the realization of carbon-based material for interconnect and heat dissipation application. These include growth, densification, transfer, electroplating and integration of carbon based materials. These basic processes were also combined with 3D IC packaging process for applications as: (1) thermal management solution including thermal interface material, micro heat sink and heat spreader; (2) through silicon via for interconnect; (3) carbon hybrid supercapacitors.

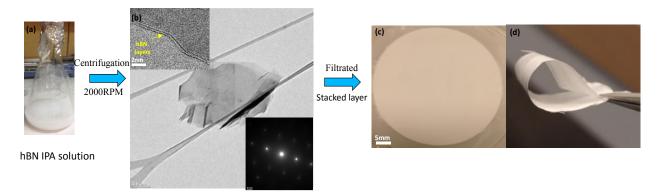

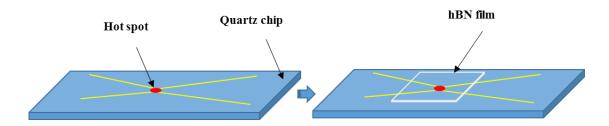

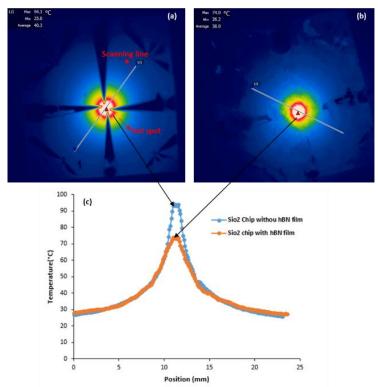

Chapter 2 mainly introduces the basics of carbon materials such as carbon nanotube and graphene. The structure and properties of carbon materials was simply reviewed, particularly in heat dissipation and interconnect field. Additionally, the potential application in 3D IC microsystem was briefed in this section. Chapter 3 presents the results on the fabrication, characterization and heat dissipation effect of thermal management material, which included thermal interface material, micro heat sink and heat spreader. Firstly, a novel nanocomposite thermal interface material (Nano-TIM) based on metallic indium in a silver-coated nanofiber network was developed and characterized in the first section. For dissipating heat energy into ambient air from IC chip, a micro heat sink was fabricated using CNT and graphene hybrid material for heat dissipation application in the IC chip level. In the third section, we focused on addressing the hot spot issue existing in the IC chip by developing the hexagonal boron nitride (hBN) heat spreader that was fabricated using liquid phase exfoliation method.

Chapter 4 is devoted to the development of CNT based material for TSV interconnection in IC packaging. In the first section, synthesis processes such as the densification and transfer process used for CNTs are illustrated. In order to improve the TSV performance, densified CNTs TSV, CNT-Solder TSV and CNT-Cu TSV are each developed, evaluated and demonstrated in the 3D IC stacked chip microsystem. Due to the flexibility of CNTs, the flexible CNT-metal TSV was also demonstrated in the flexible and stretchable electronics devices.

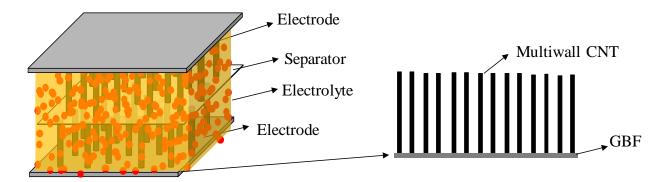

In chapter 5, we developed a controllably aligned CNTs and graphene-based film hybrid structure to use as supercapacitors electrode. This pillared CNT-G hybrid material was synthesized using chemical vapor

deposition. The atomic structure of covalently bond was characterized by high-resolution transmission electron microscopy (TEM). The performance of this CNT-G hybrid supercapacitor was investigated. Chapter 6 concludes the thesis and gives a brief outlook.

### Chapter 2

### 2. Carbon Materials

Nanostructured carbon materials have attracted more and more attentions due to their excellent performance in many fields such as high thermal conductivity, excellent electrical conductivity, flexible mechanical performance, high current carrying capability etc [40]–[42]. Due to various allotropes, nanostructured carbon material is a big family that comprise zero-, one-, two-, and three-dimensional materials such as fullerene, carbon nanotubes (CNT), graphene, diamond and porous carbon respectively. In this chapter, we focus on studying carbon nanotubes and graphene basic properties and their potential applications in the microelectronics.

#### 2.1 Carbon Nanotube

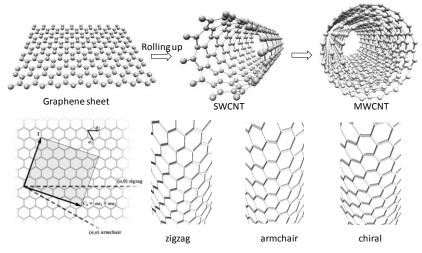

Carbon nanotubes (CNT) were first discovered in 1991 by Iijima [43], which opened up a new era in materials science. Simply speaking, CNT can be considered as a long hollow tube with the walls consisted of one-atom-thick carbon layer, called monolayer graphene now. CNT can be categorized by the wall number like single-walled CNT rolled by single layer of graphene. Multi-walled CNT is rolled up by multi-layer graphene. In addition, CNT can be classified into different types by the way of graphene rolling, which can be represented by a pair of indices (n, m). Based on the combination of n and m, the CNT can be categorized zigzag, armchair and chiral CNT. From the perspective of CNT property, nanotubes can also divide into metallic CNT and semiconducting CNT. The specific structures of different type of carbon nanotubes are illustrated in Fig. 2.1. The electrical, thermal and mechanical properties of the CNT, considering its use as an interconnect and thermal management material, are discussed as follows.

Fig. 2.1. The different structure of CNTs

Carbon Materials

#### Electrical performance

The electrical properties of SWCNTs are strongly dependent on the chirality (n, m) and the diameter of nanotubes [44]. If the chirality (n, m) can satisfy n-m=3i, where i is an integer, this CNT will be the metallic nanotubes where the electrons can transport in the metallic way. Otherwise, the CNTs will exhibit semiconductor behavior with a band gap which is roughly inversely proportional to the tube size [40], [45], [46]. Based on the statistical results in mass scale growth, the metallic CNTs can occupy one third of all produced CNTs, while two thirds are semi-conductive. For single-walled CNTs, the electrical resistivity of individual CNTs can be as low as  $10^{-6} \,\Omega$ -cm due to ballistic conductions [47], [48]. As to multiwall CNTs, the electrical resistivity can reach to  $3 \times 10^{-5} \,\Omega$ -cm [49], [50]. Moreover, if the length of a conductive CNT is shorter than its electron mean free path, a quantum effect will be behaved [51]. In addition, CNTs also have a very strong capability to carry high current density as high as  $10^9 \, A/\text{cm}^2$  [49], [52], which is three orders of magnitude higher than that of copper. Additionally, CNTs also are with very low-level joule heating effect and less susceptible to electro-migration [29], [30].

#### Thermal performance

Carbon nanotube like graphene is an excellent thermal conductor material due to its unique structure. Thermal transport in CNT is mainly conducted by the intrinsic properties of the strong sp<sup>2</sup> lattice, rather than by phonon scattering on boundaries or by disorder, giving rise to extremely high K values [53]–[56]. According to previous theoretical results, the thermal conductivity of CNTs can be ranged from  $\sim 3000$  to  $\sim 6600 \text{ W} \cdot \text{m}^{-1} \cdot \text{K}^{-1}$  using different simulation method [57]–[59]. Meanwhile, many experimental data were also reported in the past ten years. Commonly quoted values for individual CNT are  $\sim 3000 \text{ W} \cdot \text{m}^{-1} \cdot \text{K}^{-1}$  for MWCNT [53] and  $\sim 3500 \text{ W} \cdot \text{m}^{-1} \cdot \text{K}^{-1}$  for SWCNT [54] at room temperature. However, it has to be noted that crystallographic defects strongly influence the final thermal transport capability of CNTs. Particularly in large-scale defects as stone wales defects, it leads to strong phonon scattering and gets a big reduction of thermal conductivity in consequence [60]. Table 2.1 shows the specific thermal performance of CNTs measured by different methods in the past years.

Table 2.1: The thermal conductivity of carbon nanotubes

| Sample | $(\mathbf{W} \cdot \mathbf{m}^{-1} \cdot \mathbf{K}^{-1})$ | Method                                                      | Comments                            | Refs |

|--------|------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------|------|

| MWCNT  | >3,000                                                     | Electrical; micro-heater                                    | Individual; diffusive;<br>suspended | [53] |

| SWCNT  | ~3,500                                                     | Electrical self-heating                                     | Individual; boundary                | [54] |

| SWCNT  | 1,750–5,800                                                | Thermocouples                                               | Bundles; diffusive                  | [61] |

| SWCNT  | 3,000-7,000                                                | Electrical; micro-heater                                    | Individual; ballistic;<br>suspended | [62] |

| CNT    | 1,100                                                      | Electrical; micro-heater                                    | Individual; suspended               | [63] |

| CNT    | 1,500-2,900                                                | Electrical                                                  | Individual                          | [64] |

| CNT    | ~6,600                                                     | Theory: molecular dynamics                                  | $K_{\rm CNT} < K_{\rm G}$           | [57] |

| CNT    | ~3,000                                                     | Theory: molecular dynamics                                  | Strong defect dependence            | [65] |

| SWCNT  | ~2,500                                                     | Theory: Boltzmann transport equation                        | $K_{\rm CNT} < K_{\rm G}$           | [58] |

| SWCNT  | ~7,000                                                     | Theory: molecular dynamics and Boltzmann transport equation | L > 20 nm                           | [59] |

#### Mechanical performance

It is well known that CNT is the strongest material yet discovered in the world, due to the strong covalent sp<sup>2</sup> bonds between the carbon atoms. A lot of measurement methods such as atomic force microscope (AFM) [66], electromechanical resonant vibrations [67] and observations in transmission electron microscope [68], were developed to measure the Young's modulus and mechanical strength. Most of results claimed that the Young's modulus of CNTs could be able to reach to TPa level ranged from 0.41 TPa to 4.15 TPa. Normally speaking, the mechanically strength of CVD-CNT is usually lower than arc-CNT, which is possibly because of more defects introduced during CVD growth [66], [69]. In addition, coefficient of thermal expansion of CNT is close to zero, which can largely reduce thermal stress occurred at the interface between CNT and silicon  $(2.6 \times 10^{-6} \, \text{K}^{-1})$  in the IC application compared to copper  $(16 \times 10^{-6} \, \text{K}^{-1})$  and aluminum  $(23.6 \times 10^{-6} \, \text{K}^{-1})$ . Moreover, the CNT is also very flexible and resilient, indicating intrinsic advantage in wearable and flexible electronics application [32], [70].

#### 2.2 Graphene

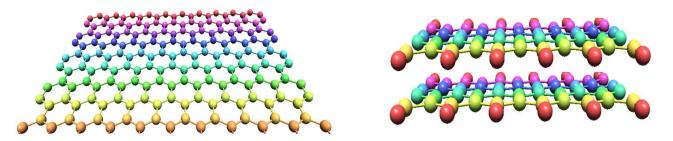

In this section, some basics of graphene material is introduced. Regarding graphene application in the microelectronics system, monolayer graphene, bilayer graphene and graphene based film are mostly investigated by worldwide researchers due to their respective unique performance. The Fig 2.2 showed the schematic structures of graphene material.

Fig 2.2: Schematic structures of graphene and bilayer graphene.

#### Monolayer graphene

Graphene is a two-dimensional material consisting of a single layer of sp<sup>2</sup>-hybridized carbon atoms arranged in a hexagonal structure [41]. It is the first 2D atomic crystal material known by human. Many extreme properties combined on this just one-atom thin graphene. Its room-temperature electron mobility can reach to  $2.5 \times 10^5$  cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> [71], which already attracts a lot of transistor research work using graphene [72]–[76]. Graphene also exhibits excellent mechanical properties such as a Young's modulus of 1 TPa [77], the intrinsic strength of 130 GPa [77] and flexural rigidity of 3.18 GPa·nm<sup>3</sup> [78]. Moreover, super high thermal conductivity (above 3000 W·m<sup>-1</sup>·K<sup>-1</sup>) were experimentally measured through different methods by researchers [79]. This extreme thermal property triggered many graphene thermal applications in the high power IC field [80]–[82]. In addition, the optical absorption of the graphene is just ~2.3% over the visible spectrum [83], which combined with its high electrical conductivity [84], could result in transparent conductive electrodes applications [85]–[87].

#### Bilayer graphene

Bilayer graphene is basically a kind of material consisting of two layers of graphene. Commonly, bilayer graphene is categorized into AB-stacked structure and AA-stacked structure. AB-stacked bilayer graphene means that half of atoms lie directly over the center of a hexagonal of the lower graphene layer and another half of atoms locate over an atom from below layer [88]. Other type is AA-stacked structure where the two layers are exactly aligned each other [89]. For AB-stacked bilayer graphene, the band structure is very interesting. Its band gap is zero just like monolayer graphene when it is pristine form. But the non-zero band gap can be induced by electrical-displacement field [90], [91]. This unique property could be potentially used to develop nanoelectronics devices such as field-effect transistor-based switches and pseudo-spintronics [92].

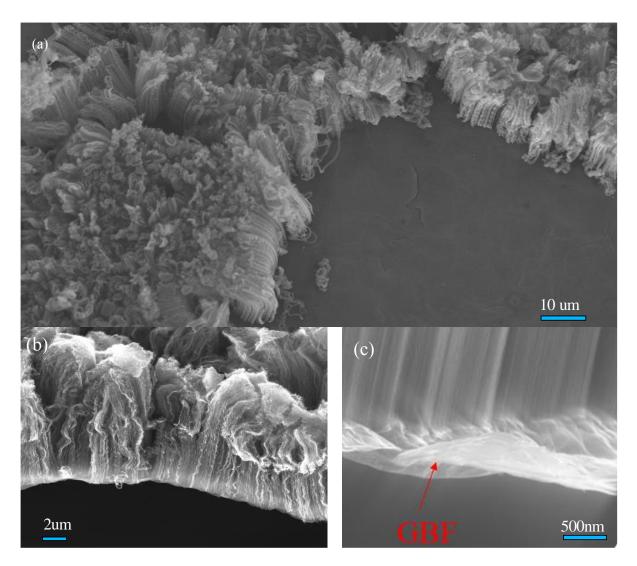

#### Graphene Based Film

Graphene based film (GBF) is a film, which consists of a few graphene layers by stacking together in order, as shown in Fig. 2.3. Graphene based film is usually obtained from graphene oxide (GO) film through high temperature reduction [87], [93]–[95] or chemically reduction [96]–[98]. As to GO film, the GO dispersion can be prepared using Hummer's method [99] and then be infiltrated by vacuum to get the film [100]. Graphene based film exhibits outstanding properties as monolayer graphene, particularly in the area of thermal performance and electrical conductivity. Table 2.2 lists the recent research work on investigating thermal performance of graphene by different method. For instance, Zhang et al. [100] claimed that the thermal conductivity of GBF can reach to around 1200 W·m<sup>-1</sup>·K<sup>-1</sup>, which is several times higher than copper and aluminum. Moreover, Chen et al. [101] reported a super high electronic conductive film ( $\sim 3112 \text{ S·cm}^{-1}$ ) through reduction of GO film by electrical current-induced annealing treatment. Besides these excellent thermal and electrical performances, more importantly it is a freestanding film with a strong mechanical performance, which means that it is much easier to be handled compared to monolayer graphene in many applications.

Fig 2.3: The structure of graphene based film.

Table 2.2: The thermal conductivity of graphene material.

| Sample     | K (W mK <sup>-1</sup> ) | Method                  | Comments                                         | Refs  |

|------------|-------------------------|-------------------------|--------------------------------------------------|-------|

| Graphene   | ~2,000–5,000            | Raman optothermal       | Suspended; exfoliated                            | [56]  |

| FLG        | ~1,300–2,800            | Raman optothermal       | Suspended; exfoliated; $n = 4-2$                 | [102] |

| Graphene   | ~2,500                  | Raman optothermal       | Suspended; CVD                                   | [103] |

| Graphene   | 1,500-5,000             | Raman optothermal       | Suspended; CVD                                   | [104] |

| Graphene   | 600                     | Raman optothermal       | Suspended; exfoliated; $T \approx 660 \text{ K}$ | [105] |

| FLG ribbon | 1,100                   | Electrical self-heating | Supported; exfoliated; $n < 5$                   | [99]  |

| Graphene   | 600                     | Electrical              | Supported; exfoliated                            | [100] |

| GBF        | ~1200                   | Laser flash             | Graphene film; thickness: ~30um                  | [100] |

| G paper    | ~1500                   | Electrical self-heating | Graphene paper; Ball-milling exfoliated          | [101] |

#### 2.3 Applications in 3D IC packaging

Thanks to the extraordinary properties of CNT and graphene as described in previous sections, many research works are concentrated on the CNT and graphene applications, particularly in the area of thermal management and interconnect. The specific applications are introduced in the following sections.

#### 2.3.1 Carbon material for thermal management application

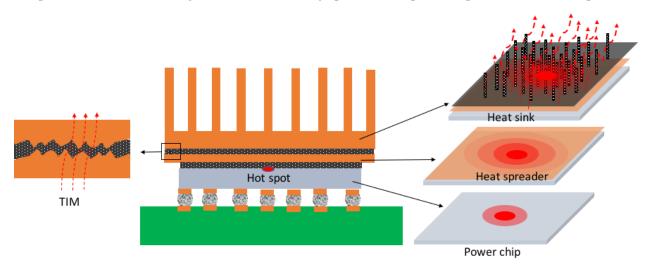

Since high capability of thermal transport in CNT and graphene was demonstrated, more and more researchers are trying to use these high thermal conductive materials into 3D IC field where there is urgent requirement on heat dissipation. A comprehensive thermal management solution using passive cooling method for IC packaging includes thermal interface material, heat spreader and heat sink. Due to graphene's high in-plane thermal conductivity and fantastic 2D structure, graphene and graphene based films have been widely investigated for using as heat spreader [80]–[82], [108]–[112]. Balandin et al. presented that thermal management of GaN transistors can be substantially improved via introduction of alternative heat dissipation channels implemented by few-layer graphene [82]. Hao et al. showed that the hot spot temperature can be lowered by  $\sim 28$  °C through chemically bonding the graphene based film on top of thermal test chip [100]. Some simulation work also demonstrated that the graphene based film have a potential for hot spot removal and the effect of heat dissipation will be more pronounced as number of transistors increases [113]. Due to high thermal conductivity in one dimensional direction and flexibility of aligned CNTs, it is more suitable to be used as TIM for improving thermal interface resistance. Many work

have therefore been done including utilize CNTs as fillers for composite TIM [114], [115], pure vertically aligned CNTs film TIM [116], [117] and CNT-metal matrix TIM [118]. For effectively resolving the contact issue between metal surfaced and vertically aligned multiwall CNT arrays, Kaur et al. published some related work in Nature Communication where they got a sixfold reduction of thermal interface resistance by bridging the interface with short, covalently bonded organic molecules [119]. Due to large surface area ratio of CNT forest, potential CNT based heat sink application were also studied in IC heat dissipation field. For instance, Fu et al. presented that a water-assisted CNT microfin on-chip cooling solution can effectively cool down high power chip (~ 1000 W·cm²) by several 10 °C [120]. Huang et al. demonstrated that cooling effect of CNT based heat sink were very related to length and arrangement of CNTs [121]. In recent years, graphene-CNT hybrid structures for thermal management have recently gained much attraction [122]–[127]. Through molecular dynamics simulations (MDS) large heat dissipation capability of this hybrid materials has been theoretically verified by some researchers [27][29][30]. Thermal transition junction between the CNT and the graphene film dominate the thermal resistance of such hybrid structure materials [31][32].

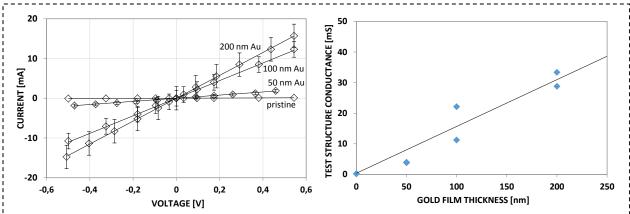

#### 2.3.2 Carbon material for interconnect application

As mentioned in the previous sections, CNT and graphene both has extreme high electrical conductivity and extreme current carrying capacity. In addition, due to their inherent nanostructure, they are able to achieve nanoscale or finer interconnect. All of their advantages for interconnect trigger many related applications in 3D IC microsystem. For instance, CNTs have been proposed as promising candidate materials to build next generation interconnects in miniaturized electronics, as both on-chip and off-chip interconnects [132]–[136]. The lower resistivity of pure CNT interconnect can be as low as  $\sim 10^{-6} \,\Omega \cdot m$ , which still does not excel that of metals such copper. In order to further reduce resistivity of CNT based interconnect, CNT-metal composite materials were developed for interconnect. Subramanian et al. [137] synthesized a novel CNT-Cu composite film using electroplating, and showed a hundredfold increase in ampacity compared with Cu. Feng et al. [138] developed a fabrication method where copper was electroplated through a tungsten seed layer onto as-grown CNTs inside a blind via to fabricate CNT-Cu TSVs. Except CNT-based interconnect applications, graphene also make many researchers interested in studying its potential interconnect in IC packaging [139]. Due to its transparency, it is also widely used as transparent conductors [42], [140]-[142]. Kin et al. demonstrated that the graphene based transparent interconnect exhibited competent performance for application in LED field [143]. Taking advantage of graphene's unique band structure, graphene based transistor also become another hot topic [74]. For example, Liao et al. claimed a self-aligned high-speed graphene transistors or circuit were successfully demonstrated in high-speed and high-frequency electronics [144].

<u>Chapter 2</u> <u>Carbon Materials</u>

## **Chapter 3**

# 3. Carbon based material for Thermal management application in 3D IC packaging

In this chapter, we mainly focus on studying thermal management application for high power chip in 3D IC packaging. As mentioned in the previous chapter, thermal issue has already become one of the bottlenecks for miniaturization of IC devices. Thus, this chapter investigates some new high thermal conductive carbon based material for thermal management applications. As shown in Fig. 3.1, a comprehensive thermal management solution for high power IC chip will be presented in this chapter.

Fig. 3.1. Thermal management solution for high power chip.

#### 3.1 A Novel nanocomposite thermal interface material (Nano-TIM) for heat dissipation

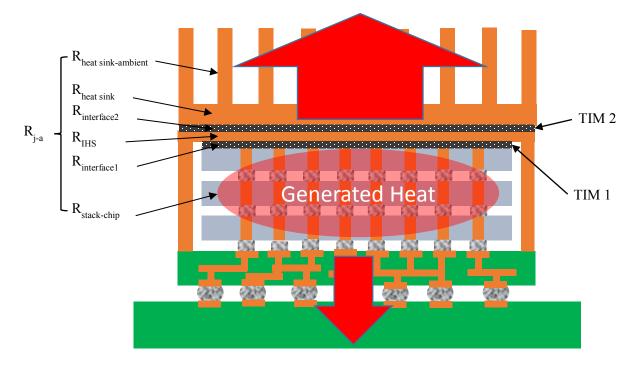

In microelectronics packaging, it is important to keep the integrated circuit junction temperature  $(T_j)$  as close as possible to the ambient temperature  $(T_a)$ . Since the temperature drop  $\Delta T$  from the junction temperature to the ambient can be written

$$\Delta T = R_{\text{thermal }} Q \tag{2.1}$$

where  $R_{thermal}$  is the thermal resistance and Q is the heat flux, it is important to keep the thermal resistance as low as possible. Thus, to keep the thermal resistance along the paths as small as possible is critical for the performance of an IC package. A typical layout of 3D IC package is outlined in Fig. 3.2 to illustrate the heat flow paths. For this IC packages the main heat flow path is typically from power chip to the top heat

sink. Thus, the two thermal interface materials between the circuit and the heat sink mainly limit thermal resistance from junction-to-ambient. In this thesis, a novel nanocomposite thermal interface material for efficient 3D IC packaging has been proposed and evaluated as described in the appended paper A.

Fig. 3.2. Typical 3D IC packaging and the heat flow paths of IC device.

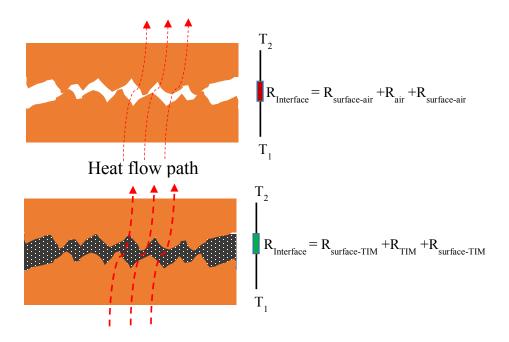

The main role of the thermal interface material is to fill the air voids and gaps, which inevitably arise at the interface between two surfaces due to surface roughness and the relative asperity. As can be seen in Fig. 3.3, the thermal interface resistance can be decreased considerably if the high resistance air gap is replaced by a low resistance thermal interface material.

Fig. 3.3: Schematic of the thermal resistance across interface with and without TIM.

The current trends of developing new TIMs are focused on the nanocomposite materials, such as embedding carbon nanotubes [145]–[147] and silver nanowire arrays in a polymer matrix [148], due to the unique properties of nanomaterials on surface area, defects, mechanical, electrical, and thermal performance. Meanwhile, the improvement and characterization of traditional TIMs, including solder-based TIMs [149] and phase-change materials [150], are also an important topic in the thermal management field. The researchers have developed several metal based nano-fiber matrix composite TIMs for heat dissipation in the electronics packaging. Zhang et al. reported the performance of indium-tin-bismuth alloy based nano-fiber composite TIMs used as a phase-change material [151]. However, phase- change TIM material can easily be oxidized and corroded at the elevated temperature cycles [152]. Zandén et al. studied the thermal performance and reliability of tin-silver-copper based nano-polymers composite in a die attachment [153]. Murugesan et al. developed carbon fiber based tin-silver-copper alloy matrix composite TIM for thermal management of high power electronics [154]. However, this kind of solder based nanocomposite TIM has to be soldered onto the substrate at around 220 °C which possibly brings a risk of reliability of some temperature sensitive device [155].

In the novel nanocomposite thermal interface material proposed in this thesis section, we have chosen indium as the base material of the TIM to exploit the high thermal conductivity and low melting temperature of the metal [156]. However, pure indium is easily deformed due to its low yield strength and its tendency of flowing out during die attach process [157]. Addressing the weaknesses of indium, a novel

nanocomposite thermal interface material (Nano-TIM) based on metallic indium in a silver-coated polyimide (PI) network was developed. The polymer network defines the geometry of the thermal interface material, such as its shape and bond line thickness. The metallic part is responsible for heat transfer.

#### 3.1.1 Fabrication of the Nano-TIM

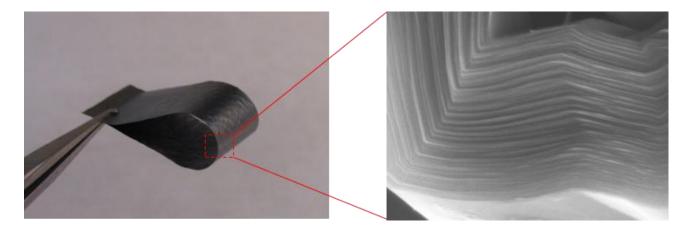

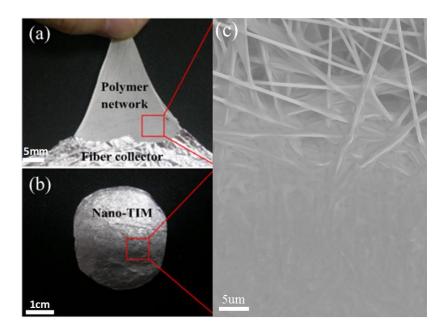

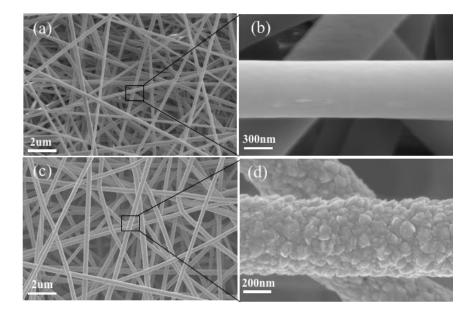

The detailed processes for fabricating this Nano-TIM is described in paper A. In short, the polymer network matrix is electrospun and then infiltrated with indium after surface modification where the fibers are coated with silver. A silver-coated polyimide network and a piece of the final Nano-TIM are shown in Fig. 3.4. The detailed structures of the polyimide nanofibers network before and after surface modification by coating silver are shown in Fig. 3.5.

Fig. 3.4. (a) Polyimide network formed with electrospinning process; (b) a piece of Nano-TIM fabricated with infiltration process; (c) SEM image of nanofiber network after partly metal infiltration. (From Paper A)

Fig. 3.5. (a) and (b) show pristine polyimide nanofibers network formed through electrospinning process; (c) and (d) show the nanofibers network with Ag nanoparticles coating after surface modification. (From paper A)

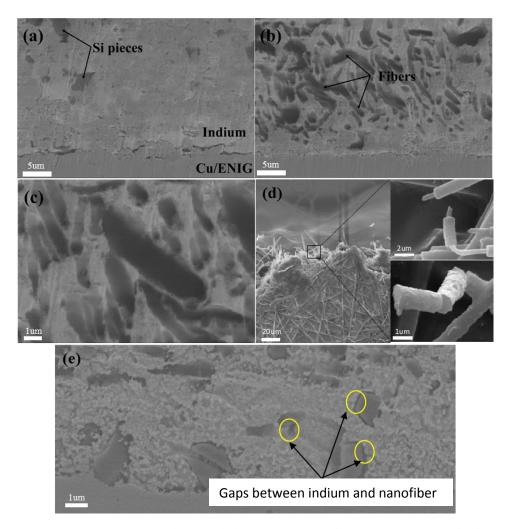

In order to study the inner structures of the Nano-TIM by scanning electron microscopy, a number of cross-section samples were prepared using a pure indium TIM sample as a reference. Pure indium at the interface between the copper pads with an electroless nickel immersion gold (ENIG) is shown in Fig. 3.6 (a). Some Si pieces are found in the indium matrix. These Si pieces come from the Si chip used during the cross-section polishing process. The Si pieces were polished off the Si chip and embedded in the soft indium. In Fig. 3.6 (b), the polymer fibers can be observed in the indium matrix. There are no visible voids that can be seen in Fig. 3.6 (b), indicating the porous polymer network has been completely filled with indium after the infiltration process. Fig. 3.6 (c) shows an image of Nano-TIM with high magnification. In Fig. 3.6 (c), each fiber is tightly covered by the indium matrix. In general, the porous fibers network is extremely difficult to be fully wetted and filled by liquid indium due to the inert nature of PI and the small gap between the fibers as shown in Fig. 3.6 (e). However, in this Nano-TIM, the surface of the fibers has been coated by silver, which significantly improves the wettability of liquid indium to the surface. For all nanofibers observed, each individual nanofiber was tightly surrounded by indium under the help of the silver particle as shown in the representative image given in Fig. 3.6 (d). As a result, the liquid indium can successfully infiltrate the fiber network by using high pressure in the infiltration process.

Fig. 3.6. Cross-sections of (a) pure indium and (b) Nano-TIM with Cu/ENIG pad; (c) high magnification image of the Nano-TIM; (d) shows the inner structure of Nano-TIM after damage; (e) shows the interface status between indium and the nanofiber without silver coating. (From paper A)

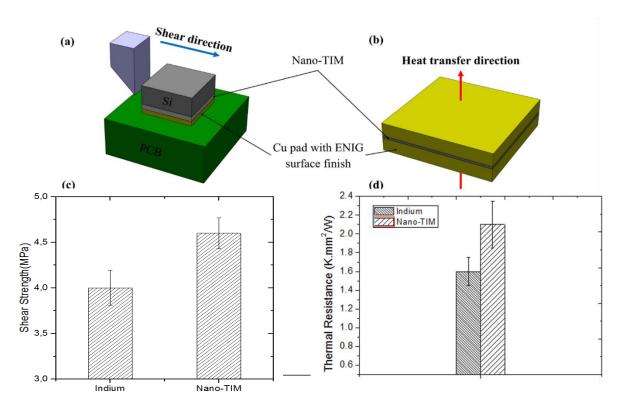

#### 3.1.2 Performance evaluation of the Nano-TIM

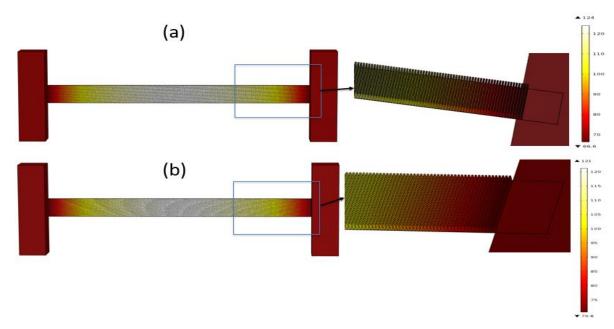

As described in detail in paper A, the novel nanocomposite thermal interface material was evaluated by shear test, thermal resistance measurements, and thermal infrared camera tests. The schematic structures of the shear test setup and the thermal interface resistance measurements are shown in Fig. 3.7, and the results of these test are shown in Fig. 3.7 (c) and (d). These figures show the results obtained from the novel Nano-TIM in comparison to the results obtained for pure indium TIMs. The results show that the average shear strength of Nano-TIM is higher than that of pure indium, which could be attributed to the reinforcement effect of silver-coated PI fibers. For the thermal resistances, that of the novel Nano-TIM is only slightly larger

than that of a purely metallic indium TIM, 2.1 and 1.7 K·mm<sup>2</sup>·W<sup>-1</sup>, respectively. The results indicate that the polymer network has no significant negative influence on the thermal conductivity of the Nano-TIM material.

Fig. 3.7. Sample structures for (a) shear test and (b) thermal interface resistance measurement. Results of (c) shear test and (d) thermal interface resistance measurement. (From Paper A)

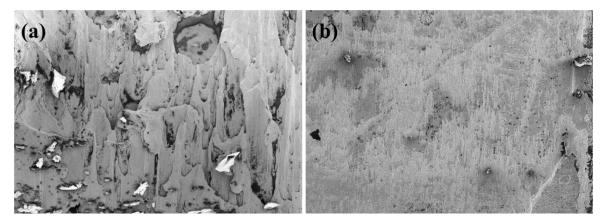

The dislocation motion in the Nano-TIM can be impeded by the silver-coated fibers limiting any crack initiation and propagation during the shear test and therefore increases the shear strength of the Nano-TIM compared to the pure indium TIM. To verify this hypothesis, the fracture surface after the shear test was also studied. The fracture surface of both samples shown in Fig. 3.8 are composed of dimples, but the

Fig. 3.8. Fracture surface of pure indium (a) and Nano-TIM (b) after shear test. (From paper A)

microstructure of the Nano-TIM is much finer than that of pure indium and with smaller dimple sizes. This fine microstructure of the fracture surfaces of Nano-TIM could be caused by the fiber network which separates the large indium matrix to small areas. This finer microstructure of fracture surface of Nano-TIM directly justified that the nanofibers do limit the crack initiation during the shear test.

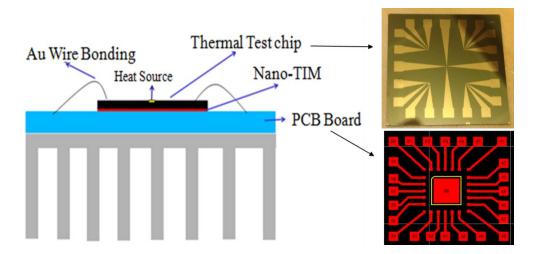

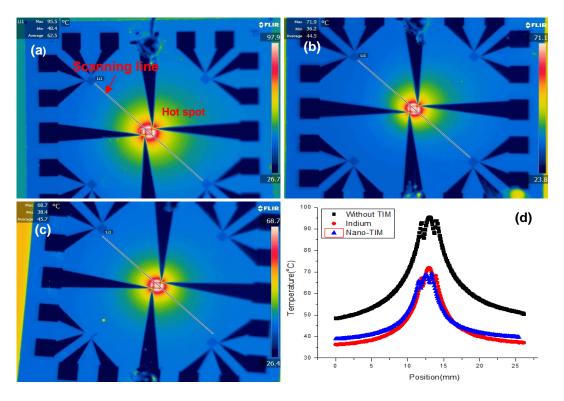

The heat dissipation effect of the Nano-TIM for die attach applications was investigated by using a thermal infrared camera. The test setup is shown in Fig. 3.9 where a hot spot power chip was attached onto a copper heat sink with TIM materials by using the same process as in the shear tests. An infrared camera was used to capture the temperature profiles of the power chip with 10 W loading. The results obtained are shown in Fig. 3.10. While the sample without any thermal interface material showed a much higher hot spot temperature (30 °C), the two samples with indium and the novel Nano-TIM showed almost the same thermal behavior as captured from the temperature profiles.

Fig. 3.9. Infrared camera setup for heat distribution analysis. (From paper A)

Fig. 3.10. IR test results: temperature distribution of the chip (a) without TIM, (b) with pure indium, and (c) with the Nano-TIM; (d) Temperature distribution along the line direction shown in Fig. 3.10 (a, b, c). (From Paper A)

#### 3.1.3 Reliability test of the Nano-TIM

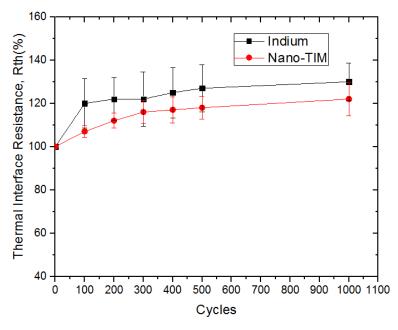

Fig. 3.11. Thermal interface resistance measurement after 100, 200, 300, 400, 500, and 1000 temperature cycles. (From paper A)

In order to evaluate the change in thermal performance and long-term reliability of the Nano-TIM, we carried out thermal cycling under harsh conditions while periodically monitoring the change in thermal resistance. The details of the thermal cycling are found in paper A, but the results after 100, 200, 300, 400, 500, and 1000 cycles are shown here in Fig. 3.11. The results presented in Fig. 3.11 gives a comparison between the pure indium TIM and the novel Nano-TIM. The thermal resistances of both materials increase with time in almost the same manner. This increase of the thermal interface resistance may be attributed to the formation of small cracks in the TIM structures caused by the harsh cycling conditions. Our conclusion is that the bonding quality of the Nano-TIM is as high as for a pure indium TIM even after 1000 cycles.

#### 3.2 CNT-Graphene hybrid material for heat dissipation application

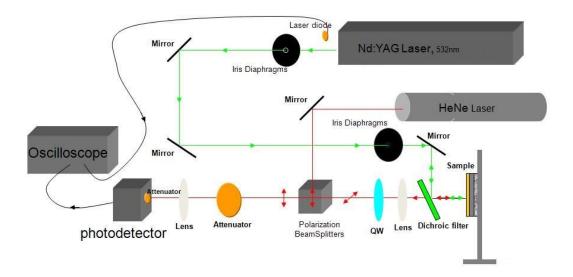

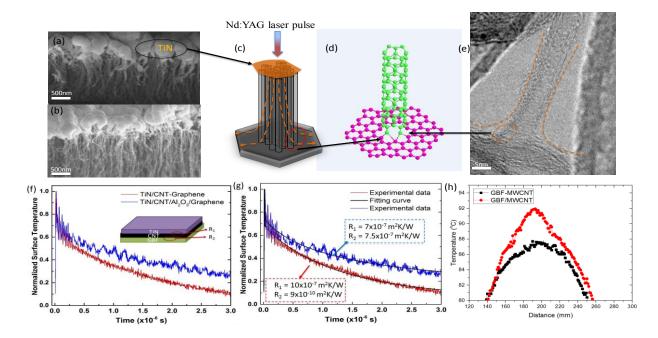

Carbon nanotubes (CNT) and graphene are the most representative carbon materials due to their extraordinary thermal performance [158]. The CNT high heat conductivity and graphene has made them hot subjects for research investigations in [159]-[168]. In particular, functionalized CNT arrays can effectively enhance the thermal transport at the interface between CNT and targeted surface and to some extent solve the problem of the small contact areas of individual CNT. However, this one dimensional (1D) thermal transfer cannot effectively decrease the heat density due to weak thermal conductivity and poor contact of CNT in the radial direction [169]. On the other hand, although 2D carbon materials like graphene can be able to dilute the heat density to a certain extent [170], graphene cannot provide as huge surface areas for convection as 1D CNT structures. Moreover, the cross-planar thermal conductivity of few-layer graphene is only around 0.7 W m<sup>-1</sup> K<sup>-1</sup> [171]. To curb these CNT drawbacks and graphene in heat dissipation applications, covalently bonded graphene-CNT hybrid structures have recently gained much attraction [122]–[127]. However, most investigations are just theoretical predictions of the potentially large heat dissipation capability of such materials [121][122]. Through molecular dynamics simulations (MDS) it has been shown that the thermal transition junction between the CNT and the graphene film dominate the thermal performance of such hybrid structure materials [124][165]. However, experimental investigations of the heat conduction between 1D CNT and 2D graphene films are still essentially absent due to the difficulties in both fabricating the material and experimentally measuring these contact resistances. Thus, few studies have experimentally demonstrated the heat dissipation performance of this kind of hybrid structures for thermal management applications. In this section, a freestanding hybrid material was developed for thermal management applications consisting of an array of multiwall carbon nanotubes (MWCNT) covalently bonded on the graphene based film. The pillared G-MWCNT hybrid material was obtained through chemical vapor deposition to grow MWCNT on the surface of the graphene. The atomic structure of covalently bond was analyzed by transmission electron microscopy (TEM). The thermal properties of the G-MWCNT structure have been characterized by the joule heating method [173]. In particular, the thermal junction resistance between the one-dimensional carbon nanotubes and the two-dimensional graphene was investigated through the pulsed photothermal reflectance (PPR) technique [230] [231]. Our results show that thermal junction resistance is effectively decreased when the two materials are joined with covalent bonds. In addition, we developed a thermal test chip to demonstrate the heat dissipation effect in the application.

## 3.2.1 Synthesis of graphene material

This section presented graphene synthesize on copper foil. In this fabrication,  $50 \,\mu m$  thick copper foils with a purity > 99.995% (from Advent research materials Ltd) were used as the catalyst substrates for graphene growth. Prior to loading the copper foil into the CVD chamber, the trimmed copper foil was cleaned by acetone and isopropanol to remove any organic contamination, whereafter the thin oxide surface layer was removed by acetic acid for 5 minutes.

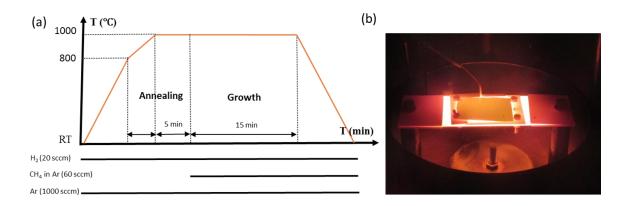

After the copper foil was suspended above the graphite heater held by an alumina frame, the bell jar was immediately pumped down to 0.1 mbar. The temperature of the graphite heater was ramped up to 800 °C at a rate of 300 °C/min in an argon or argon/hydrogen atmosphere. Hereafter, the automatic heating was stopped, and the temperature was slowly raised manually until hotspots, which indicated that the copper foil was very close to its melting point of 1060 °C. Once the hotspot was visible on the surface of the copper foil, the heating power was decreased and the temperature held at around 1000 °C. When the temperature stabilized, the copper foil was annealed for 5 minutes in hydrogen to completely remove any native oxide. Finally, the carbon feedstock, 5 % of methane in argon, was introduced into the chamber for initiating the growth. After completing growth, the chamber temperature was decreased to below 100 °C before the graphene film synthesized on the copper foil was taken out. A typical growth procedure with the two-step temperature ramp-up, a five minute anneal, a fifteen-minute growth, and the final chamber cool-down is shown in Fig. 3.12.

Fig. 3.12. The process flowchart for bilayer graphene growth (a) and a close-up of the experimental set-up during graphene growth on copper in the cold wall reactor (b). (From paper F)

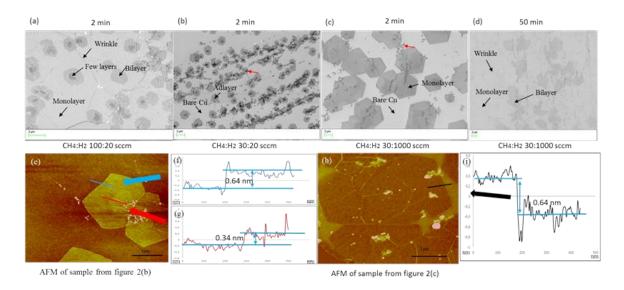

By using a low-pressure cold-wall CVD reactor, the deposition of graphene on copper foil was found not necessarily to be a self-limiting process. The appearance of graphene adlayers is independent of the ratio between the hydrogen and methane flow rates, but rather related to the growth time. As long as the growth time was long enough, graphene adlayers always formed as shown by the top row SEM micrographs in Fig. 3.13. The difference between the process runs was the ratio between the flow rates of methane and hydrogen, and the higher the hydrogen flow rate the longer before the adlayers appear. In Fig. 3.13 (a) and (b) adlayers were already visible after two minutes, while they were not visible for the high hydrogen flow rate shown in Fig. 3.13 (c). Here, it took 50 minutes before any adlayers appeared, as shown Fig. 3.13 (d), demonstrating that a high hydrogen flow hinders growth. In order to determine the exact number of graphene layers, samples (b) and (c) were transferred onto Si/SiO<sub>2</sub> substrates for AFM characterization. The result of the AFM analysis of sample (b) is shown in Fig. 3.13 (e), (f) and (g), while the result of sample (c) is shown in Fig. 3.13 (h) and (i). From Fig. 3.13 (i) the height difference between first layer graphene and bare silicon dioxide surface is found to be around 0.64 nm, which confirms the existence of patches of monolayer graphene [176]. From Fig. 3.13 (f) and (g) the 0.64 nm monolayer thickness is confirmed along the blue line in figure (e), while an adlayer thickness of 0.34 nm is confirmed along the red line in Fig. 3.13 (e).

Based on the AFM analysis of the surface topography, the difference between bare copper, monolayer and bilayer graphene could be distinguished from the contrast differences on the SEM micrographs as shown on the top row of Fig. 3.13. Graphene wrinkles were also observed, and we believe they are formed during cooling due to the different thermal expansion coefficients of graphene and copper [177]. However, no wrinkles can be observed on the bare copper area, so this feature can be used to indicate whether the first graphene layer covers the entire copper surface. As shown in Fig. 3.13 (b) and (e) after two minutes of

graphene growth, some carbon clusters (indicated by red arrows) were observed. However, these clusters gradually disappeared as the growth process continued. Bointon et al. [178] claimed that, in cold-wall CVD, graphene growth is initialized from coated carbon films, and that these carbon films progressively evolve into islands, or patches, of graphene. Even though our observation of carbon clusters is consistent with the findings of Bointon et al., graphene synthesis still follows the common stages of nucleation, expansion and coalescence.

Fig. 3.13. SEM micrographs of graphene on copper foil samples (top row), (a - d), AFM height estimations across mono- and bilayer graphene edges after patches being transferred to  $SiO_2/Si$  substrates (bottom row), (e - i). (From paper F)

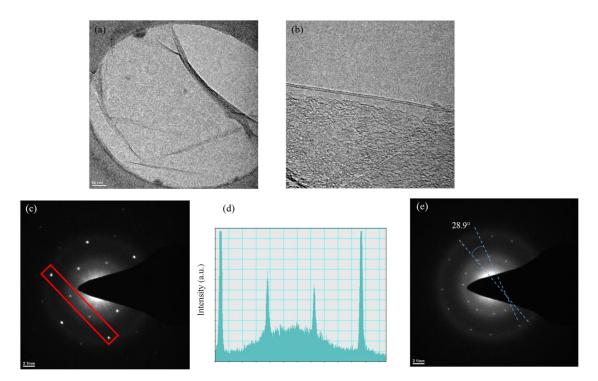

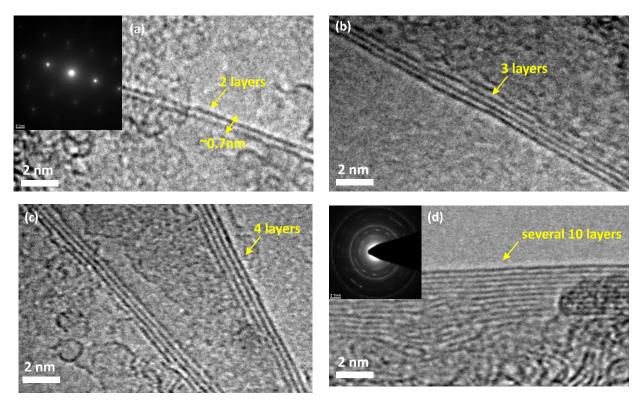

TEM observations and selected area electron diffraction (SEAD) examinations were further carried out to determine the thickness and evaluate the quality of as-grown graphene sample from Fig. 3.14. Folded graphene layers can be clearly observed suspended above the copper grid under low magnification as Fig. 3.14 (a) indicates. While a bilayer graphene edge can be identified from the high magnification TEM image shown in Fig. 3.14 (b), the SEAD pattern shown in Fig. 3.14 (c) reveals a set of 6-fold symmetry arrangement of carbon atoms. In addition, the intensities of outer diffraction are twice as strong as that of the inner diffraction as Fig. 3.14 (d) displays, indicating the formation of AB-stacked bilayer graphene. These observations are in line with the results of the Raman spectroscopy. It should be noted that the SEAD pattern of mis-oriented bilayer graphene was also occasionally observed, showing two sets of diffraction spots with a 28.9° rotation as Fig. 3.14 (e) shows. It also should be noted that the mis-oriented bilayer graphene with a twist angle 28.9° was the most often observed type in the measurement.

Fig. 3.14. Bright field (a) low-resolution TEM micrograph of graphene on copper grid, and (b) high-resolution TEM micrograph of bilayer graphene. (c) Typical SEAD patterns of the as-grown bilayer graphene shown in (a). (d) Intensity profiles along the selected spots in (c). (e) SEAD patterns of the mis-oriented bilayer graphene with a 28.9° rotation. (From paper F)

## 3.2.2 Synthesis of Graphene-CNT hybrid material

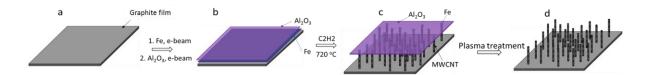

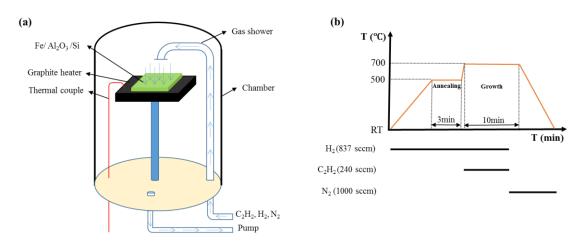

After investigating graphene growth, this section demonstrates CNT growth on the graphene by CVD method. A schematic illustration of the synthesis process of this hybrid material is shown in Fig. 3.15. The starting material obtained from the Panasonic Co. was a graphite film consisting of a number of stacked layers of graphene. The surface of this graphite film was prepared for CNT growth by deposition of a 2 nm iron film and on top of that a 3 nm thick layer of alumina (Al<sub>2</sub>O<sub>3</sub>) was deposited in situ by electron-beam evaporation. Here, the iron served as a catalyst for MWCNT growth while the alumina layer served to facilitate the formation of top grown MWCNT [124]. MWCNT array were synthesized on the surface of the graphene film through CVD. After loading the film the chamber was pumped down to below 0.1 mbar before an 837 sccm flow of H<sub>2</sub> was input. Thereafter, the substrate heater was ramped up to 500 °C at a rate of 300 °C/min, and when this intermediate temperature was reached the heater was maintained at this temperature for 3 minutes for reducing the catalyst [179]. The heater temperature was then rapidly increased to 720°C, while carbon feedstock acetylene at a rate of 240 sccm was introduced into the chamber for

several minutes for allowing the CNT array to grow from the surface of the G film. Since the process is a top-growth process, the iron catalyst and the 3 nm Al<sub>2</sub>O<sub>3</sub> layer are separated from the surface of the film during growth ending up at the top of the MWCNT array. A plasma etch treatment was used to remove the Al<sub>2</sub>O<sub>3</sub> layer because of its poor thermal conductance. After etch, a freestanding hybrid film with G-CNT covalent bond was obtained.

Fig. 3.15. Schematic illustration of the synthesis of the G-MWCNT hybrid material. (a) The graphite film was starting material. (b) Surface of the film covered with thin iron and alumina layers in preparation for CNT growth. (c) Growth of a vertical multiwall CNT array from the surface of the film lifting the iron and alumina layers. (d) Top alumina layer removed by plasma etch. (From paper G)

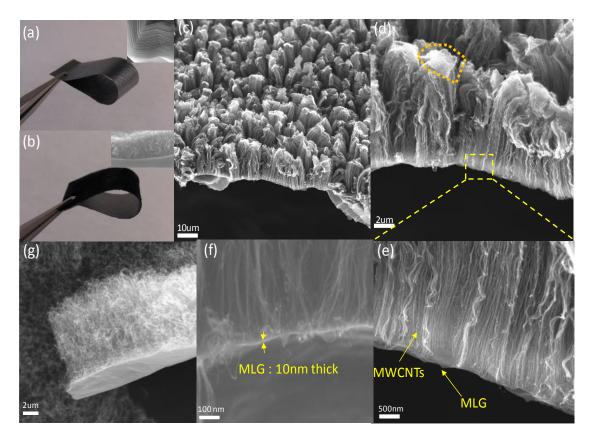

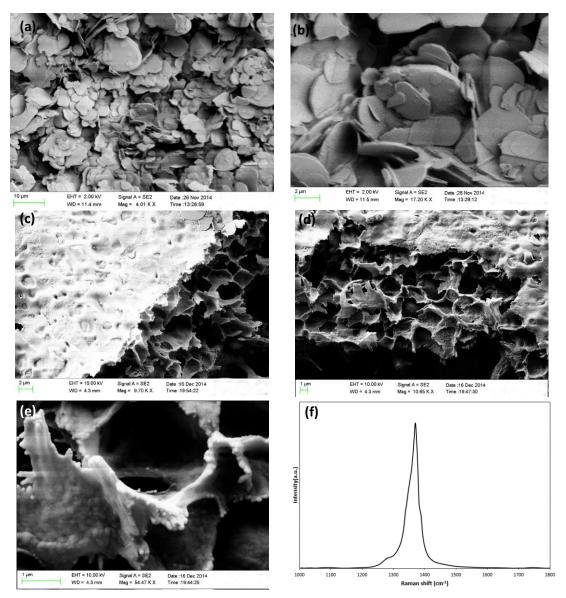

The freestanding G-MWCNT hybrid film prepared as described in Fig. 3.15 consists of an MWCNT array covering the surface of the film. The quality and structure of the MWCNT array is examined using SEM. Some of the resulting SEM images are shown in Fig. 3.16. Fig. 3.16(a) shows the flexible G film before CNT growth, while the same film after MWCNT growth is shown in Fig. 3.16(b). The color change of the top surface due to the uniform MWCNT array is clearly observed. In the SEM inset of Fig. 3.16(a) the multilayer graphene structure is visible, while in the SEM inset of Fig. 3.16(b) the vertically aligned CNT are observed. A top view of the MWCNT array is shown in the SEM image of Fig. 3.16(c). The top view shows that the MWCNT carpet was split into different islands, hundreds of micrometer in size, which is not different from normal MWCNT growth [180]. The gap between islands was formed already in the initial stage when the Al<sub>2</sub>O<sub>3</sub> layer was split so that the carbon feedstock gas could reach the iron catalyst. From the heat dissipation perspective, this kind of MWCNT porous structure is preferred to enhance the thermal convection effect. Furthermore, a plasma etching treatment was introduced to remove the thin Al<sub>2</sub>O<sub>3</sub> layer to further facilitate the heat convection as shown in Fig. 3.16(g). In order to check the quality of the MWCNTs and their interface between the G film and MWCNT, high-resolution SEM pictures are captured, as shown in Fig. 3.16(d-f). From the cross-sectional view of the MWCNT shown in Fig. 3.16 (d) the MWCNT height grown on top of the G film could be estimated to above 10 µm. In addition, most of the CNT appear vertically aligned. A number of bright areas can be observed, some of the marked by an orange dish line, and they indicate the Al<sub>2</sub>O<sub>3</sub> layer remaining on top of the catalyst according to the tip growth 'Odako' mechanism [181]. Since the MWCNT form by tip growth, the iron catalyst covered by the Al<sub>2</sub>O<sub>3</sub> layer was lifted up by MWCNT during the growth. We believe this indirectly prove that the MWCNT have

a stable and strong bonding to the multilayer graphene at the bottom. Without such strong bonds to the G film, the CNT would easily lay down horizontally instead of the vertically aligned growth shown in Fig. 3.16(e).

Fig. 3.16. SEM characterization of MWCNT grown on G. (a) The freestanding GBF with stacked layer structure. (b) The freestanding GBF-CNT hybrid film. (c) The overall CNT-G hybrid structure from top view was captured by SEM. (d-f) Several ten micrometer thick of vertically aligned MWCNT directly grow on the tens of nanometer thick G. 3 nm thick alumina layer was lifted up by CNT in the orange marked area. (g) The alumina layer lifted up by CNT was removed using plasma. (From paper G)

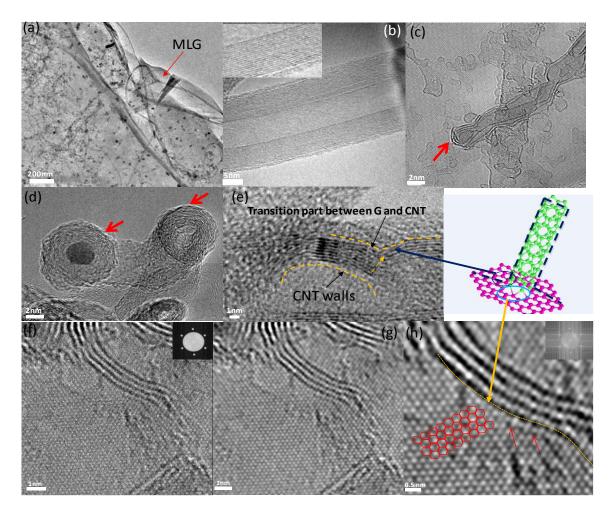

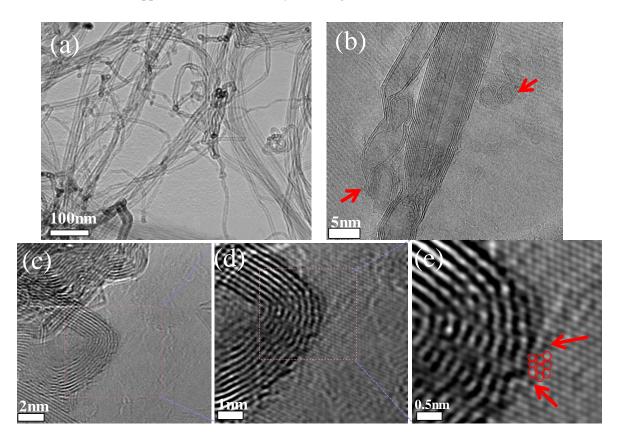

In order to investigate the junction structure between CNTs and graphene, the G-MWCNT material was analyzed by TEM. Some detailed results of typical CNTs grown under these conditions are shown in Fig. 3.17. In Fig. 3.17(a), a number of randomly distributed MWCNTs grown on the film can be observed. Moreover, most CNTs are multiwall structures with the diameter of 10 to 20 nm, as shown in Fig. 3.17 (b). Compared to SWCNT-monolayer graphene synthesized in [124], multilayer graphene seems tend to grow multiwall CNT structure. In addition, a number of multiwall ring-like structures can be observed on the graphene film as shown in Fig. 3.17(c) and (d). According to previous reports [25][40], these ring-like structures is an indication of covalent bonds between the CNTs and the multilayer graphene film. Besides

## Chapter 3 Carbon Based Materials for Thermal Management application in 3D IC packaging

that, the lateral layers inside the root junction of the CNT was also detected in Fig. 3.17(c), which implied that the CNTs are open-ended at the bottom. This result is consistent with theoretical prediction [23][26][41] that one indication of forming covalent bonds with graphene was open-ended CNT at the bottom. Furthermore, the cross-sectional views in Fig. 3.17(e) show how the CNTs have grown from the surface of the multilayer graphene film with covalent bonds. In Fig. 3.17(e) the yellow dashed lines mark the direction of the carbon shells, while the yellow arrow shows the transition shells from the CNTs to the graphene. This indicate that the outermost several shells of CNT is covalently bonded to the multilayer graphene plane. In order to further observe the detailed atomic structure of the MWCNT and planar graphene transformations, high-resolution TEM image, Fig. 3.17(f), was FFT treated to obtain atomic structure as showed in Fig. 3.17(g) and (h). It can be seen that each white dot representing an aromatic ring was orderly arrayed until the walls of MWCNT. The FFT pattern in the upper-right inset shows the six-fold crystal symmetry structure of graphene. However, there some aromatic rings nearby the shells of CNTs, as marked in red arrow, were distorted. That could be due to their out-of-plane orientations from 2D planar graphene. These distorted rings could be the seven-edge rings as reported by previous theoretical work [23][26][41] to form stable G-CNT carbon structure. Taken all the indications together, the graphene and CNTs hybrid structure through covalent bonds was confirmed.

Fig. 3.17. TEM characterization of MWCNT grown on G film. (a) It shows the overall structure of G with MWCNT. (b) This image shows the multiwall structure and diameter of one single MWCNT grown on the G. (c) It characterized the MWCNT root region as marked by red arrow. Additional shells are found on the root. (d) This shows the ring like nanostructure of MWCNT grown on the G. (e) The continuous walls from a MWCNT to graphene was detected with high resolution TEM. (f) The raw high-resolution TEM images show the CNT-G junction. (g,h) The high-resolution images after applying a filter to the FFT of raw image (f). (From paper G)

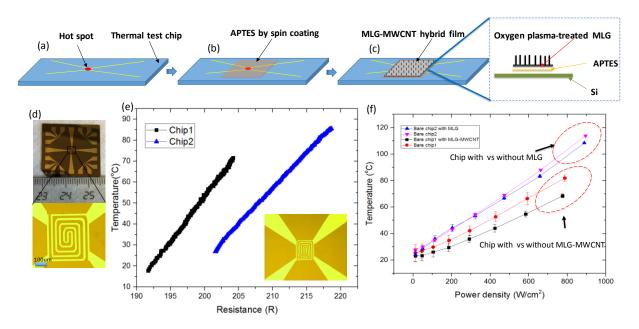

# 3.2.3 Thermal Performance characterization of CNT-Graphene hybrid material

To evaluate the thermal performance of the G-MWCNT material acting as a heat sink, the test structure described in Fig. 3.18 was used. First, the test chip was calibrated to obtain the temperature versus resistance calibration curves. Calibration was carefully done with the test chip placed in a thermal chamber and its resistance measured at a number of temperature settings after temperature steady state was reached. As shown in Fig. 3.18(e) the relationship between temperature and resistance shows good linearity, with a

## Chapter 3 Carbon Based Materials for Thermal Management application in 3D IC packaging

temperature sensitivity coefficient of about 4  ${}^{\circ}$ C/ $\Omega$ . By monitoring the resistance versus the power, dissipated in the hotspot resistor, temperature versus power density curves can be obtained and the heat dissipation performance of the heat sink material be evaluated.

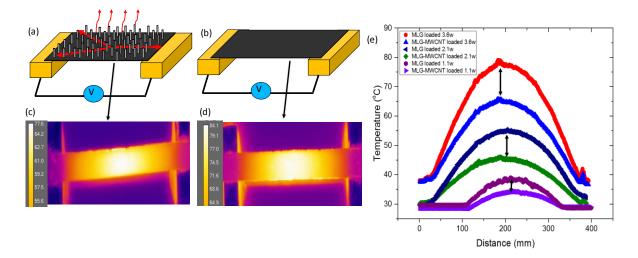

First of all the hotspot temperature curves were plotted for bare chips. As shown in Fig. 3.18(f) the hotspot temperature increased from room temperature to above 100°C when the power density was increased from 0 to 900 W/cm². As a reference, chip one was covered with G films without MWCNT and the chip two was covered with the G-MWCNT hybrid material. The application of both materials had a clear cooling effect as shown in the graph of Fig. 3.18(f). As a comparison between the two materials with and without MWCNT, it can be monitored that at a power density of 800 W/cm² that for the chips without CNT the temperature decreased 6 °C and for the chips with the G-MWCNT hybrid material the temperature decreased 10 °C. These experiments show that the G film serves to effectively spread the thermal energy from the hotspot due to its high lateral thermal conductivity. However, the surface area is still limiting the heat dissipation by convection to the ambient. In contrast, the G-MWCNT structure with vertically aligned CNT is shown to effectively enhance heat convection since the numerous carbon nanotubes function as micro heat sinks improving the heat dissipation.

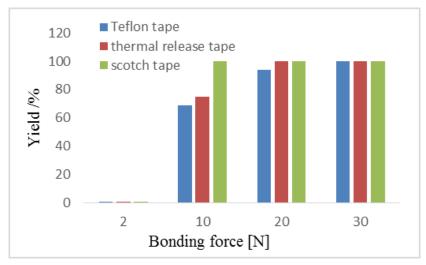

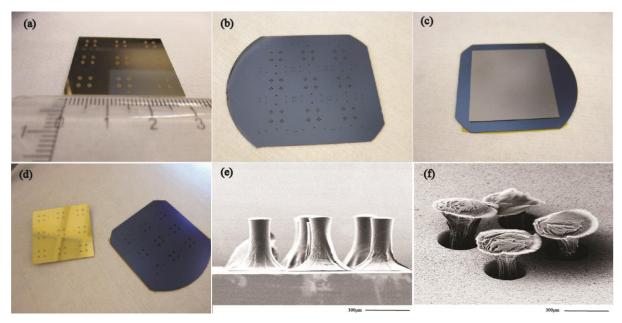

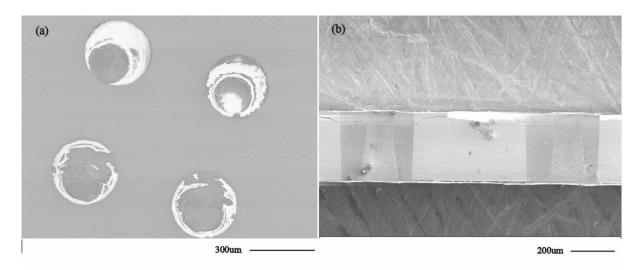

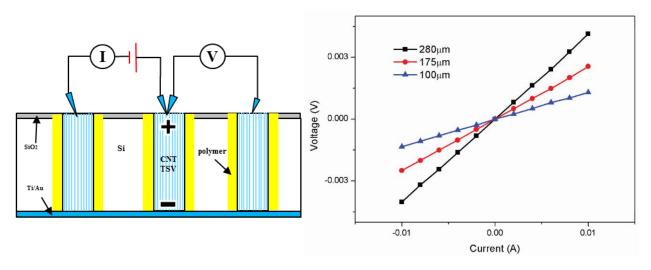

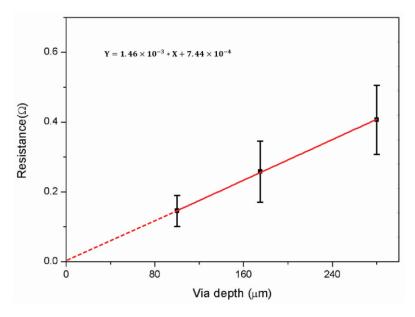

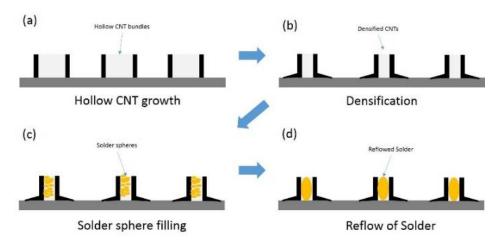

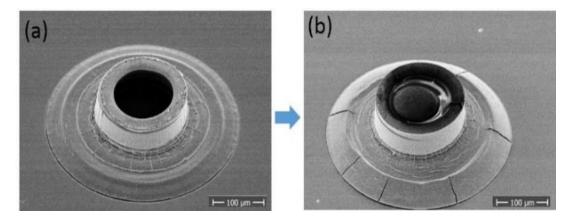

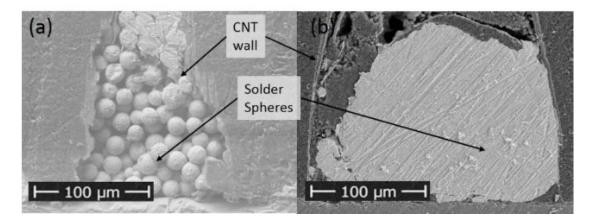

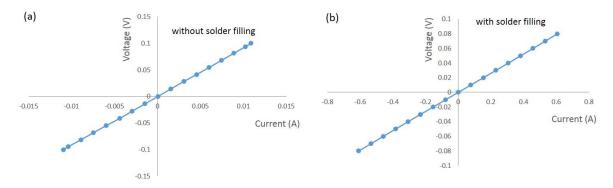

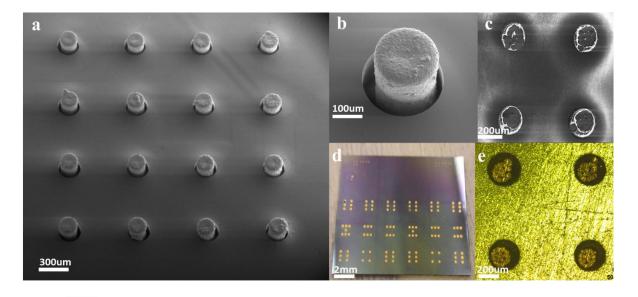

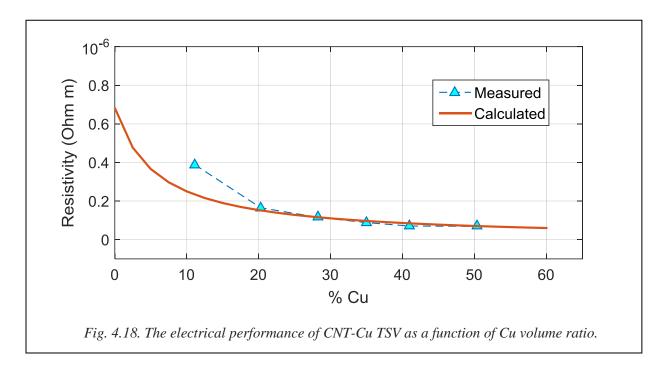

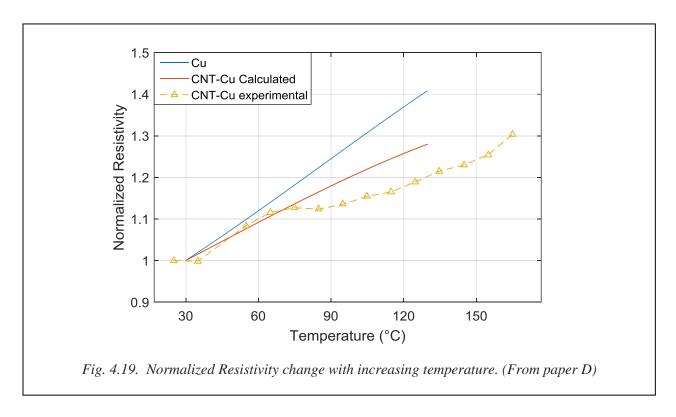

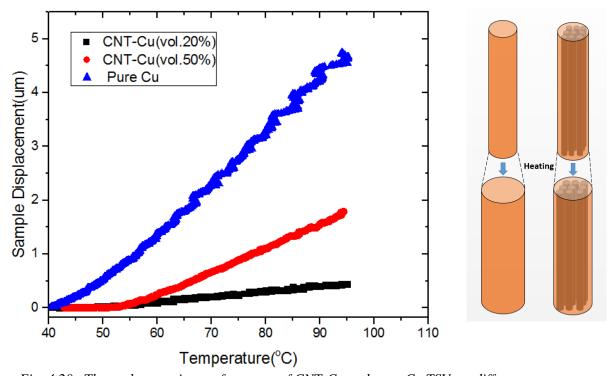

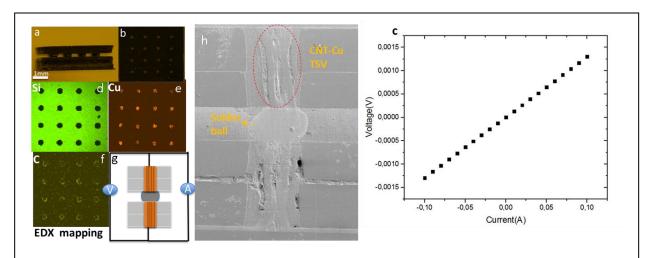

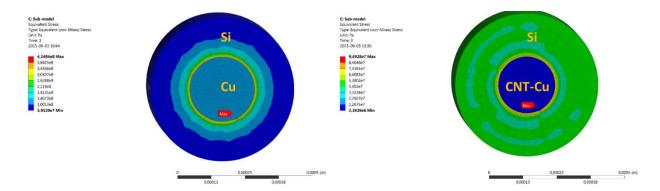

Fig. 3.18. Heat dissipation capability was demonstrated through thermal test chip. (a) Thermal test chip with the hot spot was fabricated through a series of lithography process. (b) A thin layer of APTES was spin-coated on the central part of chip. (c) The G-MWCNT film was spin-coated on the top of hot spot via APTES for improving thermal boundary resistance. (d) The thermal test chip has a micro-heater&sensor to be seen as a hot spot in the central part of chip. (e) The calibration curve of thermal test chips shows a linear relationship between resistance and temperature. The inset image of figure (e) is the hot spot structure from top view. (f) The temperature of hot spot under different power density was respectively measured to make a comparison between chips with and without G and between chips with and without G-CNT. (From paper G)