# Verifying the Logical Correctness of a Train Station

Master's thesis in Systems, Control and Mechatronics

# BERIT-JANICE HÄRLE and DANIEL LOVÉN ÖBERG

EX046/2016

Department of Signals and Systems CHALMERS UNIVERSITY OF TECHNOLOGY Gothenburg, Sweden 2016

MASTER'S THESIS EX046/2016

# Verifying the Logical Correctness of a Train Station

BERIT-JANICE HÄRLE and DANIEL LOVÉN ÖBERG

Department of Signals and Systems Division of Automation Control CHALMERS UNIVERSITY OF TECHNOLOGY Gothenburg, Sweden 2016

# Verifying the Logical Correctness of a Train Station BERIT-JANICE HÄRLE and DANIEL LOVÉN ÖBERG

#### © BERIT-JANICE HÄRLE and DANIEL LOVÉN ÖBERG, 2016.

Supervisor: Martin Fabian, Department of Signals and Systems Examiner: Martin Fabian, Department of Signals and Systems

Master's Thesis 2016:EXO46/2016 Department of Signals and Systems Division of Automation Control Chalmers University of Technology SE-412 96 Gothenburg Telephone +46 31 772 1000

Cover: Satellite picture of Gothenburg train station [1]

Logical Verification of a Train Station Berit-Janice Härle Daniel Lovén-Öberg Department of Signals and Systems Chalmers University of Technology

# Abstract

Trains offer low emissions and energy efficient transportation of passengers and goods, and are therefore essential to the infrastructure of the country. For the safety of the passengers, amongst others, it is necessary to control the trains to avoid crashes. By using a signaling system (European Rail Traffic Management System), it is possible to keep track of the train locations and react to anomalies. The railway switches and the behaviors of the trains can be modelled and then formally verified for safety. The goal of this work is to use extended finite automata to verify the logical correctness of the Gothenburg Central train station. A model is created in Supremica and UPPAAL, both tools that can verify discrete event systems. The model is then verified to ensure absence of collisions while guaranteeing that the trains can always reach their designated platforms. Initially, a simplified model is created to test the two tools, and to define properties to achieve successful verification. For larger models, the state space becomes too large for UPPAAL that suffers from memory limitations due to its 32-bit implementation. Therefore, Supremica, with its 64-bits hardware, is used to successfully verify the safety of the train station. This report also includes extensive information for both tools.

Keywords: Verification, Automata, Logical Correctness, Railways, Train Station, Safety

# Sammanfattning

Tåg är ett miljövänligt och och energieffektivt transportsätt för passagerare och varor. Det är därför en viktig del av infrastrukturen i ett land. För passagerarnas säkerhet är det nödvändigt att reglera tågen för att undvika kollisioner. Genom att använda ett signalsystem (European Rail Traffic Management System) är det möjligt att hålla reda på tågens position och reagera på avvikelser. Järnvägsväxlarnas och tågens beteende kan modelleras och sedan verifieras. Målet med rapporten är att använda sig av ändliga tillståndsmaskiner till att verifiera den logiska korrektheten av Göteborgs centralstation. En modell skapas i Supremica och UPPAAL, båda verktyg för att verifiera diskreta händelsesystem. Modellen är sedan verifierad för att undvika kollisioner och samtidigt garantera att ett tåg alltid når sin angivna plattform. Först skapas en mindre modell för att testa de båda verktygen och olika idéer över hur man kan nå en lyckad verifiering. För större modeller blir tillståndsrummet för stort för UPPAAL som får minnesproblem då det endast kan utnyttja på 32-bitar. Därför används Supremica till att framgångsrikt verifiera säkerheten för tågstationen. Rapporten innehåller också omfattande information om båda programmen.

Keywords: Verifiering, Tillståndsmaskin, Logisk Korrekthet, Järnvägar, Tågstation, Säkerhet

# Acknowledgements

We would like to thank our supervisor and examiner Martin Fabian for his support, motivation and always having an open ear. His fast responses to e-mails and his availability even for emergencies on the weekend is impressive and something we are extremely thankful for. Without Martin, the thesis would not have been nearly as successful.

Also, thank you to all of our families and friends for their understanding and mental support.

Berit-Janice Härle and Daniel Lovén Öberg, Gothenburg, June 2016

# Contents

| List of Figures xi |                                 |                                                                               |                                                                                                                                                  |                                             |  |  |

|--------------------|---------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|

| Lis                | st of                           | Tables                                                                        | 6                                                                                                                                                | xv                                          |  |  |

| 1                  | <b>INT</b><br>1.1<br>1.2<br>1.3 | Scope<br>Related                                                              | J <b>CTION</b><br>d Research                                                                                                                     | <b>1</b><br>1<br>2<br>2                     |  |  |

| 2                  | <b>THI</b><br>2.1               |                                                                               | <b>FICAL BACKGROUND</b> mentals of Railways         European Train Control System         Railway Switches         Train Station         2.1.3.1 | <b>3</b><br>3<br>4<br>5<br>5                |  |  |

|                    | 2.2                             | Autom<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.2.8 |                                                                                                                                                  | 6<br>7<br>7<br>8<br>8<br>8<br>9<br>9        |  |  |

|                    | 2.3                             | -                                                                             | I VerificationThe State Space Explosion ProblemVerification Algorithms2.3.2.1Monolithic2.3.2.2Compositional2.3.2.3Partial OrderTemporal Logic    | 9<br>10<br>10<br>10<br>10<br>10<br>10<br>11 |  |  |

| 3                  | <b>TOC</b><br>3.1               |                                                                               | nica                                                                                                                                             | <b>13</b><br>13<br>14<br>14<br>14           |  |  |

|   |                  | $3.1.2 \\ 3.1.3$                                                                        | Verify Menu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16<br>16                                                                                                                                                                           |

|---|------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                  | 3.1.4                                                                                   | Analyser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17                                                                                                                                                                                 |

|   |                  | 0.1.1                                                                                   | $3.1.4.1$ Verify $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17                                                                                                                                                                                 |

|   |                  |                                                                                         | 3.1.4.2 Find States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                                                                                                                                                 |

|   |                  | 3.1.5                                                                                   | Opening Files in Other Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18                                                                                                                                                                                 |

|   |                  | 3.1.6                                                                                   | Common Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18                                                                                                                                                                                 |

|   |                  |                                                                                         | 3.1.6.1 Increasing the Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18                                                                                                                                                                                 |

|   |                  |                                                                                         | 3.1.6.2 (Non-)Deterministic Variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18                                                                                                                                                                                 |

|   |                  |                                                                                         | 3.1.6.3 "Event removed due to Optimisation"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19                                                                                                                                                                                 |

|   |                  |                                                                                         | 3.1.6.4 "State encoding requires $x$ bits, 64 is the maximum!"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19                                                                                                                                                                                 |

|   | 3.2              | UPPA                                                                                    | AL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                                                                                                                                                 |

|   |                  | 3.2.1                                                                                   | Editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20                                                                                                                                                                                 |

|   |                  |                                                                                         | 3.2.1.1 Declarations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21                                                                                                                                                                                 |

|   |                  |                                                                                         | 3.2.1.2 Templates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22                                                                                                                                                                                 |

|   |                  |                                                                                         | 3.2.1.3 System Declarations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24                                                                                                                                                                                 |

|   |                  | 3.2.2                                                                                   | Simulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25                                                                                                                                                                                 |

|   |                  | $3.2.3 \\ 3.2.4$                                                                        | Verifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26                                                                                                                                                                                 |

|   |                  | 3.2.4<br>3.2.5                                                                          | Memory Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28<br>28                                                                                                                                                                           |

|   |                  |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20                                                                                                                                                                                 |

|   | 33               |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28                                                                                                                                                                                 |

|   | 3.3              |                                                                                         | Intentory instacts   Intentory instacts     Ional Software Tools   Intentory instacts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28                                                                                                                                                                                 |

| 4 |                  |                                                                                         | onal Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28<br><b>31</b>                                                                                                                                                                    |

| 4 |                  | Additi<br>DELL                                                                          | onal Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                    |

| 4 | мо               | Additi<br>DELL                                                                          | onal Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>31</b><br>31<br>32                                                                                                                                                              |

| 4 | <b>MO</b><br>4.1 | Additi<br>DELL<br>Simpli                                                                | onal Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>31</b><br>31<br>32<br>32                                                                                                                                                        |

| 4 | <b>MO</b><br>4.1 | Additi<br>DELL<br>Simpli<br>UPPA                                                        | onal Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>31</b><br>32<br>32<br>32                                                                                                                                                        |

| 4 | <b>MO</b><br>4.1 | Additi<br>DELL<br>Simpli<br>UPPA                                                        | inng         fication         AL         Approach 1: Standard approach         4.2.1.1         Switches and Platforms         4.2.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>31</b><br>32<br>32<br>32<br>33                                                                                                                                                  |

| 4 | <b>MO</b><br>4.1 | Additi<br>DELL<br>Simpli<br>UPPA                                                        | inal Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ul> <li><b>31</b></li> <li>32</li> <li>32</li> <li>32</li> <li>33</li> <li>34</li> </ul>                                                                                          |

| 4 | <b>MO</b><br>4.1 | Additi<br>DELL<br>Simpli<br>UPPA                                                        | onal Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ul> <li><b>31</b></li> <li>32</li> <li>32</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> </ul>                                                                              |

| 4 | <b>MO</b><br>4.1 | Additi<br>DELL<br>Simpli<br>UPPA<br>4.2.1                                               | inal Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ul> <li><b>31</b></li> <li>32</li> <li>32</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>38</li> </ul>                                                                  |

| 4 | <b>MO</b><br>4.1 | Additi<br>DELL<br>Simpli<br>UPPA                                                        | ional Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li><b>31</b></li> <li>32</li> <li>32</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>38</li> <li>39</li> </ul>                                                      |

| 4 | <b>MO</b><br>4.1 | Additi<br>DELL<br>Simpli<br>UPPA<br>4.2.1                                               | inal Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>31</b><br>32<br>32<br>33<br>34<br>35<br>38<br>39<br>39                                                                                                                          |

| 4 | MO<br>4.1<br>4.2 | Additi<br>DELL<br>Simpli<br>UPPA<br>4.2.1                                               | ional Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>31</b><br>32<br>32<br>33<br>34<br>35<br>38<br>39<br>39<br>43                                                                                                                    |

| 4 | <b>MO</b><br>4.1 | Additi<br>DELL<br>Simpli<br>UPPA<br>4.2.1<br>4.2.2<br>Supren                            | inal Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>31</b><br>32<br>32<br>33<br>34<br>35<br>38<br>39<br>39                                                                                                                          |

| 4 | MO<br>4.1<br>4.2 | Additi<br>DELL<br>Simpli<br>UPPA<br>4.2.1                                               | onal Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>31</b><br>32<br>32<br>33<br>34<br>35<br>38<br>39<br>39<br>43                                                                                                                    |

| 4 | MO<br>4.1<br>4.2 | Additi<br>DELL<br>Simpli<br>UPPA<br>4.2.1<br>4.2.2<br>Supren                            | inal Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>31</b><br>32<br>32<br>33<br>34<br>35<br>38<br>39<br>39<br>43<br>47                                                                                                              |

| 4 | MO<br>4.1<br>4.2 | Additi<br>DELL<br>Simpli<br>UPPA<br>4.2.1<br>4.2.2<br>Supret<br>4.3.1                   | onal Software Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>31</b><br>32<br>32<br>33<br>34<br>35<br>38<br>39<br>39<br>43<br>47                                                                                                              |

| 4 | MO<br>4.1<br>4.2 | Additi<br>DELL<br>Simpli<br>UPPA<br>4.2.1<br>4.2.2<br>Supret<br>4.3.1                   | ional Software Tools         ING         fication         AL         Approach 1: Standard approach         4.2.1.1         Switches and Platforms         4.2.1.2         The Trainmaker         4.2.1.3         Specification         4.2.1.4         Model of the Train Station         4.2.1.5         Reducing the Model of the Train Station         4.2.2.1         Request and RequestOut         4.2.2.2         Model of the Train Station         4.2.2.1         Request and RequestOut         4.2.2.2         Model of the Train Station         Approach 1: Without Variables and with a Model of the Train Station         Approach 2: Without Variables and no Model of the Train Station | <ul> <li>31</li> <li>32</li> <li>32</li> <li>32</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>38</li> <li>39</li> <li>43</li> <li>47</li> <li>47</li> <li>50</li> </ul> |

| 4 | MO<br>4.1<br>4.2 | Additi<br>DELL<br>Simpli<br>UPPA<br>4.2.1<br>4.2.2<br>Supret<br>4.3.1<br>4.3.2          | ional Software Tools         ING         fication         AL         Approach 1: Standard approach         4.2.1.1         Switches and Platforms         4.2.1.2         The Trainmaker         4.2.1.3         Specification         4.2.1.4         Model of the Train Station         4.2.1.5         Reducing the Model of the Train Station         4.2.2.1         Request and RequestOut         4.2.2.2         Model of the Train Station         Approach 1: Without Variables and with a Model of the Train         Station         Approach 2: Without Variables and no Model of the Train                                                                                                   | <ul> <li>31</li> <li>32</li> <li>32</li> <li>32</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>38</li> <li>39</li> <li>43</li> <li>47</li> <li>47</li> <li>50</li> </ul> |

| 4 | MO<br>4.1<br>4.2 | Additi<br>DELL<br>Simpli<br>UPPA<br>4.2.1<br>4.2.2<br>Supret<br>4.3.1<br>4.3.2<br>4.3.3 | ional Software Tools         ING         fication         AL         Approach 1: Standard approach         4.2.1.1         Switches and Platforms         4.2.1.2         The Trainmaker         4.2.1.3         Specification         4.2.1.4         Model of the Train Station         4.2.1.5         Reducing the Model of the Train Station         4.2.2.1         Request and RequestOut         4.2.2.2         Model of the Train Station         mica         Approach 1: Without Variables and with a Model of the Train Station         Approach 2: Without Variables and no Model of the Train Station         Approach 3: With Variables and no Model of the Train Station                 | <ul> <li>31</li> <li>32</li> <li>32</li> <li>32</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>38</li> <li>39</li> <li>43</li> <li>47</li> <li>47</li> <li>50</li> </ul> |

|              |       | 5.1.1    | Deadlock verification                                                                                | 59 |

|--------------|-------|----------|------------------------------------------------------------------------------------------------------|----|

|              |       | 5.1.2    | Avoid same state verification                                                                        | 59 |

|              |       | 5.1.3    | Platform/Line chosen is reached                                                                      | 60 |

|              | 5.2   | Supren   | nica                                                                                                 | 62 |

|              |       | 5.2.1    | Deadlock verification                                                                                | 62 |

|              |       | 5.2.2    | Avoid same state verification                                                                        | 62 |

|              |       |          | 5.2.2.1 Alternative $1 \ldots \ldots$ | 62 |

|              |       |          | 5.2.2.2 Alternative $2 \ldots \ldots$ | 63 |

|              |       | 5.2.3    | Platform/Line chosen is reached                                                                      | 64 |

|              | 5.3   | Result   | s                                                                                                    | 66 |

|              |       | 5.3.1    | UPPAAL                                                                                               | 66 |

|              |       | 5.3.2    | Supremica                                                                                            | 67 |

| 6            | GO    | THEN     | BURG TRAIN STATION                                                                                   | 69 |

|              | 6.1   | Modell   | ling                                                                                                 | 69 |

|              | 6.2   | Verifica | ation                                                                                                | 69 |

|              |       | 6.2.1    | Deadlock                                                                                             | 69 |

|              |       | 6.2.2    | Only one train can claim a switch/platform                                                           | 69 |

|              |       | 6.2.3    | The trains will not diverge from its route                                                           | 70 |

|              | 6.3   | Result   | S                                                                                                    | 70 |

| 7            | COI   | NCLUS    | SION                                                                                                 | 71 |

| 8            | FUI   | ГURE     | WORK                                                                                                 | 73 |

| Bi           | bliog | raphy    |                                                                                                      | 75 |

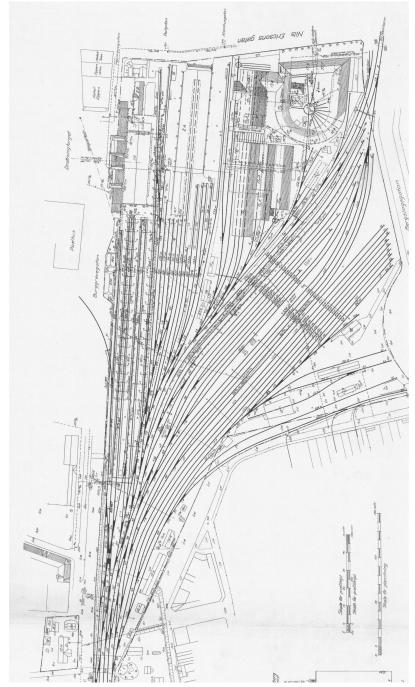

| $\mathbf{A}$ | Old   | Map      |                                                                                                      | I  |

# List of Figures

| 2.1  | ETCS components [2]. $\ldots$                                         | 3  |

|------|-----------------------------------------------------------------------|----|

| 2.2  | ETCS functionality [2]                                                | 4  |

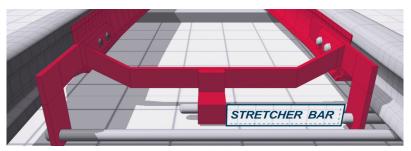

| 2.3  | An overview of a railroad switch [3]                                  | 4  |

| 2.4  | Closeup of the stretcher bar $[3]$                                    | 5  |

| 2.5  | Pointblade [3]                                                        | 5  |

| 2.6  | Stockrail [3]                                                         | 5  |

| 2.7  | Gothenburg train station $[1]$                                        | 6  |

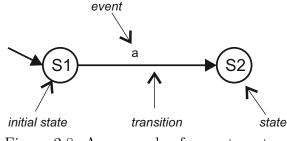

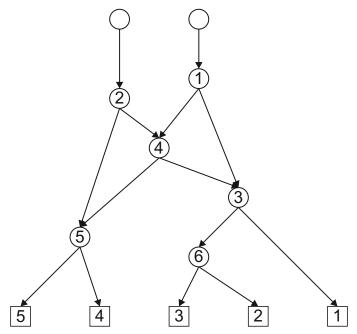

| 2.8  | An example of an automaton.                                           | 6  |

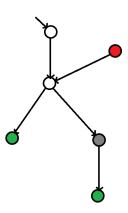

| 2.9  | Non-reachable (red) and non-coreachable (green) states                | 7  |

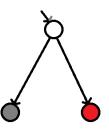

| 2.10 | Automaton with an unwanted deadlock (red)                             | 8  |

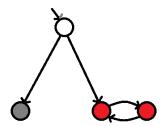

| 2.11 | Automaton with a livelock (red).                                      | 8  |

| 0.1  |                                                                       | 10 |

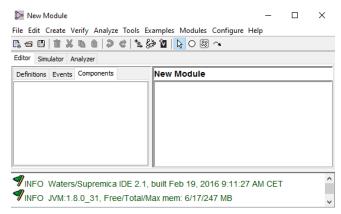

| 3.1  | Supremicas GUI.                                                       | 13 |

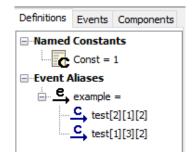

| 3.2  | Example: constant and alias in Supremica.                             | 14 |

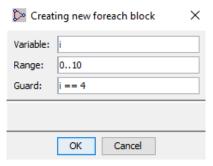

| 3.3  | Example: Creating a foreach-loop in Supremica.                        | 15 |

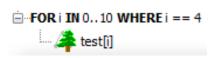

| 3.4  | Example: finished foreach-loops in Supremica.                         | 15 |

| 3.5  | Example: Creating an event as an array in Supremica.                  | 16 |

| 3.6  | Example: Including array events in Supremica                          | 16 |

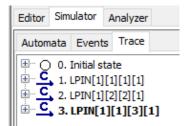

| 3.7  | Example: Trace when Simulating                                        | 16 |

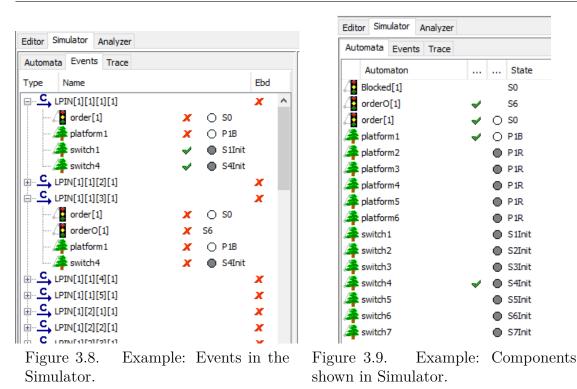

| 3.8  | Example: Events in the Simulator.                                     | 17 |

| 3.9  | Example: Components shown in Simulator                                | 17 |

| 3.10 | 1 5                                                                   | 18 |

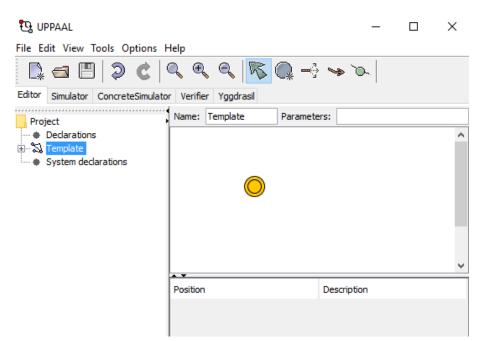

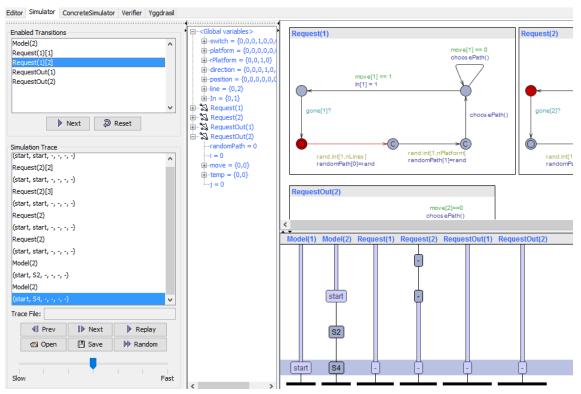

|      | UPPAAL's GUI.                                                         | 20 |

|      | Example of a Location / State.                                        | 23 |

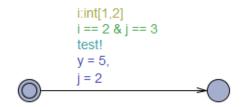

|      | Example Edge Label in UPPAAL.                                         | 24 |

|      | Example Urgent Transition in UPPAAL.                                  | 24 |

|      | Example of the normal simulator in UPPAAL.                            | 25 |

|      | Example of choosing a transition in the concrete simulator in UPPAAL. | 26 |

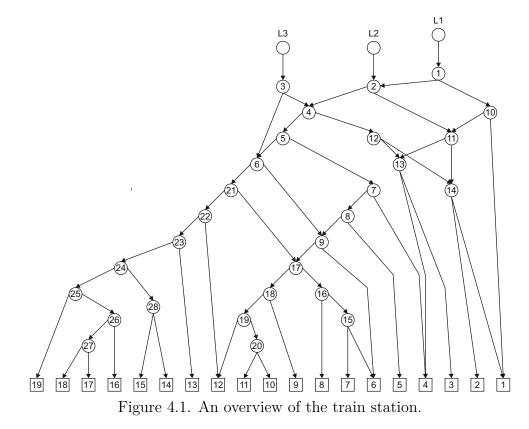

|      | Example of the Verifier.                                              | 27 |

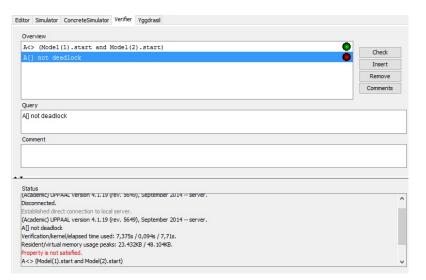

| 3.18 | Query Language Illustrated [4]                                        | 27 |

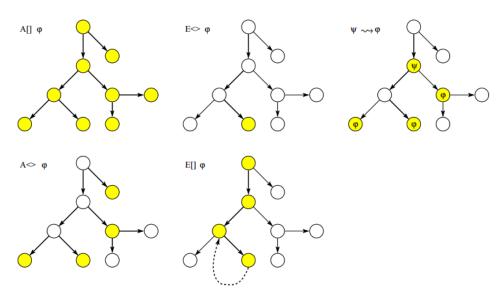

| 4.1  | An overview of the train station.                                     | 31 |

| 4.2  | An overview of the simplified train station.                          | 32 |

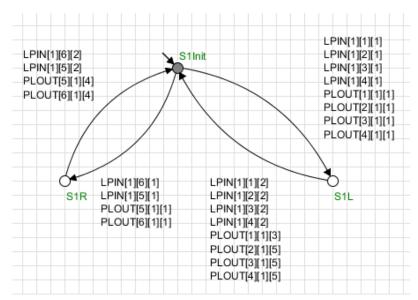

| 4.3  | A 2-state automaton describing a switch occupancy - Approach 1        | 33 |

| 4.4  | A trainmaker model with 2 lines and 2 platforms both for in and       |    |

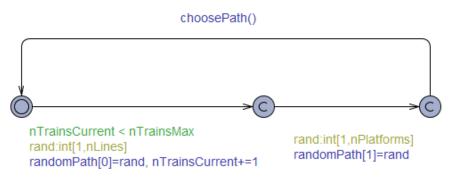

|      | outgoing trains - Approach 1                                          | 33 |

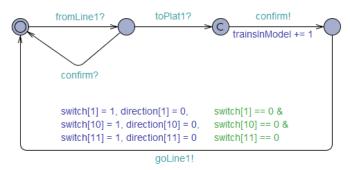

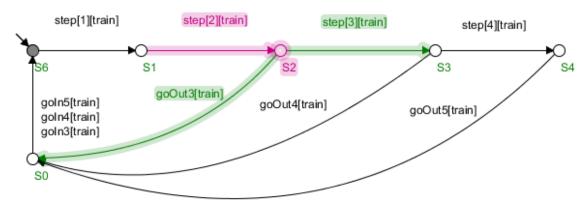

| 4.5   | Steps taken in two specifications when the <b>trainmaker</b> creates a train coming from line one to platform one - Approach 1 | 34 |

|-------|--------------------------------------------------------------------------------------------------------------------------------|----|

| 4.6   | The specification of a train using 3 switches with switches and direc-                                                         | 94 |

|       | tions as automata - Approach 1                                                                                                 | 35 |

| 4.7   | Three switch specification using variables - Approach 1                                                                        | 35 |

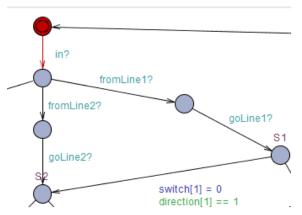

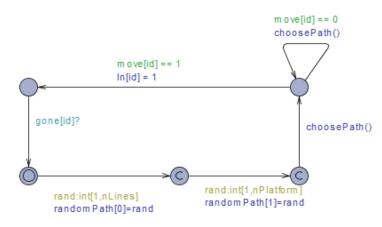

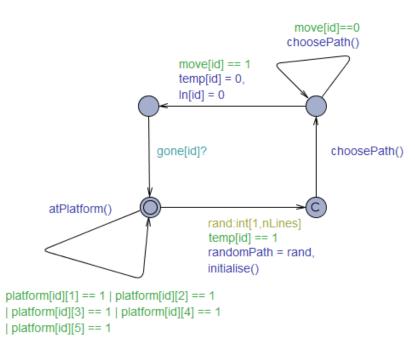

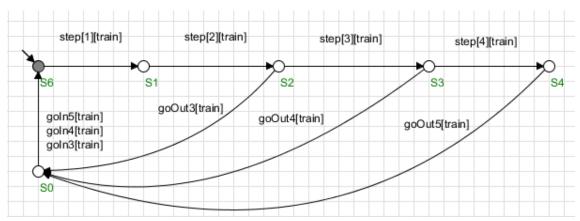

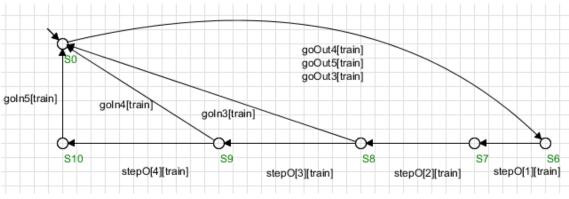

| 4.8   | The model for incoming trains - Approach 1                                                                                     | 36 |

| 4.9   | A description of how the model receives an incoming train - Approach<br>1                                                      | 36 |

| 4.10  | When switches are ready both goPlat! and leavePlat! will happen                                                                |    |

| 1 1 1 | at the same time - Approach 1                                                                                                  | 37 |

|       | goPlat sets the inbound model of the train station in a temp-state waiting for gone - Approach 1                               | 37 |

| 4.12  | <pre>leavePlat starts the train in the oubound model of the train station - Approach 1</pre>                                   | 37 |

| 4.13  | The outmodel of the train station is done and immediately fires gone                                                           |    |

|       | - Approach 1                                                                                                                   | 37 |

| 4.14  | The complete trainmaker with two lines in and five platforms - Ap-                                                             |    |

|       | proach 1                                                                                                                       | 38 |

| 4.15  | The in- and out-model of the train station combined with the trainDir                                                          |    |

|       | variable implemented - Approach 1                                                                                              | 38 |

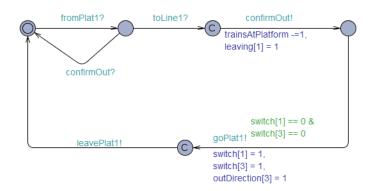

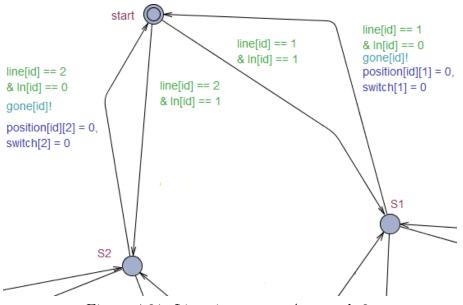

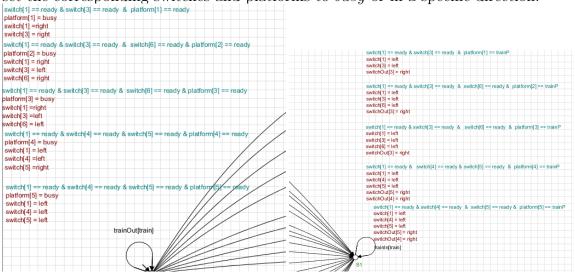

| 4.16  | Automaton Request Version 1 - Approach 2                                                                                       | 39 |

|       | Automaton Request Version 2 - Approach 2                                                                                       | 40 |

|       | Automaton RequestOut - Approach 2                                                                                              | 42 |

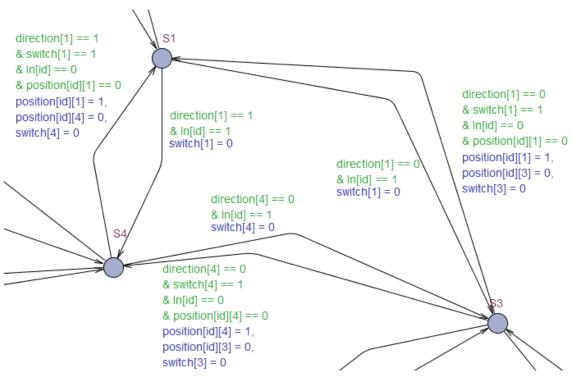

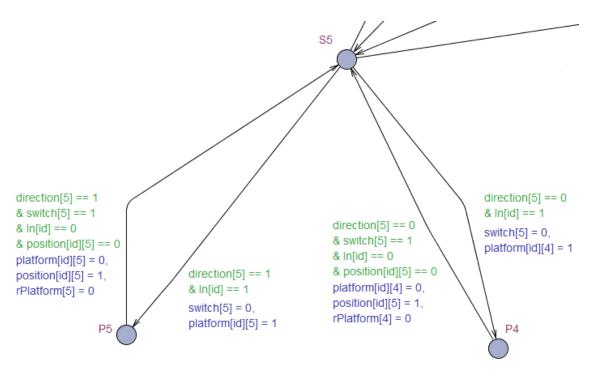

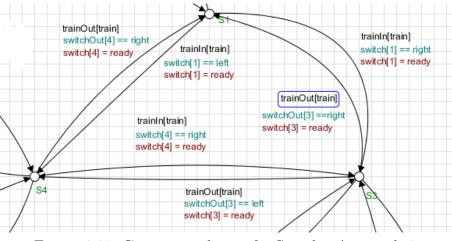

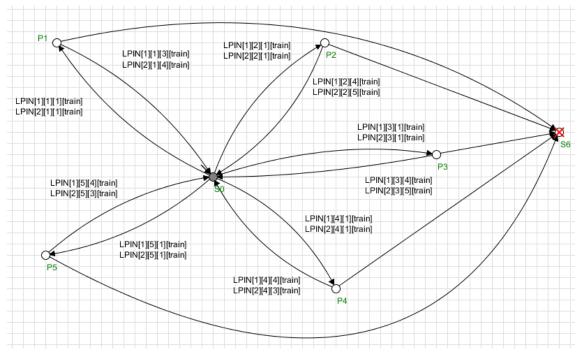

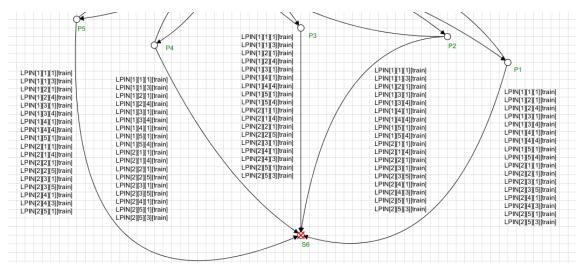

|       | Transition between Switches in Model automaton - Approach 2                                                                    | 44 |

|       | Transition in and from the Platforms in Model automaton - Approach                                                             |    |

|       | 2                                                                                                                              | 45 |

|       | Lines in Model - Approach 2.                                                                                                   | 46 |

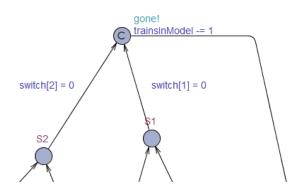

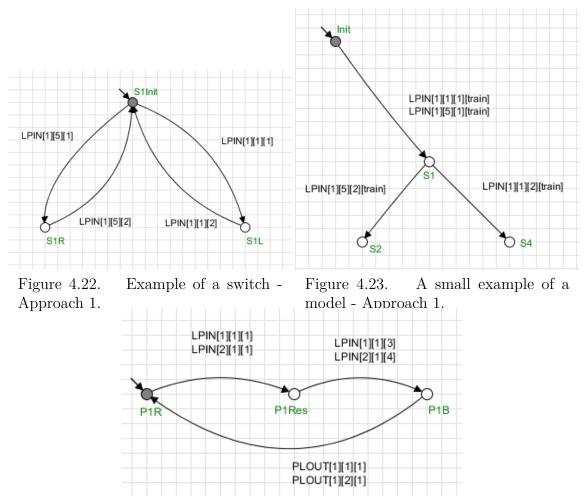

|       | Example of a switch - Approach 1                                                                                               | 48 |

|       | A small example of a model - Approach 1                                                                                        | 48 |

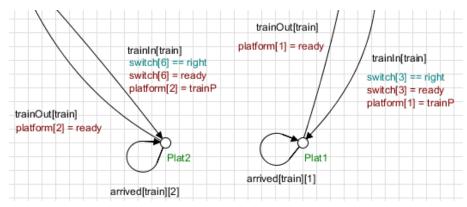

|       | An example of a platform.                                                                                                      | 48 |

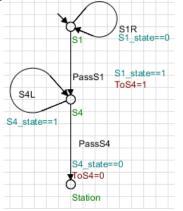

|       | An example of a switch - Approach 1                                                                                            | 49 |

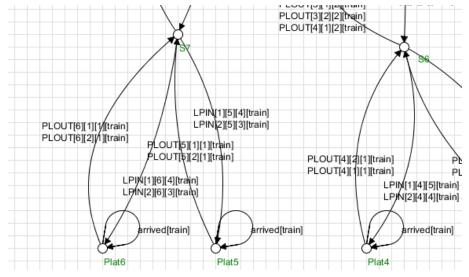

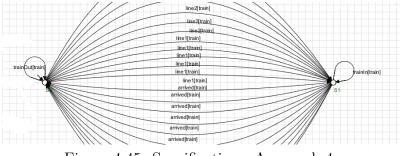

| 4.26  | The event <b>arrived</b> shown in the model of the train station - Approach                                                    |    |

|       | 1                                                                                                                              | 49 |

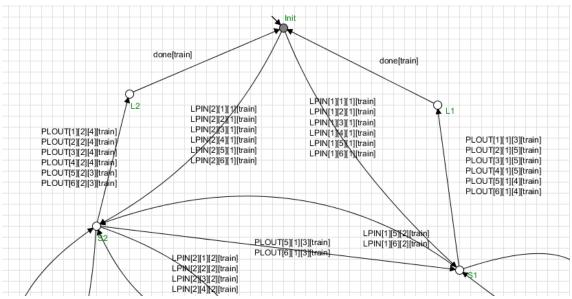

|       | The event <b>done</b> shown in the model of the train station - Approach 1.                                                    | 50 |

|       | Specification to handle the train direction in the model - Approach 1.                                                         | 50 |

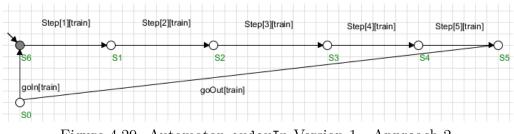

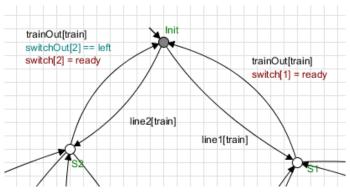

|       | Automaton orderIn Version 1 - Approach 2                                                                                       | 50 |

|       | Automaton orderOut Version 1 - Approach 2                                                                                      | 51 |

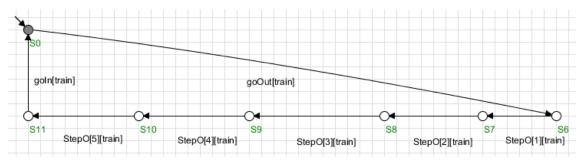

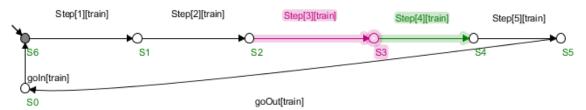

|       | Simulation of Automaton orderIn Version 1 - Approach 2                                                                         | 51 |

|       | Simulation of Automaton switch5 - Approach 2                                                                                   | 51 |

| 4.33  | Automaton orderIn Version 2 - Approach 2                                                                                       | 52 |

|       | Automaton orderOut Version 2 - Approach 2                                                                                      | 52 |

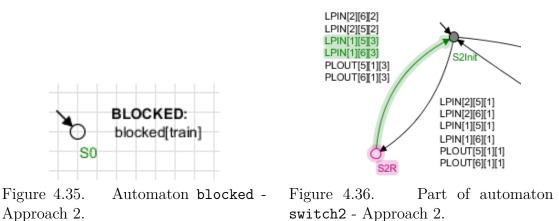

|       | Automaton blocked - Approach 2                                                                                                 | 53 |

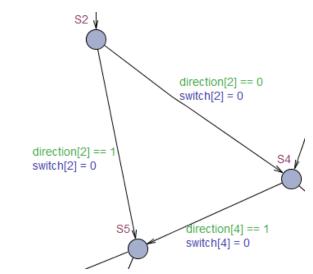

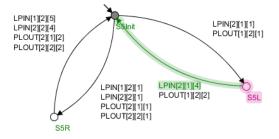

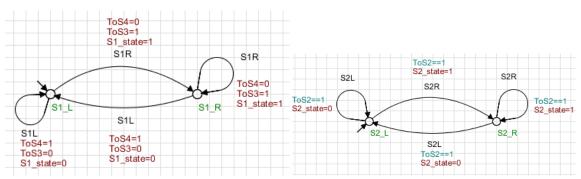

|       | Part of automaton switch2 - Approach 2                                                                                         | 53 |

|       | Simulation of automaton orderIn - Approach 2                                                                                   | 53 |

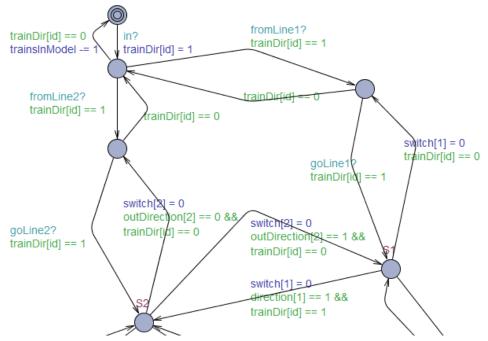

|       | Connecting the Switches with Variables Switch1- Approach 3                                                                     | 54 |

| 4.39  | Connecting the Switches with Variables Switch2 - Approach 3                                                                    | 54 |

| 4.40       | Train Specification - Approach 3                                  | 54 |

|------------|-------------------------------------------------------------------|----|

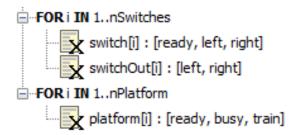

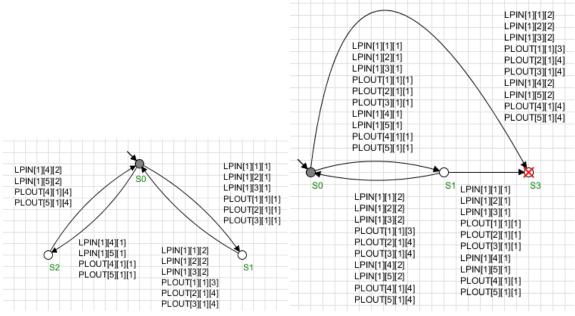

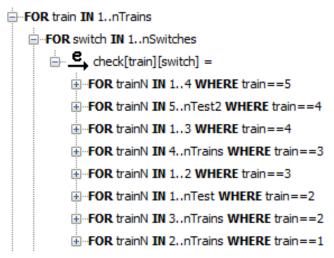

| 4.41       | The switches and platforms as variables - Approach 4              | 55 |

| 4.42       | Going in and out of a Switch - Approach 4                         | 55 |

| 4.43       | Going in and out of a Platform - Approach 4                       | 56 |

| 4.44       | Going in and out of <i>Init</i> - Approach 4                      | 56 |

| 4.45       | Specification - Approach 4                                        | 56 |

| 4.46       | Inbound transition labels for the Specification - Approach 4      | 57 |

| 4.47       | Outgoing transition labels for the Specification - Approach 4     | 57 |

| <b>_</b> . |                                                                   |    |

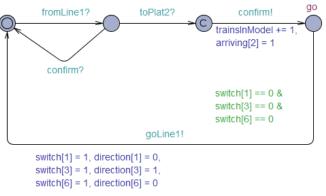

| 5.1        | The state go top right.                                           | 60 |

| 5.2        | The invariants $x<0$ and updates $x=0$ added                      | 61 |

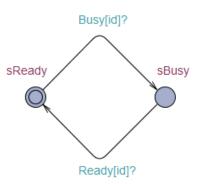

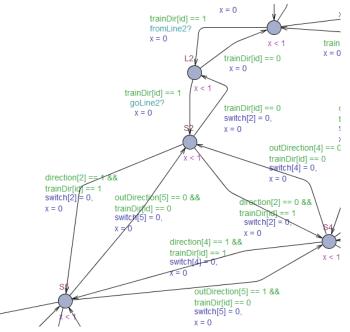

| 5.3        | Plant of a switch.                                                | 63 |

| 5.4        | Specification of the switch                                       | 63 |

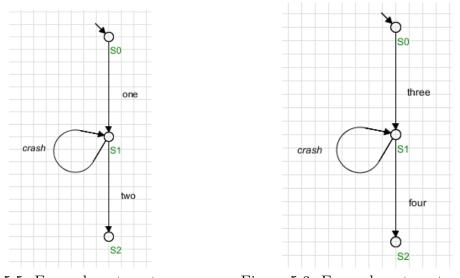

| 5.5        | Example automaton one                                             | 64 |

| 5.6        | Example automaton two                                             | 64 |

| 5.7        | Aliases for the uncontrollable events.                            | 64 |

| 5.8        | Specification to reach Platforms                                  | 65 |

| 5.9        | Specification to reach Platforms - Transitions to forbidden state | 65 |

| A.1        | Old Map of the Gothenburg Train Station [5]                       | Ι  |

# List of Tables

| 3.1 | Colorcoding of the Transition Labels in UPPAAL                            | 23 |

|-----|---------------------------------------------------------------------------|----|

| 3.2 | Query language with $\Psi$ and $\phi$ as state formula expressions in UP- |    |

|     | PAAL [6]                                                                  | 27 |

| 3.3 | Comparing Modelling and Verification Software Tools.                      | 29 |

|     |                                                                           |    |

|     | Results for UPPAAL for the simplified model of the train station          |    |

| 5.2 | Results for Supremica for the simplified model of the train station       | 67 |

| C 1 |                                                                           | 70 |

| 0.1 | Results for Supremica for the Gothenburg train station                    | 70 |

# 1 INTRODUCTION

One important part of the infrastructure of a country is the railway system. Due to the low emission rates and the energy efficiency in comparison to airplanes and vehicles, trains become essential for the transportation of goods and people [7]. Therefore a large number of trains run between cities and countries and are controlled by an automatic European signaling system. Before automatic signaling was introduced, timetables and flag officers were used for railway signaling. However, this could not be continued due to the increase of accidents by human error and high costs [8].

In 2014 in Sweden, 53 significant accidents occurred from which four were due to the collisions of trains. Over the last nine years, the amount of train collisions varied between one and four per year [9]. Even though this number might seem small, a lot of passengers or freight are affected and therefore it is necessary to reduce the collision risk. This can be done by modelling the railways, controlling the behaviour for the trains and verifying that no crashes occur.

There is a wide range of tools that are based on different methods to model and verify systems. Two of these tools are called UPPAAL and Supremica and offer modelling using automata and verification based on automata properties.

The task of the project is to test UPPAAL and Supremica to see if it is possible to build and verify a safety critical model using the Gothenburg station as a template. To do this, a model describing a train station is created and different techniques are used to specify the control for the trains. Thereafter the model, with specifications, is verified in different ways to ensure that no collisions can occur. Also, tutorials are to be created for both programs.

# 1.1 Scope

Due to Trafikverket not supplying information, assumptions have to be made. These include the functionality of the switches, the layout of the switches and platforms and the system behaviour used. Therefore, a standard railroad switch (see Section 2.1.2), an old map (see Appendix A.1) and the Route Locking and Sectional Release System (RLSRS, see Section 2.1.3) are chosen respectively.

The choice for the modelling and verification programs is predefined and based on

interest and experience. Therefore, UPPAAL and Supremica are used to complete the task.

# 1.2 Related Research

Verification of train systems is a current topic all around the world. However, the approaches and proofs differ. The following examples are only a few of many ideas available. It can be seen, that modelling and verification has not been done previously with UPPAAL or Supremica.

Similar work has been done using k-induction. The system is first described using a Kripke structure and then transformed into a transition function, on which a bounded model checking and inductive reasoning can prove certain properties. This has already been implemented and tested for the Danish Railway system from the University of Denmark and the University of Bremen, Germany. The results included the successful verification of safety properties for controlling large networks of realistic size [10].

The safety critical research group from the School of Railway Engineering in Iran has used the NuSMV, a symbolic model checker, to model and verify the interlocking control tables. The contents of the table and the behaviour of the train was analysed for conflicts. The tool set developed successfully minimizes the human interference in design, development and verification of the control table [11].

The safety properties of the European Train Control System are verified using compositional verification rules based on the Weakly monotonic time extension of DC by the Laboratory of Rail Traffic Control and Safety, Beijing Jiaotong University, Beijing. The proof divides the problem up into smaller sections which simplifies the system at hand. Resulting in a successful compositional verification of the system for controllability, reactivity and safety [12].

# 1.3 Outline

Chapter 2 describes the functionality of the European Train Control System (ETCS), automata and their properties. This is followed by Chapter 3 consisting of tutorials for the programs Supremica and UPPAAL which are used for the modeling and verification of the system. Next the modelling of the system in both programs is described in Chapter 4, followed by the verification of the models in Chapter 5. Thereafter the modelling and verification of the Gothenburg train station is described Chapter 6. Lastly, the conclusions drawn are explained in Chapter 7 and possible future work in Chapter 8.

2

# THEORETICAL BACKGROUND

This chapter explains the required theory necessary to understand the thesis. First the fundamentals of railways are described, followed by automata theory and ending with formal verification.

# 2.1 Fundamentals of Railways

Understanding the fundamentals of railways and switches is essential before modelling the system. Therefore, this section provides the basic knowledge needed to understand the task and the models.

## 2.1.1 European Train Control System

The European Union (EU) started the European Rail Traffic Management System (ERTMS) project, a Europe-wide standard for signalling, to increase the competitiveness of cross-border operation and signalling of trains. The ERTMS consists of three parts: the Global System for Mobiles - the Railway (GSM-R), the European Traffic Management Layer (ETML) and the European Train Control System (ETCS) [2].

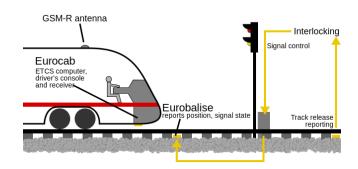

The ETCS is a system which uses signals to control the trains and prevent collisions. It requires equipment on the track and a controller in the train itself, as seen in Figure 2.1. The Eurobalise on the track reports the position and the signal state. It gets its information from the interlocking which processes the track release and sends a signal. The train has a GSM-R antenna, a ETCS computer and a receiver. The receiver processes the information received from the Eurobalise and the ETCS computer reacts accordingly [2].

Figure 2.1. ETCS components [2].

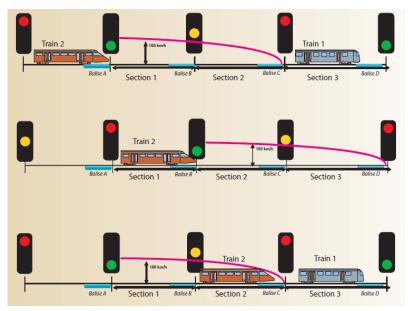

Figure 2.2 shows a lane divided into multiple blocks with two trains on it. When a train enters a block, the light turns red and hinders the following train to enter this block. This means, that the train has to have stopped by the time it reaches the red block. To achieve this, a braking trajectory is calculated by the ETCS computer, and is updated regularly [2].

Figure 2.2. ETCS functionality [2].

### 2.1.2 Railway Switches

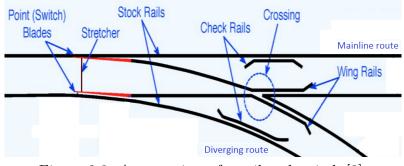

A railway switch is made out of three major parts: the point blades, the diverging route and the mainline route, see Figure 2.3. The point blades are the only movable parts and can be switched manually or automatically. The non-movable parts of the switch are called the stock rails. To make sure that the point blades can only touch one side of the stock rails at a time, a stretch bar is holding the blades together at a certain distance, see Figure 2.4.

Figure 2.3. An overview of a railroad switch [3].

Figure 2.4. Closeup of the stretcher bar [3].

The direction of the train is decided by the position of the point blades. When a train approaches, only one side of the point blades are used (see Figure 2.5) along with one side of the stock rails (see Figure 2.6). When the train passes the crossing there is a small gap in the rail. To make sure that the train does not derail, there are Wing rails and Check rails on each side to lead the train in the right direction [3]. Unless a switch is locked, the direction of the point blades are irrelevant when a train comes from either the mainline route or the diverging route. The train will force the point blades in the desired direction [13].

Figure 2.5. Pointblade [3].

Figure 2.6. Stockrail [3].

### 2.1.3 Train Station

A common system for train stations is called the Route Locking and Sectional Release System (RLSRS). This means that a train sets an inbound route to the train station by claiming all the switches necessary to reach the desired platform and the platform itself. After the train has passed a switch it will release it for other trains to claim [14].

When a train is near a station the speed is usually very low, because of this the ETCS described in Section 2.1.1 will behave slightly different. The braking trajectory will be disregarded because of the short braking distance.

#### 2.1.3.1 Gothenburg Train Station

The Gothenburg train station is the second largest train station in Sweden, serving 27 million passengers per year. Figure 2.7 shows the railway lines leading into the Gothenburg train station and to the 19 platforms.

Figure 2.7. Gothenburg train station [1].

# 2.2 Automata

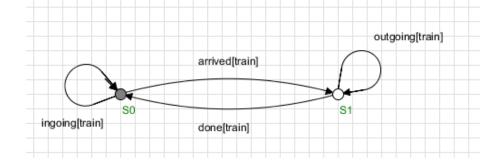

Systems can be modelled and verified using automata (see Definition 1) which are, simply put, machines that change from one *state* (often graphically represented by circles) to another by the means of *transitions* (often depicted as arrows). A state symbolises a certain configuration or situation of a system in which specific rules, policies and physical laws hold. Each transition is associated with an event which represents an incident that changes the state of the automaton. The initial state, the state in which an automaton starts in, is indicated by a transition without an origin [15].

Figure 2.8. An example of an automaton.

**Definition 1** An automaton is a tuple  $\mathcal{A} = \langle Q, \Sigma, \delta, q_0 \rangle$  with

- Q, a finite set of states

- $\Sigma$ , a finite set of events (i.e. the alphabet)

- $\delta \subseteq Q \times \Sigma \times Q$ , the transition function which describes, for each state and event, the next state after a certain event

- $q_0$ , the initial state of the automaton

## 2.2.1 Extended Finite Automata (EFA)

An extended finite automaton works exactly as an automaton, however, has some more functions in the transitions. While a common automaton has transitions that can only be associated to events, the EFA can use so called trigger conditions (guards). When a transition is fired, the EFA can also perform data operations (actions) [16]. This means that guards and actions can be associated with transitions e.g. a transition can only happen if the guard x == 1 is fulfilled and the action sets y = 1.

## 2.2.2 Marked/Forbidden States

A marked state is a state that is desired to be reached e.g. when a certain process is completed. It can either be graphically represented by a filled-in or a double circle. On the other hand, a forbidden state is a state which should not be reached and is graphically represented by a cross going through a circle [15].

# 2.2.3 (Co-)Reachability

A state is defined as **reachable** when a path of events from the initial state exists which leads to that state. If all states in an automaton are reachable, the automaton is **accessible**. If there exists a path from a state to the marked state, the state is **coreachable** and if all states in an automaton are coreachable, the automaton is **coaccessible**. An automaton is said to be **trim** if it is both accessible and coaccessible [15].

In Figure 2.9 the unreachable state (red) is still coreachable because a path to the marked state (grey) exists. On the other hand the green states are not coreachable but reachable.

Figure 2.9. Non-reachable (red) and non-coreachable (green) states.

### 2.2.4 Plants and Specifications

Plants and specifications are two different kinds of automata. Physical systems are always modelled as plants. The specification is, as the name suggests, one or more automata, that specifies how the plants are supposed to behave. An example is a keyboard modelled as a plant. When letter F is pressed the letter F will appear on the screen. The specification can control in which order and what letter should appear on the screen [15].

### 2.2.5 Synthesize and Synchronize

Automata can be synchronized which means, that common events must happen simultaneously while other, uncommon events, can occur within the restrictions of the corresponding automaton. Common events occur when the automata have the same events in their alphabet, see Definition 1. This means that if a common event *press* can happen in only one automaton, it cannot occur since it is blocked by the other automata with the same event *press*. This feature is often used to control the behaviour of the plant. A synchronized composition is a representation of all the synchronized automata combined [15].

A supervisor, also called a controller, is generated by synthesising and it dis-/enables specific events in the plant. It is devised such that it, together with the plant, fulfills the specification, meaning, that at least one marked state can be reached and no deadlock exists without directly restricting uncontrollable events [15].

### 2.2.6 Deadlock and Livelock

A deadlock state is a state that has no outgoing transitions and therefore the automaton cannot execute any other transition. This is not a problem if the deadlocked state is also a marked state since this is the desired behaviour. On the other hand, a problem exists if the deadlocked state is not marked since a desired state cannot be reached. Similarly, a livelock occurs when an automaton is caught in a loop of unmarked states that it cannot leave [17]. In figures 2.10 and 2.11 the grey state is a marked state and represents a wanted deadlock while the red states indicate an unwanted deadlock and a livelock respectively.

Figure 2.10. Automaton with an unwanted deadlock (red).

Figure 2.11. Automaton with a live-lock (red).

Blocking states are states from which a deadlock and a livelock can no longer be avoided [17]. This means that, if a state's only transition is to an unwanted deadlock, livelock or another blocking state, that state is a blocking state as well. Two (or more) automata are conflicting if, and only if, their synchronous composition is blocking [15]. An automaton with no blocking state is referred to as non-blocking.

#### 2.2.7 Uncontrollable Events

Physical systems can have uncontrollable events which need to be included in the plant. An uncontrollable event represents occurrences that the system cannot avoid or forbid. An example of an uncontrollable event is an opponent's move in a tic tac toe game. An uncontrollable state is where an uncontrollable event can occur in the plant even though the specification does not allow it. If a supervisor can reach an uncontrollable state, the system is uncontrollable [17].

#### 2.2.8 Non-deterministic Automata

When an automaton cannot determine the end state after a specific sequence of events, it is referred to as non-deteministic. This normally occurs if there are multiple initial states or multiple outgoing transitions from the same state to different states, labeled by the same event [17].

# 2.3 Formal Verification

Formal verification is (dis-)proving the correctness of a system, based on a specified property or formal specification [18]. The most common properties, according to [19], to verify a state or a particular situation are the following:

• Reachability - can be reached

For example: "x < 1 is always true", "the state S1 can always be reached" or "x == 1 always holds when in state S1".

• Safety - can never be reached (i.e. the negation of reachability)

For example: "x < 1 can never happen", "memory overflow can never happen" or "both processes are never in the critical section".

• Liveness - will ultimately occur

For example: "the elevator will arrive eventually, if it is called", "x == 1 will ultimately be satisfied" or "there will be sunshine after the rain".

• Fairness - will (or not) occur infinitely often