## Effect of high-k dielectric and ionic liquid gate on nanolayer black-phosphorus field effect transistors

M. Venkata Kamalakar, <sup>a)</sup> B. N. Madhushankar, André Dankert, and Saroj P. Dash<sup>b)</sup> Department of Microtechnology and Nanoscience, Chalmers University of Technology, SE-41296 Göteborg, Sweden

(Received 30 April 2015; accepted 25 August 2015; published online 15 September 2015)

Nanolayer black phosphorus (BP) is a direct bandgap semiconducting two dimensional crystal, showing immense promise for future nanoelectronic devices. Here, we report the effect of high-k dielectric and ionic-liquid gate in BP field effect transistors (BP FET). An ambipolar behavior is observed in pristine BP FETs with current modulation of 10<sup>4</sup>. With a high-k HfO<sub>2</sub> encapsulation, we observed identical switching performance in the BP FETs, however, with noticeable enhancement in mobility at room temperature. In comparison to the pristine device, the HfO<sub>2</sub> encapsulation showed a contrasting decrease in mobility at lower temperatures. BP FETs with electric double layer ionic liquid gate showed a drastic improvement in the subthreshold swing (SS) to 173 mV/dec and operation voltages less than 0.5 V in comparison to solid state SiO<sub>2</sub> back gated devices. Our results elucidate the effect of different electrostatic conditions on BP transistor channels and open up ways for further exploration of their prospects for nanoelectronic devices and circuits. © 2015 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4930236]

Moore's law has driven the semiconductor industry towards down-scaling of transistors for faster device performance, less power consumption, cheaper and large-scale fabrication. However, such scaling cannot continue indefinitely due to challenges like short channel effects, leakage, mobility reduction, and fabrication issues. Further development requires exploration of advanced channel materials with high carrier mobility to replace the conventional silicon. The discovery of two dimensional (2D) crystal graphene with high mobility channels has enabled the fabrication of high frequency devices and has unveiled alternative ways to study Dirac physics.<sup>2,3</sup> However, graphene in its pristine form lacks a band gap which is essential for switching in logic circuits.<sup>4</sup> Henceforth, the search for semiconducting 2D materials with a sizable bandgap has resulted in the discovery of crystals of transition metal dichalcogenides (such as MoS<sub>2</sub>) and blackphosphorus (BP).<sup>5–9</sup> While, MoS<sub>2</sub> is an n-type semiconductor, the BP shows an ambipolar behavior with dominant ptype conduction. The sub-nanometer dimensionality of these 2D materials gives rise to drastically different qualities when manipulated and structured at atomic scale, making them highly significant from both scientific and technological perspectives.

The interest in BP is primarily due to its direct bandgap, which varies from 0.3 to 1 eV with the number of atomic layers.  $^{6,10}$  Recently, field effect and photo transistors of BP with high on/off ratios, ambipolar behavior with high hole carrier mobilities, and structural anisotropy have been demonstrated.  $^{6,11-14}$  Most of these devices were made with Ti/Au source-drain contacts and thick SiO<sub>2</sub> dielectric as the back gate. These reports revealed the presence of a sizable Schottky barrier  $\sim 200 \, \mathrm{meV}$  at Ti/BP interfaces.  $^{11}$  Such a large barrier at the metal-BP interface remains a hurdle in

the fabrication of Ohmic contacts, which are essential for electronic devices 15,16 and viable for spintronic applications. 15 Other strategies to improve performance constitute the use of high k-dielectrics and high capacitance ionic liquid gate for better control over the carrier density and low device operation voltage of the BP channel. It was also observed that the 2D semiconductors are susceptible to surface degradation with exposure to humidity and air exposure over time. 12 Encapsulation using high-k dielectric not only protects the channel against such surface degradation but has also been seen to influence the electrostatic conditions modifying the channel properties. These behaviors necessitate the investigation of the effect of dielectric encapsulated BP channels to realize devices with high reliability. Additionally, ionic liquids (IL) have been used as dielectric for gating field effect devices because of their ability to electrostatically dope the semiconducting channel with carrier densities up to  $10^{15} \, \mathrm{cm}^{-2}$ , which are two orders of magnitude higher than that achieved using solid state gates. <sup>17</sup> Recently, interesting physics has been explored with IL gates on different electronic materials, for example, a metal to insulator transition in  $VO_2$ , <sup>18</sup> ferromagnetism in GaMnAs, <sup>19</sup> superconductivity and ambipolar behavior of  $MoS_2$ , <sup>20,21</sup> Dirac physics in topological surface states, <sup>22</sup> and very recently insulator to metal transition in BP.<sup>23</sup> Therefore, it is of considerable interest to further investigate the influence of high-k dielectrics and ionic liquid gate on the performance of BP field effect transistors.

In this article, we explore the influence of BP channel encapsulation with a high-k HfO<sub>2</sub> dielectric and electronic double layer transistors with ionic liquid gates. The effects of these electrostatic modifications to the BP channel on the field effect performance, and carrier mobility have been investigated here. Our measurements at different source-drain voltages, gate voltages, and temperatures in both electron and hole conduction regimes provide

a)E-mail: venkata.phys@gmail.com

b)saroj.dash@chalmers.se

understanding of such BP devices and their prospect in nanoelectronics.

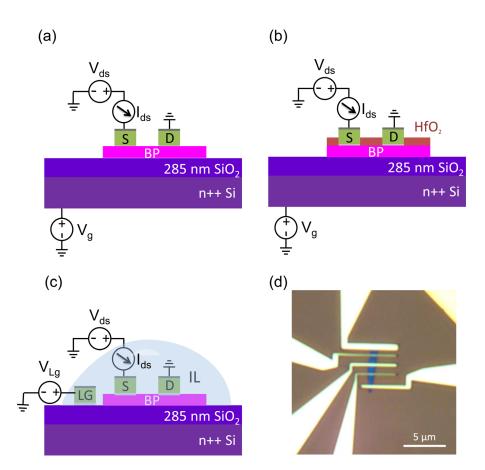

In Figure 1, we present the schematics of devices used in our experiments and a fabricated BP FET. We used BP flakes mechanically exfoliated from bulk BP crystals (procured from Smart elements) onto a SiO<sub>2</sub>(285 nm)/Si substrate. The selected flakes were found to have a thickness  $\sim 5 \, \text{nm}$  with width  $\sim$ 2–3  $\mu$ m as measured from atomic force microscopy and optical microscopy techniques respectively.<sup>24</sup> Ferromagnetic tunnel contacts of TiO<sub>2</sub>(1 nm)/Co(65 nm)/Al(4 nm) were prepared over these BP flakes with gaps  $\sim$ 1  $\mu$ m through nanofabrication techniques of electron beam lithography and e-beam evaporation methods. The thin layer of TiO2 acts as a tunnel barrier that considerably alleviates the band bending and dramatically reduces the Schottky barrier to few (<50) meV from a high value  $\sim 200$  meV present at the metal/BP interface.<sup>24</sup> Devices with such ferromagnetic tunnel contacts are prospective schemes for spintronic applications. 25,26 For the solid state back gate device, the SiO<sub>2</sub>/n-Si substrate was used to control the BP carrier concentration (Fig. 1(a)). In order to investigate the effect of high-k dielectrics on BP channels, devices with an HfO<sub>2</sub> capping layer of 20 nm over the BP channel (shown in Fig. 1(b)) were prepared by atomic layer deposition (ALD) technique at 350 °C. For ionic liquid gate devices, a small droplet of the DEME-TFSI ionic liquid (Sigma Aldrich 727679) was applied onto the devices, covering the BP layer and the source, drain and gate electrode (LG) as depicted in Fig. 1(c). We have performed a detailed characterization of contact resistances and transistor behavior of fabricated BP devices. To extract the Schottky barrier height, we performed temperature dependent drain-source  $I_{ds}$ - $V_{ds}$  characteristics of the device at different gate voltages. The Schottky barrier height was found to be <50 meV for BP/TiO<sub>2</sub>/Co contacts. The details of the Schottky barrier calculations with TiO<sub>2</sub>/Co contacts have been presented elsewhere.<sup>24</sup>

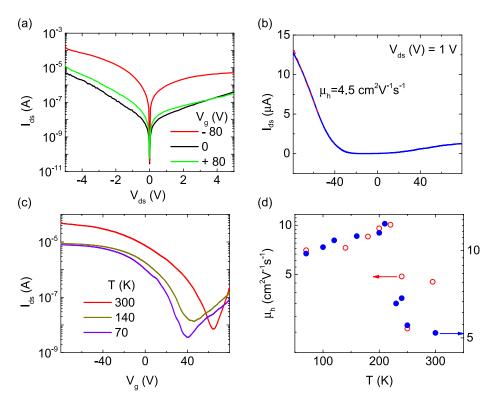

BP FET without capping-layer: We first investigate the field effect transistor characteristics of BP with SiO<sub>2</sub>/n-Si back gate as depicted in Fig. 1(a). For these devices, the BP flakes were intentionally aged for one month after the electron beam lithography with PMMA capping to verify reliability and aging effect. Such aged sample of crystals like MoS<sub>2</sub> have been observed to show better current stability.<sup>27</sup> The output characteristics of drain-source current  $(I_{ds})$  while sweeping the drain-source voltage  $(V_{ds})$  were measured at several applied gate voltages  $(V_g)$  (Fig. 2(a)). The transfer characteristics were recorded by sweeping the  $V_{\rm g}$  while measuring the  $I_{\rm ds}$  for different  $V_{\rm ds}$  (Figs. 2(b) and 2(c)). The measured transfer characteristics are typical for ambipolar behavior of BP with an asymmetry in I<sub>ds</sub>, which is due to the position of the Co Fermi level close to the valence band of the BP.<sup>6,24</sup> The negative and positive gate voltages correspond to hole and electron doping in BP, respectively.

We extract the field effect mobility  $\mu$  in BP from the slope in the linear region of the measured transfer characteristics using expression (1)

$$\mu = [(dI_{ds})/(dV_{bg})] \times [L/(WC_iV_{ds})],$$

(1)

where *L* is the length, *W* is the width of the BP channel, and  $C_i$  is the capacitance between the channel and the back-gate per unit area  $(C_i = \varepsilon_0 \varepsilon_r / d; \ \varepsilon_r = 3.9 \ \text{for SiO}_2; \ d = \text{oxide}$

FIG. 1. Nanolayer black phosphorous (BP) field effect device: (a) Schematic of a BP FET with source, drain, and  $SiO_2/Si$  back gate. (b) BP FET with  $HfO_2$  top encapsulation layer and source, drain, and  $SiO_2/Si$  back gate. (c) BP electric double layer transistor with ionic liquid gate. (d) Optical image of 5 nm thick BP FET with  $TiO_2$  (1 nm)/Co contacts on  $SiO_2/Si$  substrate.

FIG. 2. Characterization of BP FETs. (a) Output characteristics  $I_{ds}$ – $V_{ds}$  measured in high bias range for different gate voltages  $(V_g)$ . (b) Transfer characteristic  $I_{ds}$ – $V_g$  for  $V_{ds}$  = 1 V. The effective field-effect mobility for holes in BP channel is  $4.5 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  as calculated from the subthreshold slope of the transfer curves. (c) Transfer characteristics at different temperatures in logarithmical scaling reveal an  $I_{\rm on}/I_{\rm off} > 10^4$ for hole and  $> 10^2$  for electron conduction regimes. (d) Temperature dependence of the hole mobility for two different BP channels with equal thickness.

thickness of 285 nm). The effective field-effect mobility is found to be  ${\sim}4.5\,\mathrm{cm}^2\,\mathrm{V}^{-1}\,\mathrm{s}^{-1}$  for holes at room temperature. These devices also show a reasonable transistor on/off ( $I_{on}/I_{off}$ ) performance  ${>}10^4$  for hole and  ${>}10^2$  for electron conduction regimes. We would like to note that in comparison to the freshly prepared BP FETs $^{24}$  although the aged devices showed mobility reduction by more than an order in magnitude, the transistor on/off performance remained unaffected with aging of the devices. Such information of aged BP FETs are important as devices used in practical applications need to perform reliably over a period of time.

We further examined the temperature dependence of the carrier mobility to uncover the factors that could limit the mobility in our BP FETs. Transfer characteristics measured in the temperature range 77 K–300 K are shown in Fig. 2(c). The transistor on/off performance is found to increase slightly at low temperature for both electrons and hole conductions in comparison to the value at 300 K. As displayed in Fig. 2(d), the hole mobility is found to increase with lowering the temperature and saturates below 125 K. Such behavior of the mobility at low temperature is consistent with scattering from charged impurities, <sup>6,24,28</sup> which can be presented on the BP surface or at the BP/SiO<sub>2</sub> interface. The drop in mobility from 200 to 300 K can be attributed to the electron–phonon scattering which is the dominant mechanism at higher temperatures.

BP FET with HfO<sub>2</sub> capping-layer: A high-k dielectric substrate or capping-layer can affect the performance of thin-film transistors. On one hand, the introduction of surface disorder can reduce the charge carrier mobility, <sup>30</sup> and on the other hand, the dielectric screening can enhance the mobility.<sup>5,31</sup> It has been reported that high-k capping-layers on MoS<sub>2</sub> FETs can strongly dampen the Coulomb scattering of the charge carriers.<sup>5</sup> For the case of BP thin-film FETs, unresolved questions about the role of the high-k dielectric substrate and capping-layers still remain. Recently, a transition

from p-type to ambipolar behavior of BP has been observed in  ${\rm Al}_2{\rm O}_3$  top gated device.  $^{32}$

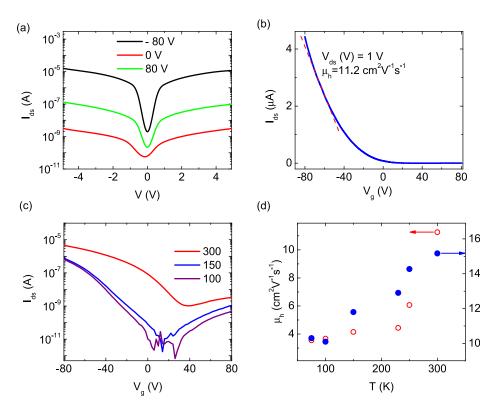

Here, we investigate the effect of a high-k  $\rm HfO_2$  encapsulation on BP transistors with  $\rm TiO_2/Co$  source-drain contacts. The output characteristics  $I_{\rm ds}-V_{\rm ds}$  revealed linear behavior at small bias voltages with the onset of non-linearity at high  $V_{\rm ds}$ . In Fig. 3(a), we present the output characteristics  $I_{\rm ds}-V_{\rm ds}$  for different gate voltage ( $I_{\rm ds}$  in log scale). Figures 3(b) and 3(c) show the measured transfer characteristics, which are typical for the ambipolar behavior of BP. In comparison to the device without  $\rm HfO_2$  capping layer, we find a shift in the threshold voltage  $\rm V_{th}$  for these devices. The effective field-effect mobility at room temperature is found to show an increment to  $11.2\,\rm cm^2~V^{-1}~s^{-1}$  for hole conduction regimes, which is more than double the mobility obtained without the capping layer.

The temperature dependence of the transfer characteristics was studied to understand the various factors that affect the mobility in our BP channel covered with HfO2. The transistor on/off performance increases by more than an order of magnitude for both electron and hole conduction at 100 K in comparison to the value at 300 K (Fig. 3(c)). With an on/off ratio up to 10<sup>4</sup> for hole regime and up to 10<sup>2</sup> for electron regime over the entire temperature range, the device showed transistor performance similar to device performance without capping layer. The hole mobility as a function of temperature is shown in Fig. 3(d), which shows a monotonic increase up to room temperature. This is in sharp contrast to the behavior observed for the device without HfO2 capping, where the mobility showed a down turn (Fig. 2(d)) in phonon limited temperature range closer to 300 K. Such behavior could possibly arise from the dominance of scattering from freshly created charged impurities at the interface of HfO<sub>2</sub> and BP. In addition, the presence of a top layer of HfO<sub>2</sub> can further contribute to the quenching of effective phonon-carrier scattering. Further studies till higher temperatures and theoretical

FIG. 3. BP FET with HfO<sub>2</sub> cap layer. (a) Output characteristics  $I_{\rm ds}$ – $V_{\rm ds}$  measured for different gate voltages at room temperature ( $V_{\rm g}$ ). (b) Transfer characteristic  $I_{\rm ds}$ – $V_{\rm g}$  for different  $V_{\rm ds}$  in a linear scaling. (c) Transfer characteristic in logarithmical scaling for  $V_{\rm ds}$  = 1 V measured at different temperatures. (d) Temperature dependence of hole mobility for two different channels having similar thickness.

modelling could shed light on the exact mechanism of such temperature dependent behavior with HfO<sub>2</sub> on BP.

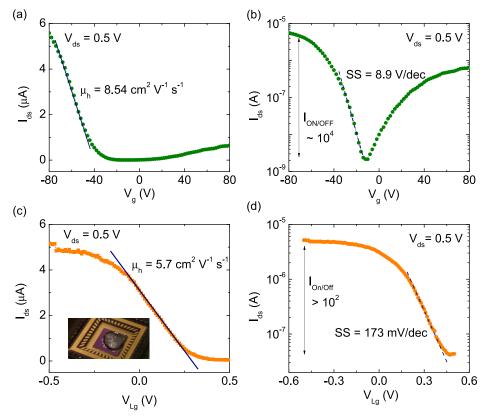

BP electric double layer transistor with ionic liquid gate: We also examined the effect of an electrolytic gate on the BP transistor performance. The electrolytic or ionic liquid (IL) gate is a unique way to induce high carrier densities in transistor channels. The IL forms an electric double layer at the interface and thus acts as a nano-gap capacitor with an extremely large capacitance. 17 A droplet of ionic liquid (Diethylmethyl(2-methoxyethyl)ammonium bis(trifluoromethylsulfonyl)imide; Sigma-Aldrich: 727679) was applied onto the surface of the BP, also covering a side gate electrode (Schematic Fig. 1(c)). An applied gate voltage drives either anions or cations onto the channel surface under positive or negative bias, respectively. The ions and induced carriers  $(\sim 10^{14} \, \text{cm}^{-2})$  form an equivalent capacitance of  $\sim 1.5$  mF/ cm<sup>2,21</sup> Figs. 4(a) and 4(b) show the transfer characteristics of a device measured with a SiO<sub>2</sub> back gate (BG) before applying the IL. The device shows a reliable transistor performance with  $I_{on}/I_{off}$  ratio of  $10^4$ , hole mobility  $\sim 8.5 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , subthreshold swing (SS)  $\sim 9 \text{ V/dec.}$  Gating with the IL reduced the operating gate voltage considerably to less than 0.5 V compared to that in the SiO<sub>2</sub> BG configuration (80 V) (Figs. 4(c) and 4(d)). The carrier mobility is calculated (using  $C_{ILG} = 1.5 \,\mu\text{F cm}^{-2}$ ) to be around 5.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, which is close to 8.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> with the SiO<sub>2</sub> BG configuration. An improvement in the SS has also been observed, which reduced drastically from  $\sim$ 9 V/dec in SiO<sub>2</sub> BG device to 170 mV/dec with IL gating. This value of SS is very close to the standard value of 60 mV/dec for commercial Si MOSFET devices.<sup>28</sup> We observe a transistor behavior with good current saturation and a current  $I_{on}/I_{off}$  ratio exceeding  $10^2$  for holes. It is observed that the off-state current has been increased by two orders with IL gate, while the on-state current remains the same. The increase of the off-state current could be due to the

fixed charges in the dielectric layer influencing the Schottky barrier at the contacts.<sup>21</sup> Another reason could be due to the role of interface trap density at the BP top surface in contact with the IL gate. The absence of ambipolarity in the IL device has been observed, which may be due to a limited window of gate sweep performed in our measurements. Also the shift of the minimum current to positive voltage can be attributed to the presence of fixed charges at the interfaces. We note that the contacts showed considerable deterioration after 30 min of measurements. Such degradation can be avoided by employing noble metals such as gold or platinum for electrodes or capping layer in future. Our experiments indicate that the electrostatic conditions at the surface of the channel can influence the performance and properties in BP FETs with unique outcomes. We believe that the performance in our devices can be further improved by the use of high quality BP devices using van der Waals heterostructures of BP with 2D dielectric crystals such as hexagonal boron nitride. 33-38

In conclusion, we have investigated the effect of highk dielectrics and ionic liquid gating on BP field effect transistors with low Schottky barrier source-drain contacts. With a high-k HfO<sub>2</sub> encapsulated layer on BP, we observed a reliable ambipolar transistor performance with on/off ratio up to 10<sup>4</sup> for the hole regime and up to 10<sup>2</sup> for the electron regime, similar to uncapped devices. However, we observed an increase in mobility with temperature for the HfO<sub>2</sub> capped device indicating some thermal activated transport. This is in contrast to the decrease in mobility at higher temperatures seen in the uncapped BP device due to phonon assisted scattering processes. In the BP electric double layer transistor employing an ionic liquid gate, we observed a drastic improvement in the subthreshold swing (173 mV/dec) and device operation below 0.5 V. Our experiments elucidate that the use of high-k dielectric capping and ionic liquid gate can lead to reliable and improved

FIG. 4. BP electric double layer transistor with ionic liquid gate (a) BP FETs with SiO<sub>2</sub> back gate before application of ionic liquid. Transfer characteristics of BP FETs with SiO<sub>2</sub> back gate measured at the drain-source bias  $V_{\rm ds} = 0.5$  V. (b) the same transfer characteristics as in Fig. 4(a) in log scale. (c) Electric double layer transistor with ionic liquid gate. Transfer characteristics of the BP IL-gated FETs measured at the drain-source bias  $V_{\rm ds} = 0.5$  V. Inset—Device of an IL-gated BP FET. (d) The same transfer characteristics as in Fig. 4(c) in log scale.

device performance in BP field effect transistors. This paves the way for BP electronic, spintronic, and optoelectronic devices with electrostatic control of charge carriers by different methods and further exploration of device physics.

The authors acknowledge the support from colleagues of Quantum Device Physics Laboratory and Nanofabrication Laboratory at Chalmers University of Technology. This research was financially supported by Nano Area of Advance program at Chalmers University of Technology, EU FP7 Marie Curie Career Integration grant, and Swedish Research Council Young Researcher Grant.

<sup>1</sup>International Technology Roadmap for Semiconductors, Semiconductor Ind. Assoc., 2013, http://www.itrs.net/.

<sup>2</sup>K. S. Novoselov, V. I. Fal'ko, L. Colombo, P. R. Gellert, M. G. Schwab, and K. Kim, Nature 490, 192 (2012).

<sup>3</sup>A. K. Geim and K. S. Novoselov, Nat. Mater. **6**, 183 (2007).

<sup>4</sup>F. Schwierz, Nat. Nanotechnol. 5, 487 (2010).

<sup>5</sup>B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, Nat. Nanotechnol. **6**, 147 (2011).

<sup>6</sup>L. Li, Y. Yu, G. J. Ye, Q. Ge, X. Ou, H. Wu, D. Feng, X. H. Chen, and Y. Zhang, Nat. Nanotechnol. 9, 372 (2014).

<sup>7</sup>A. Morita, Appl. Phys. A Solids Surf. **39**, 227 (1986).

<sup>8</sup>J. Wittig and B. T. Matthias, Science **160**, 994 (1968).

<sup>9</sup>J. C. Jamieson, Science **139**, 1291 (1963).

<sup>10</sup>S. Das, W. Zhang, M. Demarteau, A. Hoffmann, M. Dubey, and A. K. Roelofs, Nano Lett. **14**, 5733 (2014).

<sup>11</sup>H. Liu, A. T. Neal, Z. Zhu, Z. Luo, X. Xu, D. Tománek, and P. D. Ye, ACS Nano 8, 4033 (2014).

<sup>12</sup>S. P. Koenig, R. A. Doganov, H. Schmidt, A. H. Castro Neto, and B. Özyilmaz, Appl. Phys. Lett. **104**, 103106 (2014).

<sup>13</sup>M. Buscema, D. J. Groenendijk, S. I. Blanter, G. A. Steele, H. S. J. van der Zant, and A. Castellanos-Gomez, Nano Lett. 14, 3347 (2014).

<sup>14</sup>F. Xia, H. Wang, and Y. Jia, Nat. Commun. 5, 4458 (2014).

<sup>15</sup>A. Dankert, L. Langouche, M. V. Kamalakar, and S. P. Dash, ACS Nano 8, 476 (2014).

<sup>16</sup>S. Das, H.-Y. Chen, A. V. Penumatcha, and J. Appenzeller, Nano Lett. 13, 100 (2013).

<sup>17</sup>T. Fujimoto and K. Awaga, Phys. Chem. Chem. Phys. **15**, 8983 (2013).

<sup>18</sup>M. Nakano, K. Shibuya, D. Okuyama, T. Hatano, S. Ono, M. Kawasaki, Y. Iwasa, and Y. Tokura, Nature 487, 459 (2012).

<sup>19</sup>M. H. S. Owen, Ph.D. thesis, Cambridge University, 2010.

<sup>20</sup>J. T. Ye, Y. J. Zhang, R. Akashi, M. S. Bahramy, R. Arita, and Y. Iwasa, Science 338, 1193 (2012).

<sup>21</sup>M. M. Perera, M.-W. Lin, H.-J. Chuang, B. P. Chamlagain, C. Wang, X. Tan, M. M.-C. Cheng, D. Tománek, and Z. Zhou, ACS Nano 7, 4449 (2013).

<sup>22</sup>K. Segawa, Z. Ren, S. Sasaki, T. Tsuda, S. Kuwabata, and Y. Ando, Phys. Rev. B 86, 075306 (2012).

<sup>23</sup>Y. Saito and Y. Iwasa, ACS Nano 9, 3192 (2015).

<sup>24</sup>M. V. Kamalakar, B. N. Madhushankar, A. Dankert, and S. P. Dash, Small 11, 2209 (2015).

<sup>25</sup>A. Dankert, M. V. Kamalakar, J. Bergsten, and S. P. Dash, Appl. Phys. Lett. **104**, 192403 (2014).

<sup>26</sup>M. V. Kamalakar, C. Groenveld, A. Dankert, and S. P. Dash, Nat. Commun. 6, 6766 (2015).

<sup>27</sup>R. Samnakay, C. Jiang, S. L. Rumyantsev, M. S. Shur, and A. A. Balandin, Appl. Phys. Lett. **106**, 023115 (2015).

<sup>28</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices* (John Wiley & Sons, Inc., Hoboken, NJ, USA, 2006).

<sup>29</sup>B. Disavljevic and A. Kis, Nat. Mater. 12, 815 (2013).

<sup>30</sup>High-K Gate Dielectrics for CMOS Technology, edited by G. He and Z. Sun (John Wiley & Sons, 2012).

<sup>31</sup>D. Jena and A. Konar, Phys. Rev. Lett. **98**, 136805 (2007).

<sup>32</sup>H. Liu, A. T. Neal, M. Si, Y. Du, and P. D. Ye, IEEE Electron Device Lett. 35, 795 (2014).

<sup>33</sup>M. V. Kamalakar, A. Dankert, J. Bergsten, T. Ive, and S. P. Dash, Sci. Rep. 4, 6146 (2014).

<sup>34</sup>L. Li, G. J. Ye, V. Tran, R. Fei, G. Chen, H. Wang, J. Wang, K. Watanabe, T. Taniguchi, L. Yang, X. H. Chen, and Y. Zhang, Nat. Nanotechnol. 10, 608 (2015)

<sup>35</sup>L. Li, F. Yang, G. J. Ye, Z. Zhang, Z. Zhu, W.-K. Lou, L. Li, K. Watanabe, T. Taniguchi, K. Chang, Y. Wang, X. H. Chen, and Y. Zhang, e-print arXiv:1504.07155.

<sup>36</sup>R. A. Doganov, S. P. Koenig, Y. Yeo, K. Watanabe, T. Taniguchi, and B. Özyilmaz, Appl. Phys. Lett. **106**, 083505 (2015).

<sup>37</sup>R. A. Doganov, E. C. T. O'Farrell, S. P. Koenig, Y. Yeo, A. Ziletti, A. Carvalho, D. K. Campbell, D. F. Coker, K. Watanabe, T. Taniguchi, A. H. C. Neto, and B. Özyilmaz, Nat. Commun. 6, 6647 (2015).

<sup>38</sup>N. Gillgren, D. Wickramaratne, Y. Shi, T. Espiritu, J. Yang, J. Hu, J. Wei, X. Liu, Z. Mao, K. Watanabe, T. Taniguchi, M. Bockrath, Y. Barlas, R. K. Lake, and C. Ning Lau, 2D Mater. 2, 011001 (2014).