## THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## Characterization of Nanomaterials for Interconnect and Thermal Management in Electronic Packaging

Si Chen

Department of Microtechnology and Nanoscience (MC2) BioNano Systems Laboratory CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden 2015 Characterization of Nanomaterials for Interconnect and Thermal Management in Electronic Packaging

Si Chen

ISBN: 978-91-7597-204-6

© Si Chen, 2015.

Doktorsavhandlingar vid Chalmers tekniska högskola

Ny serie nr 3885

ISSN 0346-718X

Technical Report MC2-310 ISSN 1652-0769

CHALMERS UNIVERSITY OF TECHNOLOGY

Department of Microtechnology and Nanoscience - MC2 BioNano Systems Laboratory SE-412 96 Göteborg Sweden Telephone +46 (0) 31-772 1000

Printed by Chalmers Reproservice Göteborg, Sweden 2015

# Abstract

Electronic packaging, protecting the fragile chip from atmosphere and providing the paths for signal transmission as well as heat dissipation, is one of the most important parts in electronic devices. The cost, dimensions, performance, and reliability of an electronic device therefore strongly depend on its packaging structures and materials. In recent years, the miniaturization and diversification of electrical devices, having increased packaging and power density, pose a serious challenge to the reliability of traditional packaging materials. To address this challenge, several nanomaterials were thus fabricated and used for either interconnection or heat dissipation in the electronic packaging.

For interconnection, vertically aligned carbon nanotubes (VACNT) grown with thermal chemical vapor deposition (TCVD) method were used as filling materials of through silicon vias (TSV). Meanwhile, vertically aligned carbon nanofibers (VACNF) fabricated with plasma enhanced chemical vapor deposition (PECVD) method were used as not only the bump material for chips, but also for the reinforcement material for solder joints. By using these carbon nanomaterials, some failure modes, such as burnout, electromigration, and coarseness, can be avoided. Besides carbon, alloy and semiconductor nanomaterials were also fabricated in this thesis for interconnection. Sn3.0Ag0.5Cu (SAC305) alloy and Bi<sub>2</sub>Te<sub>3</sub> semiconductor nanopowders were mixed with traditional Sn58Bi and SAC305 lead free solders respectively in order to improve the shear strength and thermal fatigue resistance of solder joints. The dislocation movement and crack propagation can be effectively delayed by uniformly distributed nanoparticles in the solder matrix. However, it always shows a performance degradation when the content of nanoparticles passes a threshold. This phenomenon could be caused by increased voids and the agglomeration of nanoparticles in the solder matrix with increased content of nanoparticles.

For heat dissipation, a polyimide (PI) network enhanced indium thermal interface material (TIM) was developed as a passive heat dissipation solution, and meanwhile a nanostructured bulk thermoelectric (TE) material constructed of Ag and Bi<sub>2</sub>Te<sub>3</sub> nanopowders is presented as an active heat dissipation solution. The mechanical properties of pure indium TIM can be improved by the PI network without any degradation of heat dissipation ability. This is attributed to the Ag-coated PI fibers which formed solid bonding with the indium matrix and constrained the crack propagation. For the TE material, the thermal conductivity of nanostructured Bi<sub>2</sub>Te<sub>3</sub> samples was much lower than that of raw materials due to the increased phonon scattering at the grain boundaries, which consequently led to a higher figure of merit (ZT value).

**Keywords:** electronic packaging, nanomaterial, characterization, interconnect, heat dissipation, through silicon via, solder, thermal interface material, thermoelectric.

# **List of Publications**

The thesis is based on the following papers:

# Paper A: Through-silicon vias filled with densified and transferred carbon nanotube bundles

T. Wang, S. Chen, D. Jiang, Y. Fu, K. Jeppson, L. Ye, and J. Liu

IEEE Electron Device Letters, vol. 33, no. 3, pp. 420–422, 2012.

# Paper B: Ultra-short vertically aligned carbon nanofibers transfer and application as bonding material

S. Chen, D. Jiang, C. Zandén, Z. Hu, Y. Fu, Y. Zhang, L. Ye, and J. Liu

Soldering & Surface Mount Technology, vol. 25, no. 4, pp. 242–250, Sep. 2013.

# Paper C: A solder joint structure with vertically aligned carbon nanofibres as reinforcements

S. Chen, D. Jiang, L. Ye, and J. Liu

Electronics System-Integration Technology Conference (ESTC), 2014, 2014, pp. 1–6.

Paper D: A reliability study of nanoparticles reinforced composite lead-free solder

S. Chen, L. Zhang, J. Liu, Y. Gao, and Q. Zhai

MATERIALS TRANSACTIONS, vol. 51, no. 10, pp. 1720–1726, 2010.

### Paper E: Sn-3.0Ag-0.5Cu nanocomposite solder reinforced with Bi<sub>2</sub>Te<sub>3</sub> nanoparticles

S. Chen, X. Luo, D. Jiang, L. Ye, M. Edwards, and J. Liu

Accepted by the journal of IEEE Transactions on Components, Packaging and Manufacturing Technology.

Paper F: Characterization of mechanical and thermal performance of a novel nanocomposite thermal interface material for electronic packaging

S. X. Sun, S. Chen, C. Zandén, X. Luo, L. Ye, and J. Liu

Submitted.

Paper G: A high performance Ag alloyed nano-scale n-type Bi<sub>2</sub>Te<sub>3</sub> based thermoelectric material

S. Chen, N. Logothetis, L. Ye, and J. Liu

Accepted by Materials Today: Proceedings.

Other journal and conference papers not included due to being out of the scope of this thesis:

#### Coffin-Manson equation of Sn-4.0Ag-0.5Cu solder joint

S. Chen, P. Sun, X. C. Wei, Z. N. Cheng, and J. Liu

Solder. Surf. Mt. Technol., vol. 21, no. 2, pp. 48-54, Apr. 2009.

#### Development and characterization of nano-composite solder

J. Liu, S. Chen, and L. Ye

Lead-Free Solders: Materials Reliability for Electronics, K. N. Subramanian, Ed. John Wiley & Sons, Ltd, 2012, pp. 161–177.

#### Selective growth of double-walled carbon nanotubes on gold films

Y. Fu, S. Chen, J. Bielecki, A. Matic, T. Wang, L. Ye, and J. Liu

Mater. Lett., vol. 72, pp. 78-80, 2012.

Formation of three-dimensional carbon nanotube structures by controllable vapor densification

T. Wang, D. Jiang, S. Chen, K. Jeppson, L. Ye, and J. Liu

Mater. Lett., vol. 78, pp. 184–187, 2012.

### Paper-mediated controlled densification and low temperature transfer of carbon nanotube bundles for electronic interconnect application

D. Jiang, T. Wang, S. Chen, L. Ye, and J. Liu

Microelectron. Eng., vol. 103, pp. 177–180, 2013.

#### A highly conductive bimodal isotropic conductive adhesive and its reliability

D. Li, H. Cui, S. Chen, Q. Fan, Z. Yuan, L. Ye, and J. Liu

Ecs Trans., vol. 34, no. 1, pp. 583–588, Mar. 2011.

#### Study on the reliability of fast curing isotropic conductive adhesive

W. Du, H. Cui, S. Chen, Z. Yuan, L. Ye, and J. Liu

Ecs Trans., vol. 34, no. 1, pp. 805–810, Mar. 2011.

### Ultrafast transfer of metal-enhanced carbon nanotubes at low temperature for largescale electronics assembly

Y. Fu, Y. Qin, T. Wang, S. Chen, and J. Liu

Adv. Mater., vol. 22, no. 44, pp. 5039–5042, 2010.

# Flip chip assembly using carbon nanotube bumps and anisotropic conductive adhesive film

X. Zhang, T. Wang, P. Berggren, S. Chen, and J. Liu

Ecs Trans., vol. 27, no. 1, pp. 825-830, Nov. 2010.

#### Thermal elastomer composites for soft transducers

S. Jeong, S. Chen, J. Huo, L. Gravier, K. Gamstedt, J. Liu, S. Zhang, Z. Zhang, Z. Wu

Accepted by the 18th International Conference on. Solid-State Sensors, Actuators and Microsystems (Transducers 2015).

#### Vertically stacked carbon nanotube based interconnects for TSV application

D. Jiang, W. Mu, S. Chen, Y. Fu, K. Jeppson, and J. Liu

IEEE Electron Device Letters, vol. PP, no. 99, pp. 1–1, 2015.

# Abbreviations

- IC integrated circuit

- CSP chip scale packaging

- WLP wafer level packaging

- POP packaging on packaging

- VACNT vertically aligned carbon nanotube

- TSV through silicon via

- VACNF vertically aligned carbon nanofiber

- HIS integrated heatspreader

- TIM thermal interface material

- TE thermoelectric

- CPU central processing unit

- SOP system on packaging

- DIP dual in-line packaging

- PGA pin grid array

- LGA land grid array

- BGA ball grid array

- PTH pin through hole

- PCB printed circuit board

- SMT surface mount technology

- PLCC plastic leaded chip carrier

- QFP quad flat pack

- CTE coefficient of thermal expansion

- PM powder metallurgy

- CVD chemical vapor deposition

- CDCA consumable electrode direct current arc

- TEM transmission electron microscopy

SAC305 - Sn3.0Ag0.5Cu

EDX - energy dispersive X-ray spectrometry

IMC - intermetallic compound

ENIG - electroless nickel immersion gold

TC - thermal cycling

OM - optical microscopy

- DSC differential scanning calorimetry

- ICP MS inductively coupled plasma mass spectrometry

XRD - X-ray diffraction

PI - polyimide

ZT value - dimensionless figure of merit

IR - thermal infrared

MMC - metal matrix composite

# Contents

| Chapter 1 Introduction                                                       | 1  |

|------------------------------------------------------------------------------|----|

| 1.1 Background                                                               | 1  |

| 1.2 Scope                                                                    | 1  |

| 1.3 Outline                                                                  | 2  |

| Chapter 2 Electronic Packaging                                               | 3  |

| Chapter 3 Nanomaterials                                                      | 11 |

| Chapter 4 Interconnect                                                       | 17 |

| 4.1 One-Dimensional Carbon Nanomaterials                                     | 17 |

| 4.1.1 Post-processes for 1D carbon nanomaterials                             | 19 |

| 4.1.2 Applications of 1D Carbon Nanomaterials                                | 23 |

| 4.2 Nanocomposite solders                                                    |    |

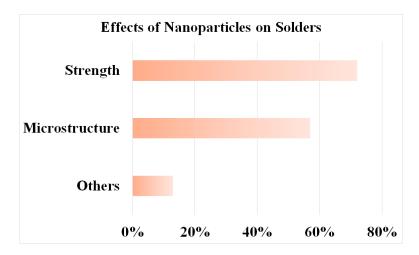

| 4.2.1 Literature review of nanocomposite solders                             | 40 |

| 4.2.2 Two novel nanocomposite solders                                        | 43 |

| Chapter 5 Thermal Management                                                 |    |

| 5.1 Metal matrix nanocomposite thermal interface material for passive heat d | 1  |

| 5.2 Nanostructured thermoelectric material for active heat dissipation       | 66 |

| Chapter 6 Conclusions and Outlook                                            | 73 |

| Acknowledgements                                                             | 75 |

| References                                                                   | 77 |

# **Chapter 1 Introduction**

# 1.1 Background

In recent years, electronic devices have become an essential part of people's life as we need them for work, study, and communication almost every day, which therefore brings a huge market and has boosted the development of electronic industry for decades, especially after the invention of transistor and integrated circuit (IC) [1], [2].

The IC industry has developed rapidly in past 50 years. The density of transistors on the IC doubled every two years according to the prediction of Moore [3]. Driven by the IC industry, the electronic packaging industry also developed quickly because the IC always needs the electronic packaging for mechanical support, signal transmission, and heat dissipation. Since the 1960s, packaging structures and materials have been updated many times in order to make electronic devices smaller and faster. Currently, in most advanced packaging structures, such as chip scale packaging (CSP), wafer level packaging (WLP), and packaging on packaging (POP), the interconnect dimension has shrunk to the micro-and nano-scale, at which the reliability of traditional materials is no longer satisfied. New interconnect materials are therefore urgently required. In addition to interconnection, heat dissipation is another critical issue with advanced packaging structures, especially when these packaging structures combine with a high power IC. The complex structure and materials in the packaging will lead to a high thermal stress and non-uniform heat distribution, which will degrade the reliability of electronic packaging and thus constrain the increase of device performance.

Nanomaterials have been suggested for the manufacturing of electronic devices nowadays due to their unique properties. However, the gap between nanoscience and nanotechnology has greatly limited the application of nanomaterials. For instance, the carbon nanotube, one of the most promising nanomaterials, was reported 25 years ago [4]. Thousands of books and articles have been published, in which the structures, properties, and potential applications of nanotubes have been described systematically. However, it is rare to see a commercial product in today's market due to the high costs for fabricating, controlling, and manipulating carbon nanotubes. In this context, this thesis attempts to combine the nanoscience and nanotechnology in electronic packaging field by using nanomaterials whose properties and performance will be characterized in the packaging structures.

## 1.2 Scope

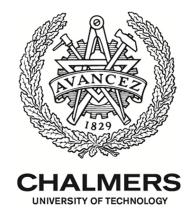

Addressing two urgent issues of advanced electronic packaging, namely interconnect and heat dissipation, several nanomaterials were fabricated and characterized in this thesis. The potential applications of these nanomaterials are demonstrated in Figure 1.1. A pile of chips is attached on the substrate with nanocomposite solders. The signal transmission between chips can be carried out by using vertically aligned carbon nanotube (VACNT) filled

through silicon vias (TSVs), nanocomposite solder bumps, and vertically aligned carbon nanofibers (VACNFs). An integrated heatspreader (IHS) is pressed on the top of stacked chips for heat transfer. The gap between the IHS and the chips is filled with a nanocomposite thermal interface material (Nano-TIM) in which several thin-small nanostructured thermoelectric (TE) coolers are embedded for pumping heat from the hotspots. Above the IHS, a large nanostructured TE cooler sandwiched with two Nano-TIMs is placed between a heat sink and the IHS for increasing the cooling rate.

Figure 1.1: Potential applications of nanomaterials for advanced packaging

## 1.3 Outline

Based on the introduction in Chapter 1, the followed content of this thesis is divided into 5 chapters. Chapter 2 will give a brief introduction to electronic packaging and then review the development and challenges of advanced packaging. Chapter 3 will discuss the type, property, and application of nanomaterials. The fabrication processes for the nanomaterials used in this thesis will be also introduced. Chapter 4 will specify the characterizations and applications of the nanomaterials for interconnect. The content includes VACNT filled TSVs, VACNF bumps, VACNFs reinforced solder joint structure, and nanocomposite solders. In Chapter 5, two nanomaterials will be presented for heat dissipation in the electronic packaging. First of them is the Nano-TIM consisting of a polyimide (PI) network and indium metal. The mechanical properties of Nano-TIM will be mainly discussed. Another material discussed in this chapter is a nanostructured TE material, which is constructed of Bi<sub>2</sub>Te<sub>3</sub> nanopowder and small amount of Ag nanoparticles. Chapter 6 will summarize the results presented in this thesis and give an outlook of nanomaterials.

## **Chapter 2 Electronic Packaging**

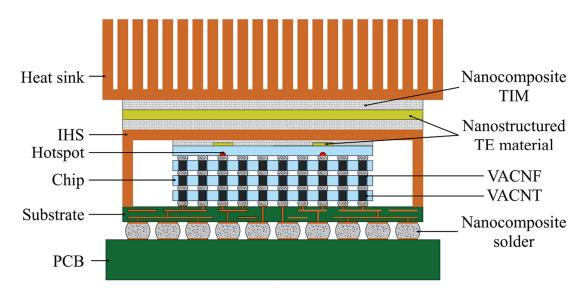

Electronic packaging plays a critical role in electronic devices, and is responsible for signal transmission, heat dissipation, and mechanical support. The cost, performance, and dimension of electronic devices strongly depend on their packaging materials and structures. In the past decade, the development trends of consumer electronics can be summarized as dimensional minimization and functional diversification. A typical industrial case is the Apple iPhone, one of the most popular cellphone productions on the market. Its central processing unit (CPU) frequency increased about 4 times in last 10 years while the dimension (thickness) reduced almost half as shown in Figure 2.1. This remarkable achievement partially attributes to the application of advanced packaging technologies, such as POP and system on packaging (SOP).

Figure 2.1: Development of the Apple iPhone

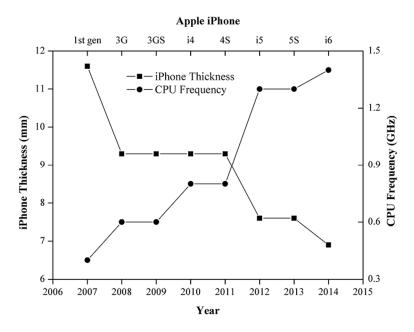

Another industrial case is from Intel, a giant of CPU manufacturing. In the Figure 2.2, the packaging density (pin number/packaging size) of Intel CPUs has continuously increased since 1970 and an exponential growth was presented after 2002. By 2010, the packaging density of Intel CPU has reached 100 cm<sup>-2</sup>, almost 10 times higher than that of 1970. This high packaging density is definitely result of the development of CPU packaging structures, from dual in-line packaging (DIP) to pin grid array (PGA), land grid array (LGA), or ball grid array (BGA) packaging.

Figure 2.2: Packaging density of Intel CPUs

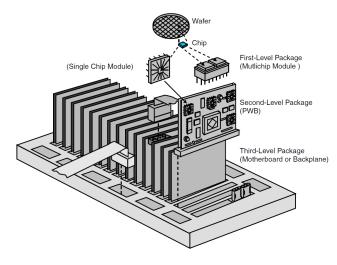

The structure of the electronic packaging is usually constructed with two packaging levels. The first level is called IC-level packaging, which directly interacts with ICs and protects ICs from various environmental impacts, such as moisture, dust, temperature, and force. The second level is named system-level packaging, which creates a platform on a system-level board for the communication between the packaged IC and other required components, such as resistor, capacitor, and diode. In particular, if more than one system-level board is included in a device, an extra packaging level is generally required for the signal transmission among the boards. It can be defined as third-level packaging. The hierarchy of electronic packaging is illustrated in Figure 2.3 [5].

Figure 2.3: Packaging hierarchy

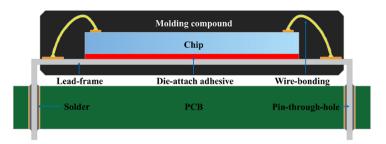

In the history of electronic packaging, hundreds of packaging structures have been developed for increasing the packaging density and shrinking the packaging size. Among them, wire-bonding with pin through hole (PTH) structure described in Figure 2.4 is one of the most typical combinations for the electronic packaging since 1970s. During the packaging process, the back-side of chip will be first attached on a lead-frame with the die-attach adhesive. Then, the pads on the chip surface will be connected with frame legs by using metallic wires. This technology is called wire-bonding. After wire-bonding, the chip and lead-frame will be encapsulated by the molding compound and form a DIP component. This DIP component will be assembled on a printed circuit board (PCB) by inserting and soldering its pins in the PCB holes.

Figure 2.4: A DIP component assembled on the PCB with PTH system-level packaging.

Although wire-bonding with PTH structure has the advantage of cost, it is difficult to further increase the packaging density after 10 cm<sup>-2</sup>. Therefore, the development of new structures and processes for high density packaging became a major topic in 1970s. During this period, a large number of new packaging structures were designed based on two creative technologies. One is flip-chip technology for IC-level packaging, and another is surface mount technology (SMT) for system-level packaging.

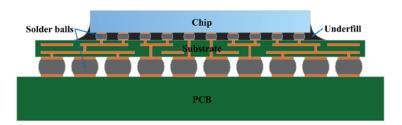

Flip-chip technology was developed by IBM in the 1960s and was used on the IBM System 3 mainframe computer in 1973 [6]. It is named flip-chip because the chip is turned facedown when compared to wire-bonding in which the chip is attached on the lead-frame faceup. In the flip-chip structure, solder balls and the substrate are generally used instead of wires and the lead-frame in the wire-bonding structure as shown in Figure 2.5.

Figure 2.5: Flip-chip and surface mount technology.

SMT was invented in 1950s and started to be used in 1960s [7]. By using SMT, electronic components can be directly mounted on the PCB surface without pin-hole structures. The cost of manufacturing PCB was therefore greatly reduced as the fabrication processes related to the PCB holes were removed from the process line. Meanwhile, the required amount of PCB for a system was also reduced due to increased packaging density.

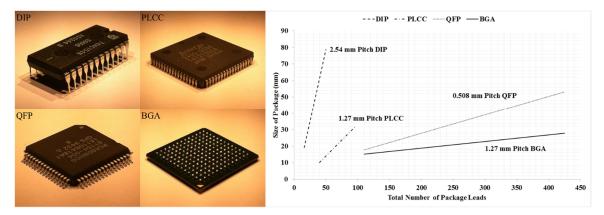

In order to meet the specifications of SMT, a huge number of component structures have been designed. Figure 2.6 gives the images of a typical PTH component (DIP) and three SMT components (PLCC - plastic leaded chip carrier, QFP - quad flat pack, BGA). Meanwhile, the Figure 2.6 also shows the relationship between the packaging size and the lead number for these four components [8] in which all SMT components have higher packaging density than PTH component. Furthermore, the BGA component owns the highest packaging density compared to other SMT components.

Figure 2.6: Images of typical PTH and SMT components and the relationship between packaging size and leads.

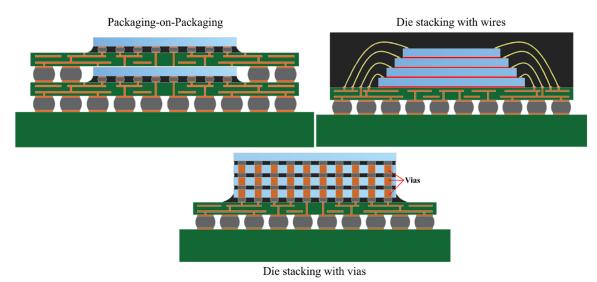

In recent years, the research of electronic packaging has begun to focus on 3-dimensional (3D) structures in order to increase the packaging density. Figure 2.7 lists two kinds of 3D packaging structures. One is formed by stacking packaged chips in the vertical direction,

which is named POP packaging. Another is constructed with a pile of chips and it is called a die stacking structure. The communication between the chips can be built-up by using wires at the peripheral areas of the chip surface or through vias inside the chips.

Figure 2.7: Typical structures of 3D packaging.

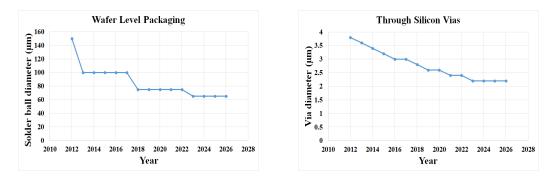

Although 3D packaging can greatly improve the packaging density, it has to face some challenges of packaging materials and processes. The first challenge is related to interconnect materials. Owing to the shrinkage of packaging size, the diameters of pads and vias are becoming smaller and smaller. According to the prediction of International Technology Roadmap for Semiconductors (ITRS) [9], the solder ball and via diameter in 3D packaging will be reduced to the range of micrometer as shown in Figure 2.8, which will lead to a series of reliability issues. For example, the thermal fatigue resistance and isothermal fatigue life of solder joints were severely degraded once the diameter of solder balls decreased to 170  $\mu$ m [10].

Figure 2.8: Development trends of solder ball and through silicon via diameters.

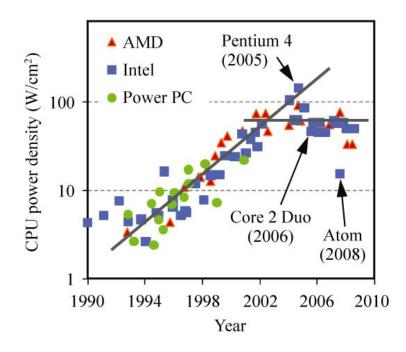

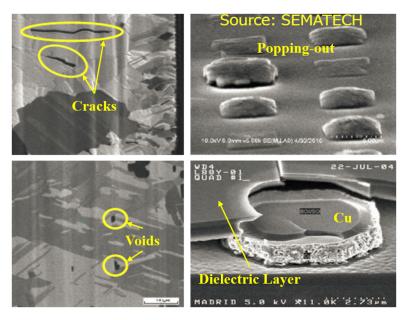

Another major challenge of 3D packaging is thermal management. Figure 2.9 shows the CPU power density in the past two decades [11]. The development of high frequency CPUs has slowed down since 2005 in order to keep the power density lower than 100 W  $\cdot$  cm<sup>-2</sup>. It demonstrates the insufficient ability of current packaging technology to provide sufficient heat dissipation. Moreover, it is quite apparent that the thermal management issue will be more severe in a die stacked structure, in which the complex structure and small interconnect channels will dramatically slow the heat dissipation rate when compared to the single plane structure. For instance, the Cu filled TSV structure suffers from high thermal stress (>200 MPa) in the die stacked structure due to the large coefficient of thermal expansion (CTE) mismatch between Cu and Si (Cu:  $17 \times 10^{-6}$ /K, Si:  $3 \times 10^{-6}$ /K) as shown in Figure 2.10 (SEMATECH technical report).

Figure 2.9: Development trend of CPU power density.

Figure 2.10: Defects in the Cu filled TSV due to high thermal stress.

As the traditional materials are becoming less able to meet the requirements of a high density packaging structure, new packaging materials with outstanding mechanical, electrical, chemical, and thermal properties will be highly desirable. Currently, nanomaterials are one of the most attractive materials for high density packaging. Their unique properties have been gradually discovered and proven in past several decades.

# **Chapter 3 Nanomaterials**

Nano has become an increasingly used word and is most typically used to describe a substance that exhibits unique properties once the size shrinks below 100 nm (the nanoscale). One nanometer is equal to 10<sup>-9</sup> meters, about 50 thousand times smaller than the diameter of a human hair [12]. Driven by the considerable interest in the nanoscale, two new research fields named nanoscience and nanotechnology have been established. According to the definition given by the Royal Society and Royal Academy of Engineering in the UK, nanoscience is the study of phenomena and manipulation of materials at atomic, molecular, and macromolecular scales, where properties differ significantly from those at a larger scale. Meanwhile, nanotechnologies are the design, characterization, production, and application of structures, devices, and systems by controlling shape and size on the nano-scale. These two new areas can be closely linked by the development of nanomaterials [13].

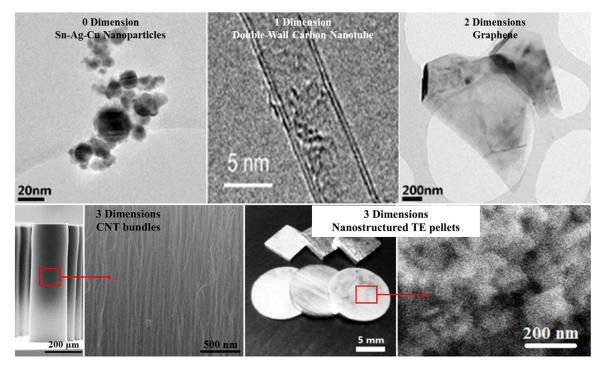

A nanomaterial is a material where some controllable relevant dimension is of the order of 100 nm or less [14]. Nanomaterials can be classified according to the number of dimensions as shown in Figure 3.1. Zero-dimensional (0D) nanomaterials means the materials are nanoscale in all dimensions. Nanoparticles are one of the most common 0D nanomaterials. One-dimensional (1D) nanomaterials are described as a material where one dimension is greater than nanoscale, such as nanowires and nanotubes. Carbon nanotube shown in the Figure 3.1 is a typical case of 1D nanomaterials. Two-dimensional (2D) nanomaterials usually relates to film materials where only the thickness must be in the nanoscale. Currently, single-layer graphene, consisting of only one layer of carbon atoms, has been regarded as one of the most promising 2D nanomaterials. 3D nanomaterials are defined as special bulk materials which are built with 0D, 1D, or 2D nanomaterials. 3D nanomaterials are sometimes quite similar to those normal bulk materials in appearance but have quite special microstructures and properties.

Figure 3.1: Types of nanomaterials classified by the number of dimensions.

Most nanomaterials have a large surface area which is the root of their many special properties. For instance, the melting point of metallic particles, such as Al [15], Sn [16], Sn-Ag-Cu [17], and Sn-Co-Cu [18], can be decreased by 10 - 100 °C by reducing the particle diameter to the nanoscale. This provides a huge benefit to powder metallurgy (PM) and the soldering industry. It has shown that the required process temperature for sintering Fe nanosized particles is almost 50 % lower than for large particles [19]. The temperature of soldering processes can also be decreased by using nanosized solder alloys. In the chemical industry, nanosized particles have been used as high efficiency catalysts due to their large surface area to the volume aspect ratio [20]. Besides their use as base materials, nanomaterials can also be used as effective reinforcement materials in a composite due to their small size and extraordinary properties. For instance, the strength of Cu was enhanced more than 2 times by using CNTs [21] or graphene [22] as reinforcement. The thermal conductivity of Ag filled conductive adhesive was approximately doubled by adding Agcoated SiC nanoparticles [23].

As more and more unique properties of nanomaterials have been found and applied in different fields, various fabrication techniques of nanomaterials have been invented. Currently, the methods for fabricating nanomaterials can roughly divide into two techniques, namely top-down and bottom-up techniques. Top-down techniques are those in which the particles are fabricated from bulk material, and bottom-up techniques are those in which the particles are built atom by atom, or molecule by molecule [24]. The fabrication methods like ball-milling, mechanical exfoliation, Consumable electrode Direct Current Arc (CDCA), and electrospinning are typical top-down techniques.

vapor deposition (CVD) and the chemical reduction method are two popular bottom-up techniques. In the practice, shaping materials to the nanoscale is just first step for the application of nanomaterials. Post-processes, such as high temperature annealing and surface functionalization, are usually required in order to obtain high quality structures or achieve expected functions.

### Chemical Vapor Deposition

CVD forms a thin film on the surface of a substrate through thermal decomposition or the reaction of gaseous compounds. The desired materials are deposited directly from the gas phase on to the surface of the substrate [28]. CVD is a common method for producing VACNT and VACNF. A major advantage of the CVD method for growing VACNT and VACNF is its compatibility with the standard lithography process. The carbon from source gases like  $C_2H_2$  and  $CH_4$  is deposited on the patterned catalyst particles for building CNT or CNF structures. The catalyst particles are generally formed by annealing a catalyst layer with the thickness of several nanometers at high temperature.

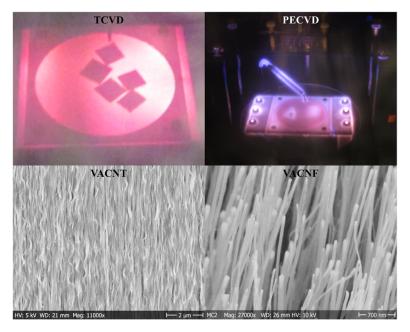

In this thesis, VACNT was synthesized with a thermal CVD (TCVD) method. A patterned catalyst layer, consisting of 10 nm Al<sub>2</sub>O<sub>3</sub> and 1 nm Fe, was formed on a Si chip by using standard photolithography and evaporation processes. The growth process was finished in a commercial machine named Black Magic (Aixtron). The chip was first placed on a graphite heater and heated up to 500 °C at a rate of 300 °C/min in a 692 standard cubic centimeter per minute (sccm) H<sub>2</sub> flow and then annealed 3 min to form discrete catalyst particles. After that, the heater temperature was quickly raised to 700 °C. Meanwhile, a  $C_2H_2$  flow of 200 sccm was injected to the growth chamber for CNT growth. The height of VACNTs is controlled by the growth time. When growth is finished, the Si chip with as-grown VACNTs were cooled down to the room temperature by using a 1000 sccm N<sub>2</sub> gas flow.

VACNFs were also grown by using Aixtron machine. A 7 nm Ni catalyst layer was evaporated on the chip before growth process. Then, a 5 min annealing step was carried out at 625 °C to form discrete Ni catalyst particles. During the annealing process, NH<sub>3</sub> gas was injected into the process chamber with 200 sccm flow rate for preventing the catalyst from oxidation. After the annealing process, the temperature of the heater was increased to 700 °C and a 40 sccm  $C_2H_2$  gas flow was added as carbon source for VACNF growth. The 600 V DC plasma was applied to the growth process in order to promote the gas ionization.

The Figure 3.2 shows the growth process and morphology of as-grown VACNTs and VACNFs. The graphite heater is red in color due to the high process temperature. The blue plasma glow can be observed in the chamber of PECVD process. According to the scanning electron microscopy (SEM) images, the diameter and pitch between VACNFs are much larger than for VACNTs while the height is much shorter. This difference in morphology between VACNT and VACNF determines their specific applications and post-processes in this study.

Figure 3.2: VACNTs and VACNFs fabricated with TCVD and PECVD method respectively

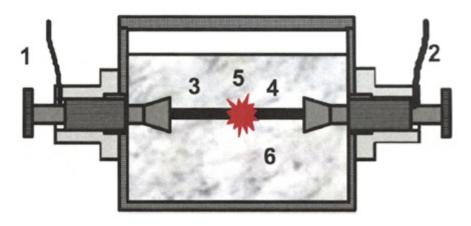

## Consumable Electrode Direct Current Arc

CDCA is a promising top-down technique for fabricating nanomaterials in a large scale. This technique is originally invented for cutting and shaping hard or brittle materials for mechanical manufacturing. It was then applied for producing various fine powders since 1960s [25], such as metals [26][27], semiconductors [28], carbon [4][29], and even ceramic materials [30]. Figure 3.3 shows a typical manufacturing setup of the CDCA technique [31]. In principle, the arc (or a plasma channel) will be triggered once the dielectric liquid between two electrodes breaks down at high voltage. The tremendous energy and pressure near the arc can increase the surface temperature of the electrodes to around 10,000 K in only few microseconds [32]. As a result, the electrodes will be melted and evaporated. The molten part will quench in the dielectric liquid, forming microsized materials. Meanwhile, there will be nanosized materials in the evaporated part after solidifying in the dielectric liquid [33]. Although the setup of CDCA is simple, the process control is difficult. Many parameters, such as feeding speed, the distance between the electrodes, electrode diameter, power, and the viscosity of dielectric liquid, can significantly affect the quality and yield of nanomaterials. Therefore, each parameter must be carefully adjusted for different materials.

Figure 3.3: Schematic picture of CDCA set-up: (1) cathode, (2) anode, (3) and (4) electrodes, (5) spark, (6) dielectric coolant.

### Electrospinning

Electrospinning technique is an old technique, the history of which can even date back to the 1745 when Bose described the formation of aerosols formed by electrical potentials on the surfaces of droplets. However, this technique has not been widely used for fabricating fibers until that Baumgarten reported on the electrospinning of acrylic microfibers and Larrondo and Manley reported a series of papers on the electrospinning of polymer melts in the 1970s [34]. Although the electrospinning technique has been around for hundreds of years its complex mechanism has only recently been explained in recent years with the assistance of a high speed camera. The basic setup and the mechanism of electrospinning are described in Figure 3.4. When a high voltage is applied between a metallic needle and a grounded conductive collector, the conical polymer droplet (Taylor cone [35]) will be formed at the nozzle of the needle due to the electrostatic force. If this electrostatic force overcomes the surface tension of the polymer solution, a liquid jet will be launched toward the collector. This electrically charged jet maintains a straight motion at the beginning of travel, and then will travel in an unstable bending motion due to the repulsive forces in the charged jet [36]. Owing to the continuous stretching and whipping during the travel from the needle and collector, this jet is finally shaped into a thin and long fiber, landing on the collector [37]. The right side of Figure 3.4 shows a SEM image of a PI film fabricated with the electrospinning technique. The average diameter of the fibers in this film is 780 nm [38]. The film was then heated at 320 °C for 1 hour in order to evaporate the residual solvent.

Figure 3.4: Basic electrospinning setup and PI network used in this thesis

In summary, the study of nanomaterials has achieved a lot of valuable results in recent years but some problems still need to be addressed. For example, the agglomeration of nanomaterials is still a critical issue in nanocomposite materials. Owing to the high surface energy [39], uniformly dispersed nanomaterials in nanocomposite materials is difficult to achieve. Although dispersants can be used on the surface of nanoparticles for breaking the agglomeration [40], [41], the effects of these dispersants on the properties of nanomaterials, such as conductivity and surface activity, must be carefully considered. Another critical problem of nanomaterials is related to the productivity and cost. Currently, some specific suppliers have started to provide commercial nanomaterials in the market, but the price is normally in the range of 10 to 100 USD/gram which is too high for the electronics industry, especially for the consumer electronic market.

# **Chapter 4 Interconnect**

In electronic devices, signal transmission and mechanical connection are usually carried out by using interconnect materials, such as Cu traces, Au wires, conductive adhesives, and solder bumps. Therefore, interconnect materials play an important part in the electronic packaging. Every critical property of interconnect materials, such as melting point, surface energy, stiffness, mechanical strength, toughness, fatigue resistance, chemical resistance, temperature stability, electrical conductivity, maximum current density, and CTE, must be evaluated during the electronic packaging design. In this chapter, focusing on the reliability issues in the 3D packaging, two types of nanomaterials were manufactured and characterized. One of them is 1D carbon-based nanomaterials, including VACNT and VACNF. VACNTs were used as filling materials in TSVs, and VACNFs were used as bump materials for flip-chip technology as well as reinforcement materials for solder joint structure. Another material will be presented in this chapter is nanosized particles, which were mixed in the traditional lead-free solders in order to enhance the strength and thermal fatigue resistance of solder joints.

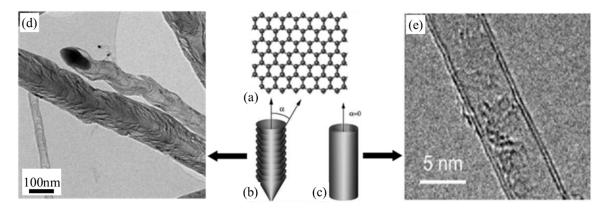

## 4.1 One-Dimensional Carbon Nanomaterials

CNT and CNF are two major 1D carbon nanomaterials. As far as the structure is concerned, both CNT and CNF can be described as a rolled graphene sheet. The difference is the rolling angle between the rolling axis and the sidewall. If this angle is equal to zero, the CNT structure can be formed, otherwise a conical structure will be presented. The CNF structure can be formed by stacking a pile of this kind of cones in one direction. The schematic pictures and transmission electron microscopy (TEM) images of CNT and CNF are shown in Figure 4.1.

Figure 4.1: Schematic drawings of graphene (a), CNF (b) and CNT structure (c) [42]. TEM pictures of CNF (d) and CNT (e) [43].

Owing to the unique structures, CNT and CNF have many special properties which are needed for advanced packaging. Some of them are listed in Table 4.1 [44]–[48]. The nanosized diameter of CNT and CNF can satisfy the fine pitch requirement of high density packaging. Meanwhile, the high current density and thermal conductivity of CNT and CNF are benefit to high power devices. The low CTE, high strength, and lateral flexibility of 1D carbon nanomaterials are essential properties for building a high reliability device. In addition, some issues in traditional interconnect materials, such as electromigration, coarsening, and decomposition, can be addressed by using carbon materials due to their excellent stability.

Compared to CNT, CNF shows lower performance in terms of conductivity, stability, and reliability due to its cone-stacked structure. The angle of cone structure means that the charge transport direction is not only decided by the axial direction like CNT. The van der Waals bonding between cones also determines the mechanical strength cannot compare with covalent bonded CNT. Meanwhile, the chemical property of CNF is not so stable due to its exposed edges [42]. However, CNF still has the advantage of process compatibility [49]. The average diameter and spacing between CNFs is almost 10 times larger than CNT. Moreover, the aspect ratio of CNF is much smaller than CNT. These properties make CNF more compatible to traditional IC processes and convenient to be manipulated compared with CNT. For example, owing to the proper spacing and aspect ratio, the sputtering process can be an efficient method for coating CNF surface.

| Property                                                                      | CNF     | CNT       |

|-------------------------------------------------------------------------------|---------|-----------|

| Average Diameter<br>(nm)                                                      | 55      | 4         |

| Average Tube Spacing (nm)                                                     | 300     | 20        |

| Aspect Ratio                                                                  | 100     | 175000    |

| Electrical Conductivity<br>(×10 <sup>6</sup> S·m <sup>-1</sup> )              | 2       | 0.1~1     |

| Maximum Electric<br>Current Density<br>(x10 <sup>6</sup> A·cm <sup>-2</sup> ) | 3       | 4000      |

| Thermal Conductivity<br>(W·m <sup>-1</sup> ·K <sup>-1</sup> )                 | 2000    | 3000-6000 |

| Coefficient of Thermal<br>Expansion (x10 <sup>-6</sup> K <sup>-1</sup> )      | -1      | -1.5±0.2  |

| Tensile Strength (GPa)                                                        | 8.7     | 150       |

| Density (g·cm <sup>-3</sup> )                                                 | 1.4~1.6 | 1.33~1.4  |

Table 4.1: Properties of CNT and CNF

Although 1D carbon nanomaterials own many advantages, they also face a lot of difficult challenges in the practical application. First major challenge is the harsh growth condition. The growth temperature of carbon nanomaterials is usually higher than 600 °C which is a harmful temperature to most electronic materials. In recent years, some low temperature processes (around 150 to 200 °C) have been reported for CNF [50] and CNT [51] growth, but unsatisfied material quality constrains the application of these processes. Second challenge of 1D carbon nanomaterials is related to the inert surface of CNT and CNF. It is known that CNT and CNF need to bond with various metallic surfaces as the interconnect materials in the packaging structure. However, the solid bonding between carbon and metallic materials is difficult to be formed unless a metallic coating layer is used on the carbon surface. Currently, some wet chemical processes have been developed for coating vertically aligned [52] and discrete CNFs. These well coated CNTs and CNFs can be the promising materials for specific applications, such as making fuel cell or composite materials. However, wet coating processes are not suitable for IC-level packaging and can destroy the alignment of VACNTs and VACNFs or pollute the surface of ICs. Therefore, physical coating processes, such as sputtering or evaporation, appear to be more compatible with current IC fabrication processes. However, these processes can just work for those VACNTs and VACNFs with sparse distribution and small aspect ratio.

## 4.1.1 Post-processes for 1D carbon nanomaterials

### Transfer Process

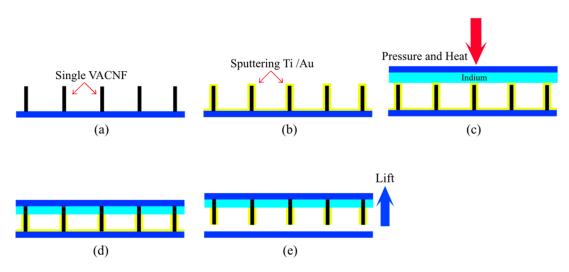

Owing to the high growth temperature, as-grown VACNT and VACNF have to be transferred from the growth chip to another chip. Currently, two transfer methods have been developed by Y. Fu, [53], S. Chen et al. [54]. One method is developed by using an indium layer on the target chips, and another is depended on the Au-Au bonding.

The indium layer assisted transfer process for VACNF transfer is described in Figure 4.2. In the beginning of the process, 20 nm Ti and 100 nm Au were sputtered on the surface of CNFs. After sputtering, the transfer step was carried out by using an indium coated target chip, as shown in Figure 4.2 (c), with a flip-chip bonder which can control heating temperature, time, and pressure. The thickness of indium layer is 1  $\mu$ m. The Ti/Au coated VACNFs on the growth chip was pressed on the indium coated target chip with 5 MPa pressure at 160 °C. The duration of heating step is 20 s. In this period, indium melted and wetted the tip of the CNF, forming a bonding between indium layer and CNF. This bonding held the CNF and pulled it out from the growth chip during the separation step as shown in Figure 4.2 (e). The wetting area of indium on the CNF must be well controlled during the heating step. If the indium covers whole CNF and further spread to the surface of the Ti/Au coated growth chip, the reaction between indium and Ti/Au will cause the formation of the metallic bonding at the surface of growth chip. In this case, owing to the comparable bonding force at both sides of CNF, the complete transfer of VACNFs will be extremely difficult.

Figure 4.2: Schematic description for VACNF transfer process: (a) VACNFs were grown on the growth chip with PECVD method, (b) 20/100 nm Ti/Au metallic layer was coated on the surface of VACNFs with sputtering process, (c) target chip with 1  $\mu$ m In layer was pressed on the growth chip with heating, (d) VACNFs were wetted by In at 160°C, (e) target chip was separated from the growth chip at room temperature.

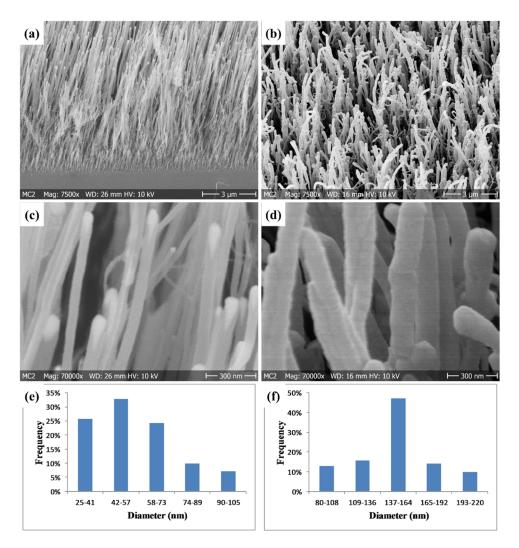

The morphology of VACNFs before and after sputtering process is shown in Figure 4.3 (a) and (b). After sputtering, the VACNFs can still retain straight but the morphology has changed. The close-up views of VACNFs in Figure 4.3 (c) and (d) show that the VACNFs are well covered by metallic layer, and the average diameter of VACNFs was increased from 55 nm to 147 nm after the sputtering process as shown in Figure 4.3 (e) and (f). The 92 nm increasing at the diameter is consistent with the setting thickness of sputtering machine.

Figure 4.3: SEM pictures of VACNFs before (a) (c) and after (b) (d) Ti/Au sputtering process. Statistic of VACNF diameter before (e) and after (f) the sputtering process.

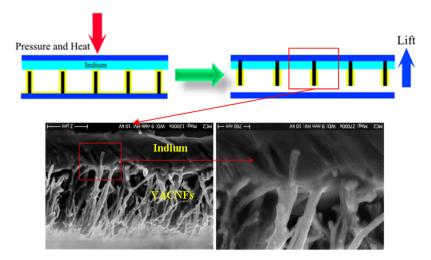

Figure 4.4 shows the VACNFs on the surface of the indium coated target chip after the transfer process. In the figure, most transferred VACNFs are still as straight as before. Furthermore, the tips of VACNFs have embedded into the indium layer at least 500 nm depth which gives a high transfer rate in this study.

Figure 4.4: SEM observations of transferred VACNFs.

The processes for transferring VACNT bundles are quite similar to VACNFs. The process parameters for transferring VACNTs and VACNFs are listed in Table 4.2. Compared with VACNTs, shorter duration time is used for VACNFs due to the height limitation. The controllable height of VACNFs (around several micrometers) in this study is much shorter than that of VACNTs (several hundred micrometers), which extremely increases the sensitivity of transfer successful rate to the transfer parameters and conditions. As the VACNFs are so short, the dust at the surface of the chips can even affect the transfer result. Therefore, the process window for transferring VACNFs is quite narrow. Although researches have put a lot of effort into increasing the growth rate of VACNFs [42], the height of VACNFs is still limited in the range of several micrometers.

Table 4.2: Process parameters for transferring VACNT and VACNF

| Transfer parameters | VACNT | VACNF |

|---------------------|-------|-------|

| Temperature (°C)    | 170   | 160   |

| Pressure (MPa)      | 6.4   | 5     |

| Duration time (s)   | 120   | 20    |

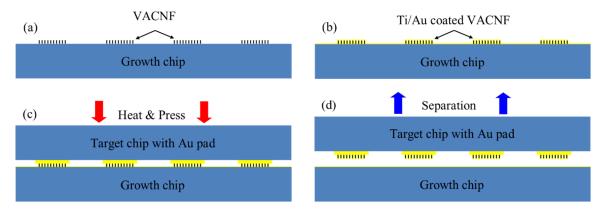

Indium layer assisted transfer method is capable of transferring both VACNFs and VACNTs, but the high cost, oxidation [55], low strength [56], and low abundance [57] of indium are potential barriers of this method. Therefore, another transfer method depended on Au-Au bonding technique was studied. Figure 4.5 shows the VACNF transfer process with Au-Au bonding technique. VACNFs were grown on a patterned Si chip by using PECVD method as shown in Figure 4.5 (a). After the growth and sputtering process, the VACNFs were aligned and pressed to a target chip with Au pads by using the flip-chip bonder as shown in Figure 4.5 (c). The size of the Au pads on the target chip is 500 µm in

diameter. The optimized temperature, pressure, and duration time are set at 300 °C, 10 MPa, and 5 minutes respectively. After the bonding process, this target chip was separated from the growth chip once the temperature decreased to 40 °C as shown in Figure 4.5 (d).

Figure 4.5: Au-Au bonding transfer process: (a) growing VACNFs with the PECVD method, (b) Ti/Au coating on the surface of each carbon nanofiber, (c) hot-pressing target chip on growth chip with flip-chip machine, (d) cold-separating target chip from growth chip.

### Densification Process

The VACNT bundles fabricated with TCVD method are extremely loose materials in which more than 90 % of volume is occupied by the spacing between CNTs [58]. Apparently, this loose structure will decrease the performance related to the cross-section area, such as tensile stress and electrical conductivity. Unlike the VACNFs, the spacing between VACNTs is as narrow as 20 nm, at the same time, the aspect ratio of VACNTs can be as high as 175000. In this case, the spacing between CNTs is difficult to be full filled with physical method, like sputtering. Therefore, some research efforts begun to convert from filling the spacing to densifying the VACNT bundles. In this thesis, a vapor method was used for the densification of VACNT bundles. The VACNT bundles were exposed to the water diluted acetone at 75 °C. Once the acetone vapor condenses on the surface of CNT, CNTs will stick to each other due to the surface tension of acetone. After the acetone evaporates from VACNT bundles, a dry and densified VACNT bundles can be formed.

## 4.1.2 Applications of 1D Carbon Nanomaterials

CNT has many excellent properties, such as high current carrying capacity, thermal conductivity, Young's modulus, and lateral flexibility. These outstanding properties have been used in various fields in which many valuable results have been achieved. For instance, CNT has been used in the lead-free solders as reinforcement in order to increase the

mechanical performance [59], [60]. It was also used as thermal interface materials to fill the gap at the interface [61].

### Application 1: Vertically aligned carbon nanotube filled through silicon vias

In recent years, CNT is considered as a promising filling material for the TSVs of die stacking structures. Table 4.3 lists several properties which should be considered as priorities for developing the filling materials of TSVs [44]–[46]. Compared with the properties of Cu, the properties of CNT show a clear advantage in every aspect except the electrical conductivity. CNT can stand high current density and transfer heat quickly. Meanwhile, CNT bundles have high mechanical strength and light weight which appear to be more and more important to recent consumer electronics.

| Property                                                                    | Copper | CNT       |

|-----------------------------------------------------------------------------|--------|-----------|

| Electrical<br>Conductivity<br>(×10 <sup>6</sup> S·m <sup>-1</sup> )         | 59.6   | 0.1~1     |

| Electric Current<br>Density (x10 <sup>6</sup> A·cm <sup>-2</sup> )          | 0.1    | 4000      |

| Thermal Conductivity<br>(W·m <sup>-1</sup> ·K <sup>-1</sup> )               | 385    | 3000-6000 |

| Coefficient of<br>Thermal Expansion<br>(x10 <sup>-6</sup> K <sup>-1</sup> ) | 17     | -1.5±0.2  |

| Tensile Strength<br>(GPa)                                                   | 0.22   | 150       |

| Density (g·cm <sup>-3</sup> )                                               | 8.92   | 1.33~1.4  |

Table 4.3: Comparison between copper and CNT

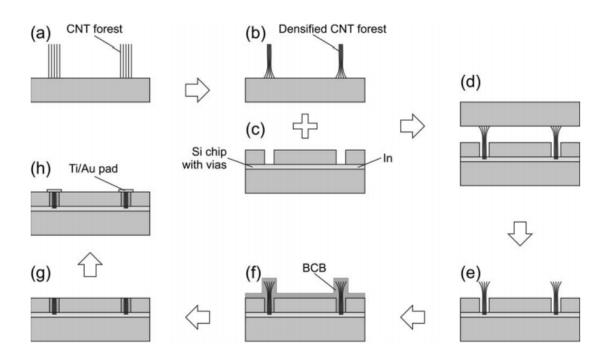

A series of processes described in Figure 4.6 were developed in order to fill the TSVs with VACNT bundles. The VACNT bundles grown with TCVD method were first densified with the vapor method and then transferred into the vias with indium layer assisted transfer method. After that, the space between VACNT bundles and the sidewall of vias is filled with benzocyclobutene (BCB) by using spinning coating process. The rugged surface shown in the Figure 4.6 (f) was then flatted by using a planarization process. Finally, a Ti/Au layer was deposited on the VACNT filled vias as metallic pads.

Figure 4.6: Process description of VACNT filled TSV. (a) VACNT growth with TCVD method; (b) VACNT densification with the vapor method; (c) target chip with the indium layer and vias; (d) and (e) VACNT transfer process; (f) filling gap between VACNT and via by using BCB; (g) planarization process; (h) Ti/Au deposited pads.

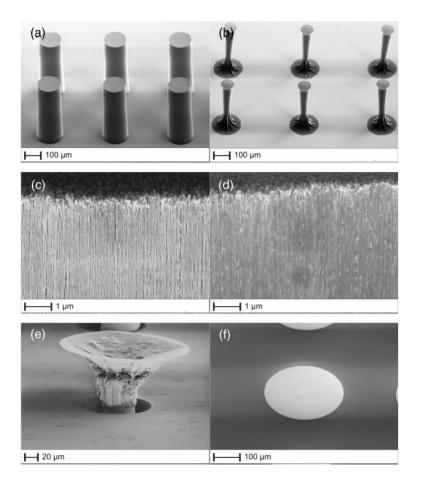

SEM observations of critical steps in the process are shown in Figure 4.7. Comparing Figure 4.7 (a) with (b), the shrinkage of VACNT bundles in diameter is as high as 70 %. The high magnification images of the sidewall of the VACNT bundles before and after densification are shown in Figure 4.7 (c) and (d). The number of the visible chinks on the sidewall of VACNT bundles was obviously decreased after the vapor densification process. Figure 4.7 (e) shows a densified VACNT bundle inside a via after the transfer process. The diameter of the via is 100  $\mu$ m. The root of VACNT bundle (mushroom head shape) exposed from the via opening will be polished away with the planarization process. A Ti/Au pad formed on the top of via is shown in the Figure 4.7 (h), which will be used for making the bonding between TSVs and other materials, such as solders or conductive adhesives.

Figure 4.7: SEM images of critical steps in the process of VACNT filled vias. (a) as-grown VACNT bundles; (b) densified VACNT bundles; (c) and (d) VACNT sidewalls before and after densification process; (e) VACNT filled vias; (f) Ti/Au pads on the top of vias.

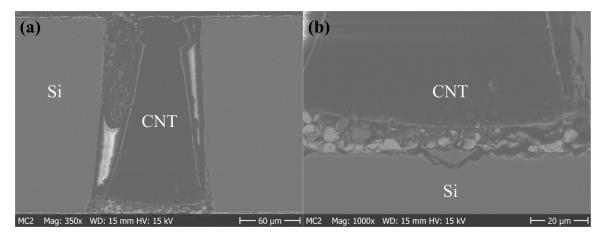

A cross-section of VACNT filled vias is shown in Figure 4.8 in which no obvious deformation of VACNT can be observed after transfer and planarization processes. Owing to the larger shrinkage at the CNT waist than the head, the CNT in the via shows a conical shape after removing the mushroom head. Figure 4.8 (b) shows the interface between the CNT and the Si chip. Although the structure of interface has been broken during polishing process, a bonding layer can be still recognized.

Figure 4.8: Cross-section of VACNT vias: (a) VACNT in the vias; (b) close-up view of CNT/Si interface.

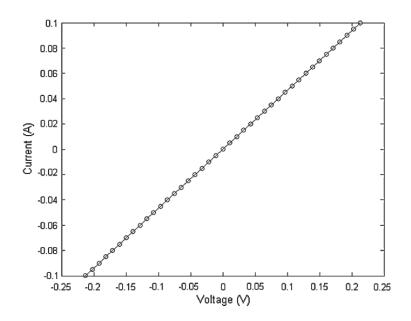

The electrical performance of VACNT vias was measured with four probe method. Figure 4.9 exhibits an expected linear relationship between the current and voltage. The electrical resistivity of  $3.9 \times 10^{-5} \ \Omega \cdot m$  of VACNT vias was achieved, which is about an order of magnitude lower than that of un-densified VACNT filled vias.

Figure 4.9: I-V curve of densified VACNT filled vias.

#### Application 2: Vertically aligned carbon nanofiber bumps

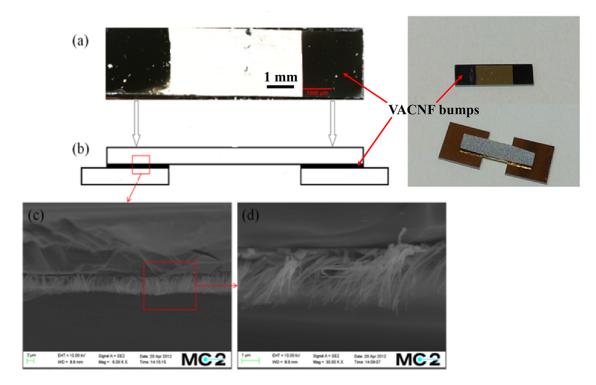

VACNF bumps were fabricated based on aforementioned growth and transfer processes. In order to measure the electrical and mechanical performance of VACNF bumps, two sample structures were designed. One is a bridge structure sample as shown in Figure 4.10 (a) and (b), which is used for electrical resistance measurement. This structure was formed by transferring the VACNFs to the two sides of a rectangular Si chip with the indium assisted transfer method and then mounting this Si chip on another two square Au coated Si chips with flip-chip bonder. Compared with the transfer process, the mounting process has a longer duration time and higher temperature and pressure in order to ensure the remelted indium can wet entire CNF and reach the surface of Au coated square chips, forming a solid In-Au bonding. The cross-section of the bridge sample was shown in Figure 4.10 (c) and (d), in which the VACNFs are slight bent which is caused by the higher pressure loading in the mounting process. In addition to VACNFs, three traditional materials, Sn3.0Ag0.5Cu (SAC305), Ag filled conductive adhesive, and pure indium, were also tested with the same sample structure as VACNFs.

Figure 4.10: Bridge structure sample for electrical test: (a) indium coated rectangular Si chip with VACNF bumps, (b) schematic pictures of bridge structure sample, (c) SEM observation of the cross-section of VACNF bumps, and (d) close-up view of the red frame in the image (c).

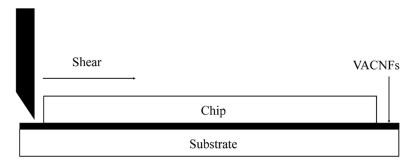

Another sample structure used for shear test is a sandwich structure, as shown in Figure 4.11. The as-grown VACNFs were transferred to an indium coated Si substrate. Then, a gold coated square chip was mounted on the silicon substrate directly by using the same bonding process as the bridge sample.

Figure 4.11: Sandwich structure for shear test

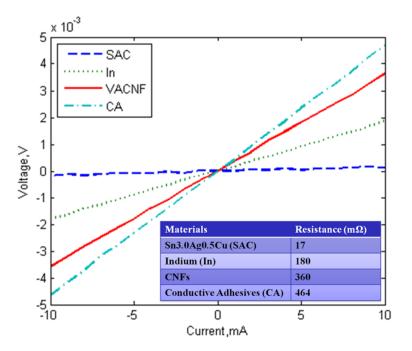

The results of electrical resistance test are shown in Figure 4.12. All samples can show a linear I-V curve. The inset table in Figure 4.12 displays the resistance of four kinds of interconnect materials. It indicates that the electrical performance of VACNFs is comparable with Ag filled conductive adhesive, but it is one order of magnitude lower than metallic materials.

Figure 4.12: The results of resistance measurement

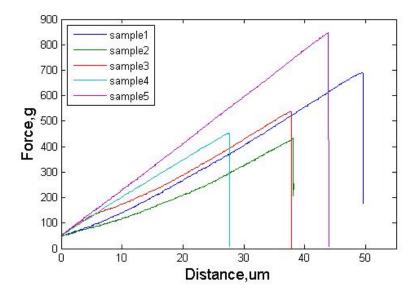

The force-displacement relationship during the shear test was shown in Figure 4.13. All five VACNF samples show the similar force-displacement relationship. The force sharply dropped when the certain displacement was reached. It shows that the fracture mode of VACNF bump is close to brittleness fracture mode. According to the calculation, the average shear strength of VACNF bump is 1.5 MPa. Compared with our previous experimental results [62][63], this value is almost one order of magnitude lower than solders and conductive adhesives.

Figure 4.13: Force-distance relationship during shear test

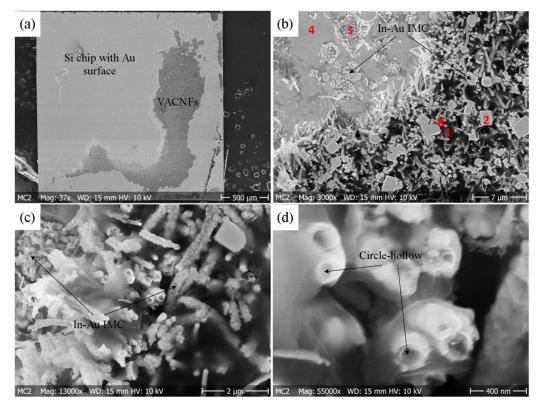

The fracture surfaces after the shear test were observed by using SEM. Figure 4.14 (a) shows that the fracture surface at the chip side consists of two different areas. A close-up view near the boundary of these two areas is shown in Figure 4.14 (b). The VACNFs in the dark area and the Au coated Si surface in the bright area can be easily distinguished. According to the analysis of energy dispersive X-ray spectrometry (EDX), the VACNF surface (point 1) in Figure 4.14 (b) contains In-Au intermetallic compound (IMC) with the atomic ratio of 3:1 as shown in Table 4.4. Meanwhile, some small pieces (point 2 and 3) can be observed in both areas. They also include the In-Au IMC as the VACNF surface. It proves that the melted indium at the substrate side has crossed whole VACNF surface and begun to react with the Au at the Si chip side. Figure 4.14 (c) shows a high magnification picture of the VACNF area. Compared to as-coated VACNF, the surface of VACNF in Figure 4.14 (c) has become quite rough, which is another evidence for the reaction between Au and In on the VACNFs. The cross-section of these broken VACNFs presents a circular-hollow structure as shown in Figure 4.14 (d).

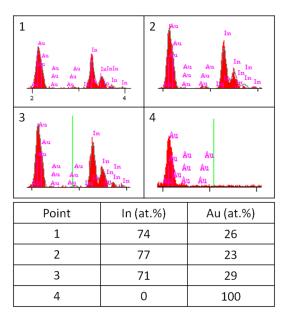

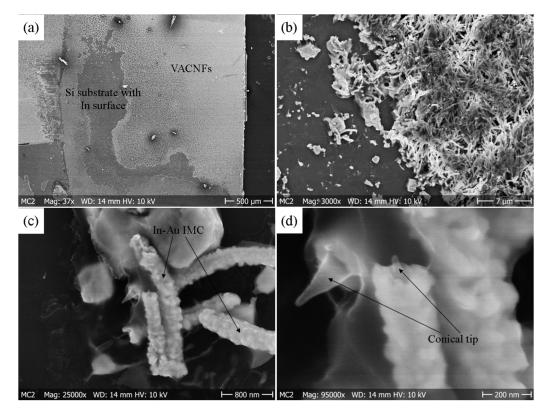

Figure 4.14: Chip side: (a) fracture surface at the chip side, (b) close-up view of the fracture surface, (c) close-up view of the VACNFs area, (d) circular-hollow structure on the cross-section of broken VACNF.

Table 4.4: EDX analysis on the fracture surface at the chip side

Figure 4.15 (a) shows the fracture surface at the substrate side, which agrees well with the surface pattern at the chip side. Figure 4.15 (b) shows a close-up view at the boundary of dark and bright area. In contrast to the chip side, the bright area is covered by VACNFs and the dark area is Si substrate surface. Some small pieces with broken VACNFs can be observed in the Si substrate surface. According to the high magnification image showing in Figure 4.15 (c), the sidewall of these broken VACNFs has been covered by rough In-Au IMC. Figure 4.15 (d) shows the small cones on the cross-section of broken VACNFs. This conical structure is consistent with the circular-hollow structure at the chip side. Combining the cross-section of broken VACNFs at the two sides, we can conclude that the VACNF is easy to be broken at the interface between the cones of CNF. This break structure of CNF was also observed by other researchers [64].

Figure 4.15: Substrate side: (a) fracture surface at the substrate side, (b) close-up view of the fracture surface, (c) close-up view of the broken carbon nanofiber, (d) conical structure on the cross-section of broken CNF.

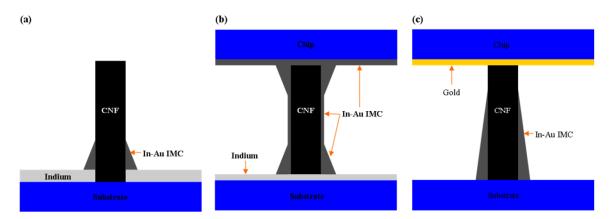

In Table 4.4, the point 4 at the chip side only shows some Au peaks without In. It means that the distribution of IMC layer at the interface is discontinuous or not uniform. The possible reason could be attributed to the insufficient indium volume at the substrate side. During the transfer process, the indium will wet the tip of the VACNF as shown in Figure 4.16 (a). A part of indium will be consumed by reacting with Au at the VACNF surface.

After that, the indium will be further consumed during the bonding process in order to wet whole surface of the VACNF. Finally, the indium can reach to another side (chip side) and form IMC layer, as shown in Figure 4.16 (b). However, if the volume of indium is not enough, after bonding process, the left indium will be insufficient to form IMC layer with Au at the chip side, see Figure 4.16 (c). In this case, discontinuous IMC layer will be formed at the interface. Therefore, increasing the thickness of indium layer could be a possible way to form continuous and uniform IMC layer at the interface and then improve the electrical and mechanical performance of VACNF bumps. However, on the other hand, the cost will be further increased.

Figure 4.16: The status of IMC formation during the transfer and bonding process: (a) the formation of IMC at the tip of VACNF during transfer process, (b) continuous IMC layer can be formed at the chip side if sufficient indium can be supplied during the bonding process, (c) IMC layer cannot be formed at the chip side if without enough indium supply during the bonding process.

#### Application 3: Vertically aligned carbon nanofiber reinforced solder joint structure

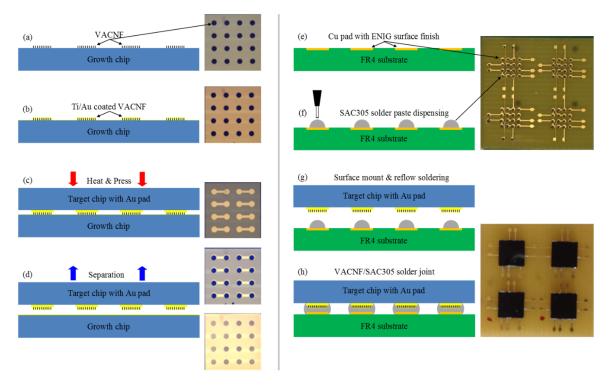

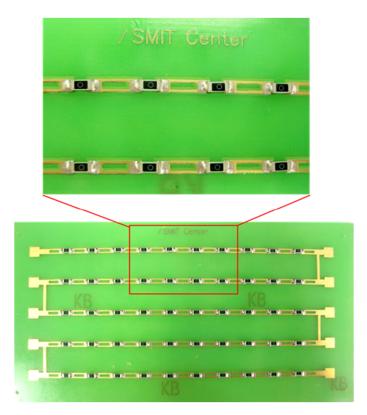

Besides being used as bump materials, VACNFs are also used for enhancing the thermal fatigue resistance of traditional solder joint structure. The structure and fabrication processes of daisy-chain samples were shown in Figure 4.17. Each step in the process is described by a schematic drawing together with an optical microscopic image. At the beginning of the process, the VACNFs were grown on a patterned Si chip by using PECVD method as shown in Figure 4.17 (a). The diameter and pitch of the circles are 400 and 1000  $\mu$ m respectively. Figure 4.17 (b) - (d) describe the VACNF transfer processes based on the Au-Au bonding method. Figure 4.17 (e) shows a FR4 substrate with Cu pads and electroless nickel immersion gold (ENIG) surface finish. After dispensing SAC305 solder paste on the Cu pads, the target chip shown in Figure 4.17 (g). Lastly, by using a reflow solder process, a daisy-chain structured sample with VACNF/SAC305 solder joints was presented and shown in Figure 4.17 (h).

Figure 4.17: Assembly process of VACNF/SAC305 solder joint: (a) growing VACNFs with the PECVD method, (b) Ti/Au coating on the surface of each carbon nanofiber, (c) hot-pressing target chip on growth chip with flip-chip machine, (d) cold-separating target chip from growth chip, (e) FR4 substrate with Cu pad and ENIG surface finish, (f) dispensing SAC305 solder paste on the Cu pad with dispensing machine, (g) mounting target chip on FR4 substrate and running reflow process, (h) thermal cycling test sample with VACNF/SAC305 solder joints.

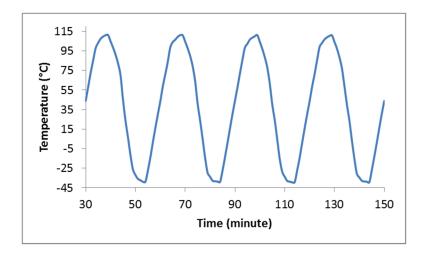

The temperature profile for thermal cycling (TC) test is shown in Figure 4.18. The temperature range of the TC test is -40 to 115 °C. The heating and cooling rate are both 31 °C/min. The duration time per cycle and the soak time at peak and valley of the profile were set to 30 and 10 minutes respectively. The temperature and sample resistance are recorded per minute by an Agilent 34972A Data Acquisition device. The sample will be regarded as failure if 5 consecutive events ( $R > 1000 \Omega$ ) are detected. Pure SAC305 solder joints were also tested with the same sample structure as VACNF/SAC305. The initial average resistance of VACNF/SAC305 and pure SAC305 samples is 58 ± 28  $\Omega$  and 43 ± 28  $\Omega$  respectively.

Figure 4.18: Recorded temperature profile in thermal cycling test

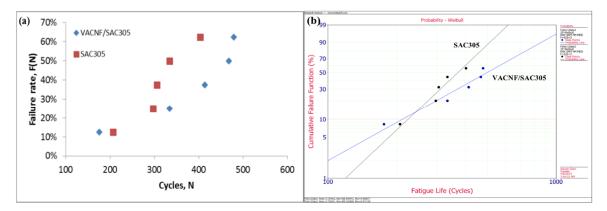

The relationship between the failure rate and the number of cycles is illustrated in Figure 4.19 (a). The failure rates for both samples rapidly increase after 300 cycles, but the failure rate of the VACNF/SAC305 sample is obviously lower than that of the SAC305 sample. The Weibull distributions of cumulative failure function for both samples are shown in Figure 4.19 (b). The shape parameters of the VACNF/SAC305 and SAC305 samples are 2.2 and 3.7 respectively. The characteristic life of the VACNF/SAC305 sample is 589 cycles, which is about 40% longer than that of SAC305 sample (409 cycles).

Figure 4.19: Results of thermal cycling test: (a) relationship between the failure rate and the number of cycles, (b) Weibull distribution of cumulative failure function.

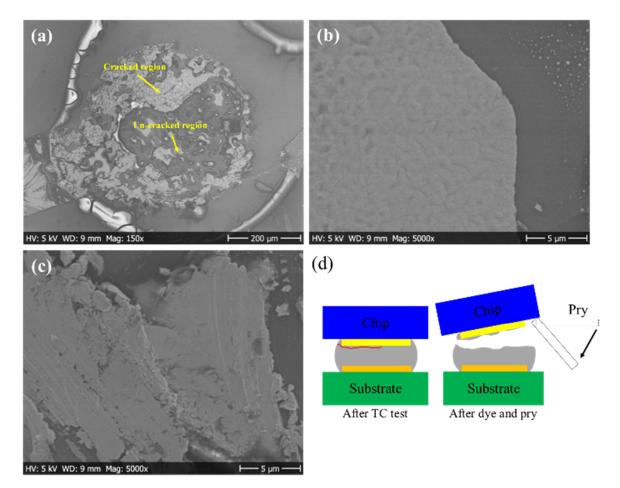

The dye and pry method was used for failure analysis after the TC test. Table 4.5 shows the optical microscopy (OM) images of the fracture surfaces on the chip side. The observation was focused on the solder joints at the four corners of the chip which generally endure the highest stress and strain in the TC test. According to the area calculation of colored region, the crack region of the SAC305 sample is obviously larger than that of the VACNF/SAC305, which means the speed of crack propagation in the VACNF/SAC305 solder joints is lower than SAC305. The aforementioned longer thermal fatigue life of the VACNF/SAC305 sample should be attributed to this lower crack propagation speed.

| SAC305           | ориника и конструкций и констру и конструкции и конструкции и конструкции и констру и конструкции и конструкции и конструпции и констру и конструпции и конструпции и конструпции и конструпции и кон | <u>ой ит</u> | <u>ой рит</u>                                   | Сорона и с | Average |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Crack Area%      | 93.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 72.9         | 66.0                                            | 90.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 80.7    |

| VACNF/<br>SAC305 | Сорона<br>100 р.т.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u>орин</u>  | <u>е по в по </u> | <u>орин</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Average |

| Crack Area%      | 65.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6.6          | 80.8                                            | 75.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57.2    |

Table 4.5: Dye and pry analysis of fracture surfaces

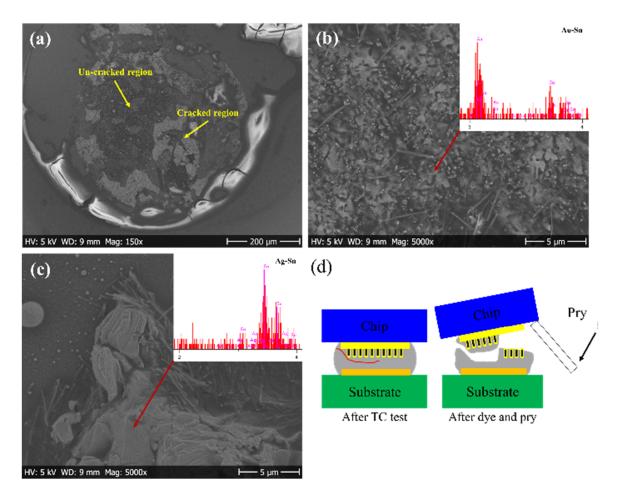

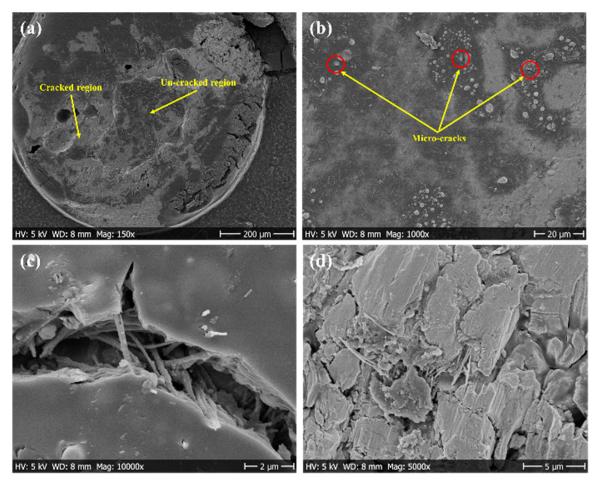

After the OM analysis, the fracture surfaces of the VACNF/SAC305 solder joints were observed by SEM. Figure 4.20 (a) shows a hybrid morphology on the fracture surface of the chip side. Uncracked and cracked regions can be clearly distinguished. Figure 4.20 (b) and (c) are the close-up views of uncracked and cracked regions. In Figure 4.20 (b), some VACNFs are distributed on a rough surface. The subsequent EDX analysis only found Au and Sn elements from this rough surface without Ni or Ag, which implicates that the fracture surface in this region should be very close to the chip side. In Figure 4.20 (c), some VACNFs are distributed around a large bulk which consists of Sn and Ag, proving that the fracture surface in this region is located in the SAC305 solder. Two schematic pictures in Figure 4.20 (d) describe the formation process of this hybrid morphology. The red line in the left schematic picture represents the crack in the solder joint. During the thermal cycling, the crack is initially generated around the corner and propagated along the IMC layer. When the crack meets the VACNFs layer, it appears to bypass the VACNF/SAC305 region, which can reduce the propagation speed and change propagation path of cracks and consequently contributes a long thermal fatigue life to the solder joint. In this case, if the crack finally does not go through whole solder joint after thermal cycling, the cracked and uncracked regions will present a different fracture surface morphology after dye and pry as described in Figure 4.20 (d). The fracture surface of the cracked region was formed in the solder under the VACNFs on the chip side. Therefore, most VACNFs in this region are

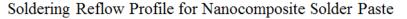

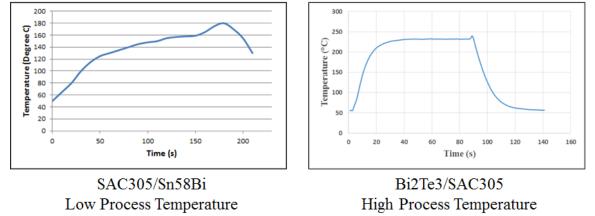

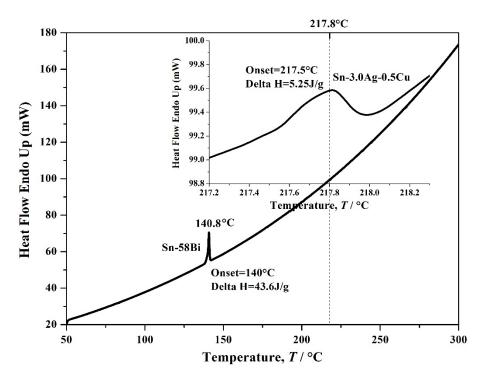

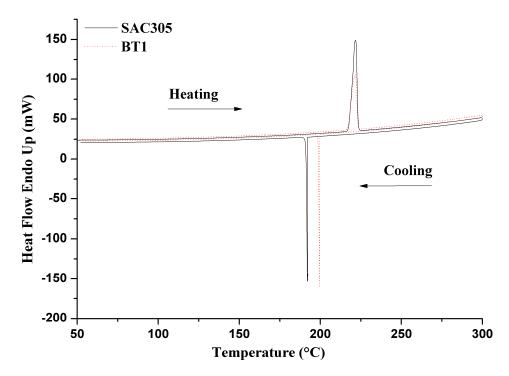

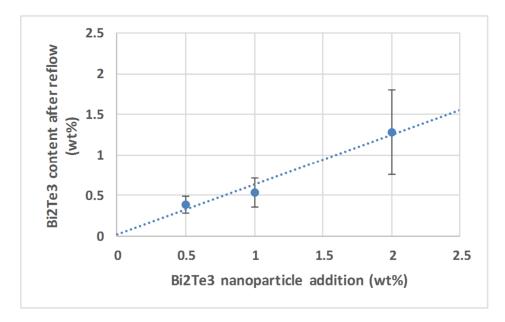

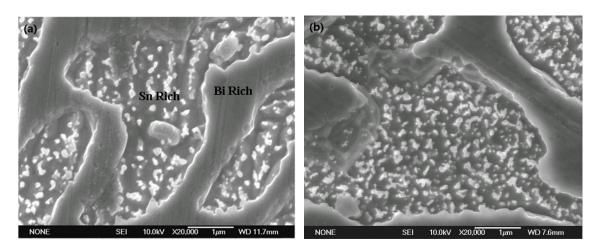

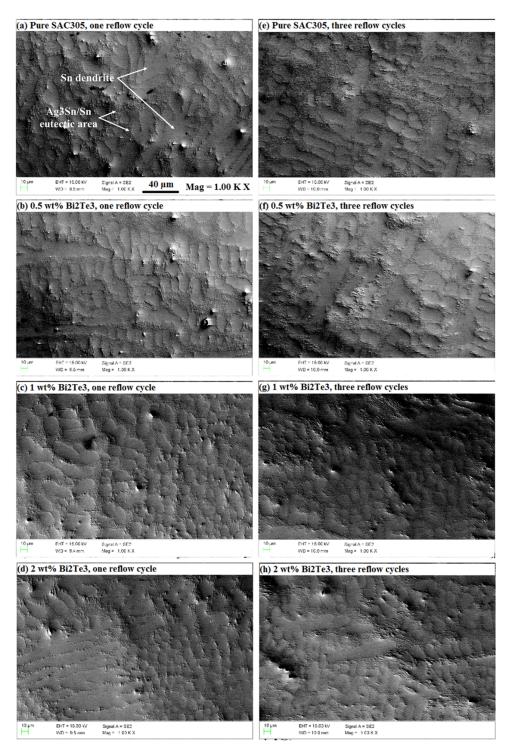

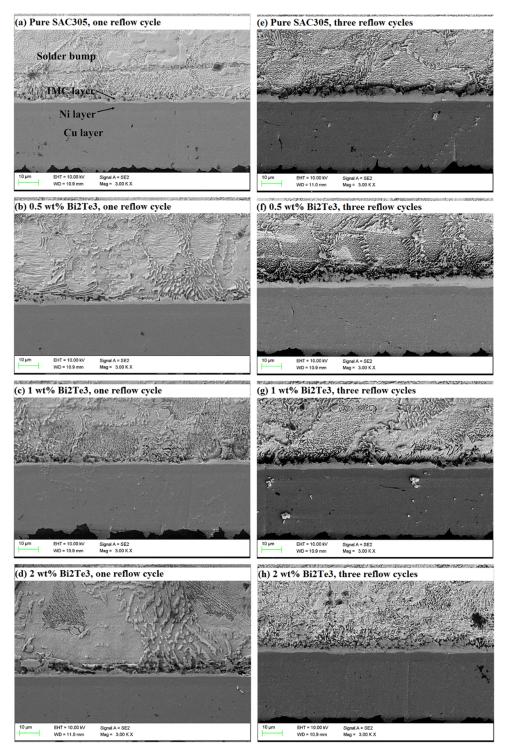

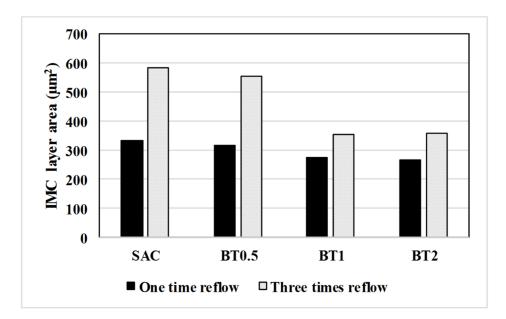

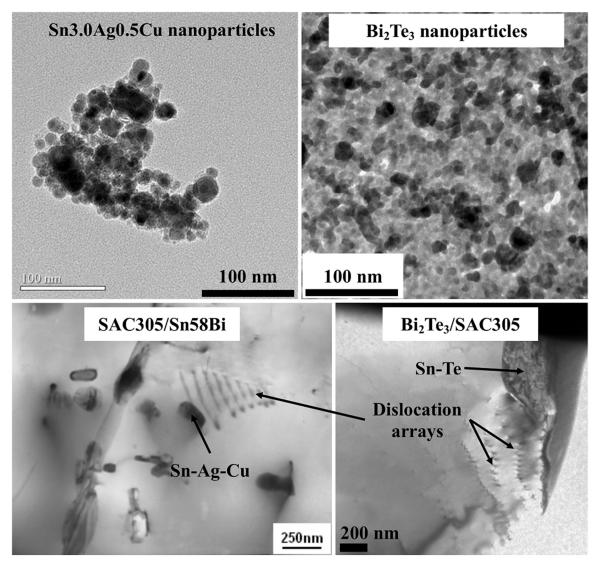

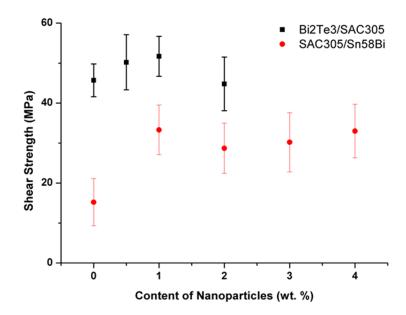

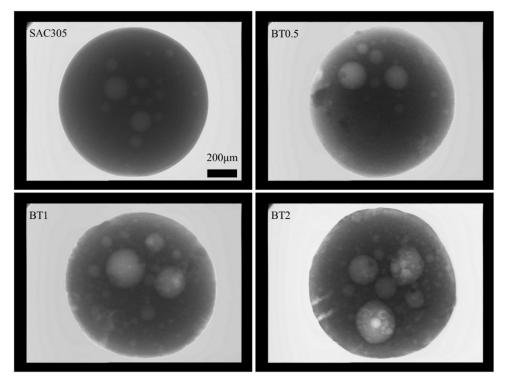

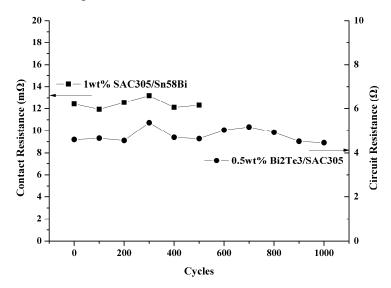

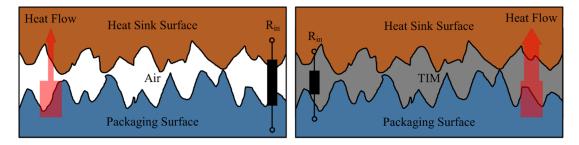

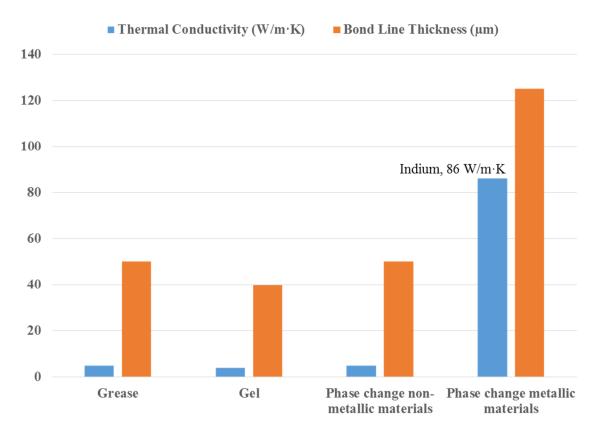

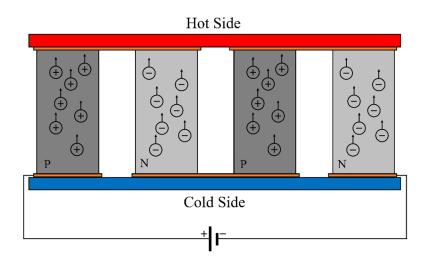

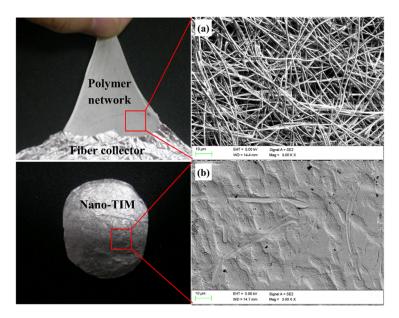

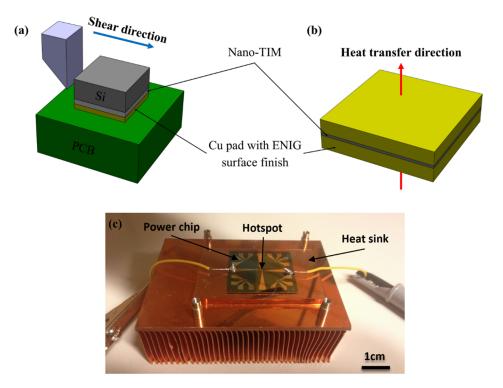

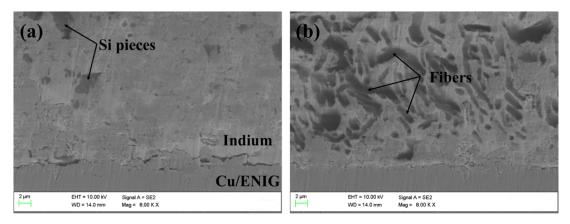

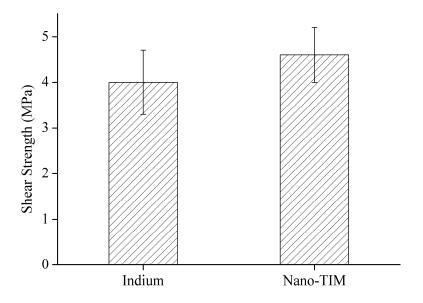

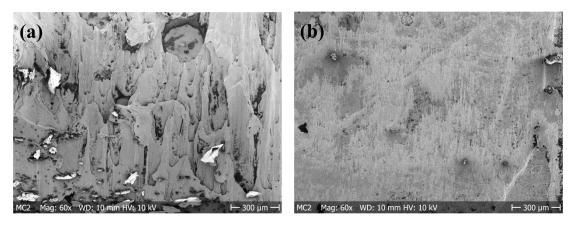

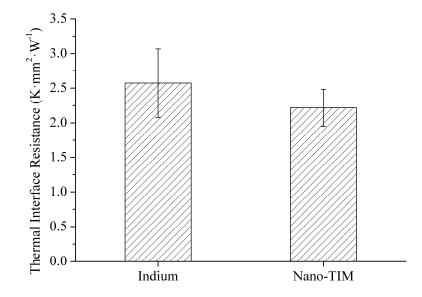

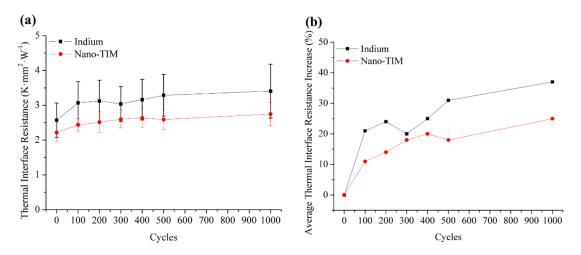

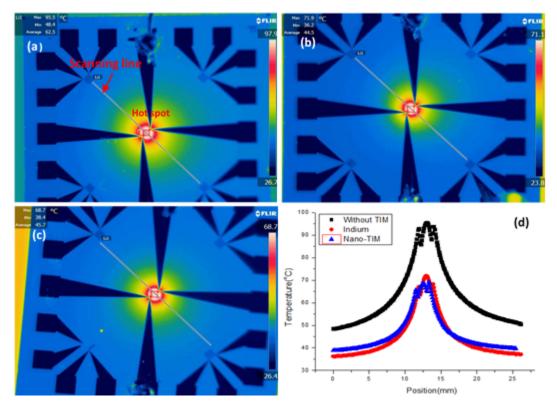

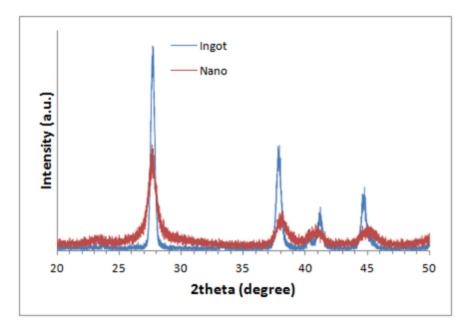

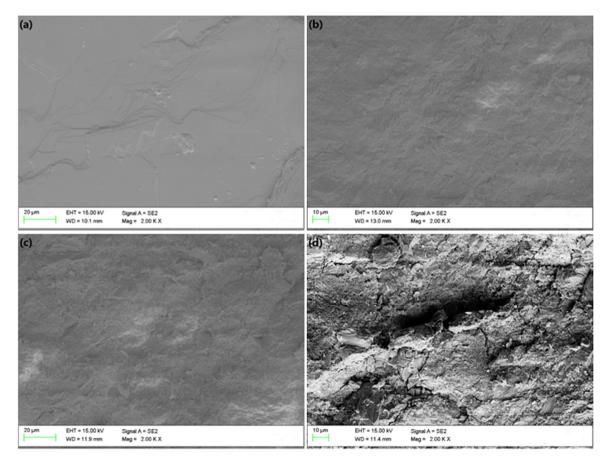

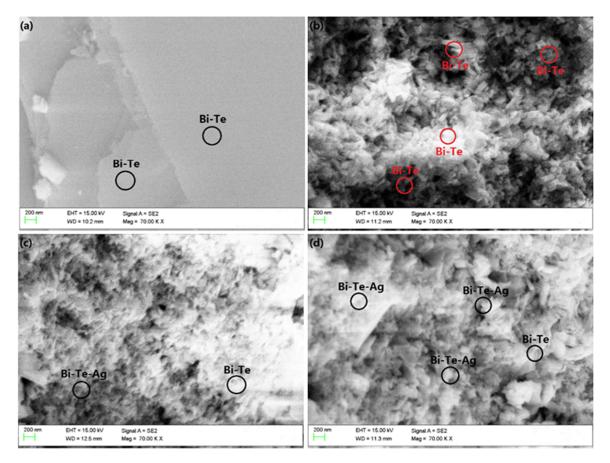

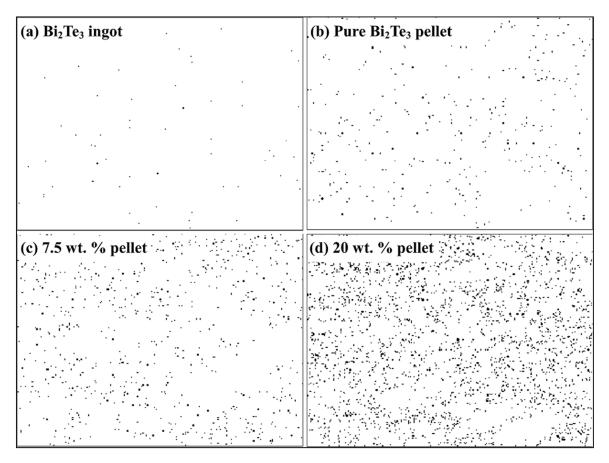

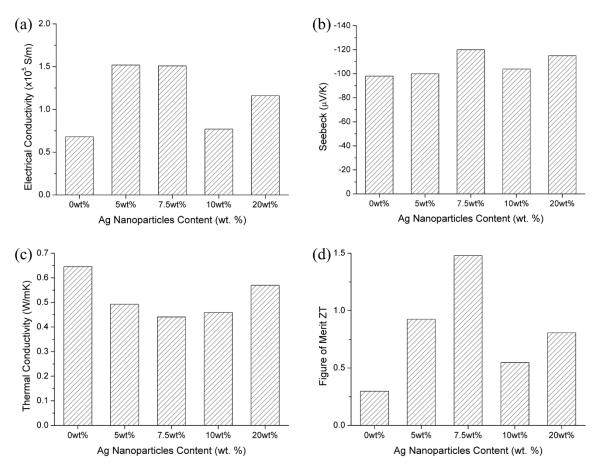

invisible because covered by SAC solder after prying the chip off the substrate. However, some exposed VACNFs can be observed at the edge of the SAC305 solder bulk as shown in Figure 4.20 (c). Around the uncracked region, owing to the stronger bonding between the SAC305 solder and the surface of the VACNFs compared to the Au-Au bonding between the chip surface and the tip of the VACNFs, most VACNFs were removed from the chip surface and only a few VACNFs were left on the chip side as shown in Figure 4.20 (b).