# **CHALMERS**

## **Chalmers Publication Library**

#### Linearization of dual-input Doherty power amplifiers

This document has been downloaded from Chalmers Publication Library (CPL). It is the author's version of a work that was accepted for publication in:

International Workshop on Integrated Nonlinear Microwave and Millimetre-Wave Circuits, INMMiC 2014

#### Citation for the published paper:

Cahuana, J.; Landin, P.; Gustafsson, D. et al. (2014) "Linearization of dual-input Doherty power amplifiers". International Workshop on Integrated Nonlinear Microwave and Millimetre-Wave Circuits, INMMiC 2014 pp. Art. no. 6815085.

http://dx.doi.org/10.1109/INMMIC.2014.6815085

Downloaded from: http://publications.lib.chalmers.se/publication/199954

Notice: Changes introduced as a result of publishing processes such as copy-editing and formatting may not be reflected in this document. For a definitive version of this work, please refer to the published source. Please note that access to the published version might require a subscription.

Chalmers Publication Library (CPL) offers the possibility of retrieving research publications produced at Chalmers University of Technology. It covers all types of publications: articles, dissertations, licentiate theses, masters theses, conference papers, reports etc. Since 2006 it is the official tool for Chalmers official publication statistics. To ensure that Chalmers research results are disseminated as widely as possible, an Open Access Policy has been adopted. The CPL service is administrated and maintained by Chalmers Library.

### Linearization of Dual-Input Doherty Power Amplifiers

Jessica Chani Cahuana, Per Landin, David Gustafsson, Christian Fager, and Thomas Eriksson GigaHertz Centre, Chalmers University of Technology, 412 96 Gothenburg, Sweden

Abstract—This paper studies the linearity of dual-input Doherty power amplifiers. We propose a linearization scheme that uses a combination of an efficiency-optimized static splitter and a vector-switched digital predistorter. The performance of the proposed linearization scheme is evaluated on a dual-input Doherty power amplifier operating at 2.0 GHz with 42 dBm peak output power. Experimental results show that the proposed linearization scheme achieves a normalized mean square error of -43.7 dB and an adjacent channel power ratio of -55.8 dBc with a power added efficiency of 42.4%.

*Index Terms*—digital Doherty, digital predistortion, dual-input Doherty, linearization, power amplifiers.

#### I. INTRODUCTION

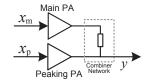

The dual-input Doherty power amplifier (DPA), also referred to as digital Doherty amplifier, is an attractive transmitter architecture for current and future wideband communications systems [1]. A block diagram of a dual-input DPA is shown in Fig. 1. It consists of two parallel amplifiers, a main amplifier and a peaking amplifier, and an impedance inverter network. Unlike single-input DPAs, dual-input DPAs eliminate the analog input splitter, allowing independent control of the input signals to the main and peaking PA. In this way, the input power to both amplifiers can be efficiently distributed so that the power wasted in the peaking branch is minimized when the peaking PA is turned off [1]. In addition to that, the phase relation between branches can be independently controlled at different frequencies thus enabling frequency re-configuration and wider bandwidth implementations [2].

Although improvements in efficiency and bandwidth have been achieved [1], [3], the linearization of dual-input DPAs has not been studied extensively in the literature. In this paper, two aspects of dual-input DPA linearization are studied: power efficiency and bandwidth of the input signals. It is shown that by using a combination of an efficiency-optimized static splitter and a vector-switched digital predistorter, the linearity of dual-input DPAs can be improved while maintaining high efficiency. It is also shown that due to the wide bandwidth of the signals after the static splitter, residual spectral regrowth is found at the output of the amplifier. To circumvent this problem, an improved linearization scheme is proposed. Experimental results show that the proposed scheme can considerably reduce the residual spectral regrowth providing an alternative for the linearization of dual-input DPAs.

This paper is organized as follows. Section II describes the linearization procedure for dual-input DPAs from the derivation of the efficiency-optimized static splitter to the digital predistortion (DPD). Section III presents the measurement setup. Experimental results and discussions are given in Section IV. Finally, the conclusions are provided in Section V.

Fig. 1. Block diagram of a dual-input Doherty power amplifier.

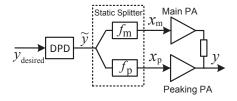

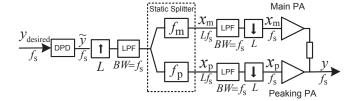

Fig. 2. Linearization scheme for dual-input Doherty power amplifiers.

#### II. LINEARIZATION TECHNIQUE

As Fig. 1 illustrates, for the operation of dual-input DPAs, two RF input signals have to be designed in the digital domain. The signal design should be made to fulfill two requirements: to provide an output signal that complies with the linearity requirements and that provide high power efficiency. Due to the complexity of fulfilling both requirements simultaneously, the signal design is done in two steps. First, a static splitter is derived to provide input signals that drive the PA in a power efficient way and to compensate the amplifier static nonlinearities. Then, the linearity is further enhanced by adding a digital predistorter before the static splitter, as illustrated in Fig. 2. First the derivation of the static splitter is treated.

#### A. Static Splitter

In order to ensure high efficiency operation, the optimal combination of input signals  $x_{\rm m}$  and  $x_{\rm p}$ , as depicted in Fig. 1, has to be identified. This is performed by driving both amplifiers with static continuous wave signals having different combinations of input amplitudes  $|x_{\rm m}|$  and  $|x_{\rm p}|$  and phase differences  $\Delta\phi$  between  $x_{\rm m}$  and  $x_{\rm p}$  and recording the corresponding output signal y and power added efficiency (PAE).

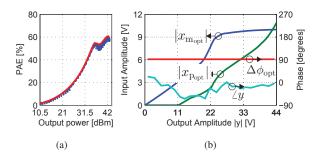

The recorded PAE vs output power is shown in Fig. 3(a), where each blue dot corresponds to a combination of  $|x_{\rm m}|$ ,  $|x_{\rm p}|$  and  $\Delta\phi$ . Different combinations of  $|x_{\rm m}|$ ,  $|x_{\rm p}|$  and  $\Delta\phi$  may provide the same output power but with different PAE. Therefore, a search is performed to identify the input signals  $|x_{\rm m}|$ ,  $|x_{\rm p}|$  and  $\Delta\phi$  that maximize the PAE at each output power level, see Fig. 3(a).

In this work, ADS harmonic balance simulations were performed to test several combinations of  $|x_{\rm m}|$ ,  $|x_{\rm p}|$ , and  $\Delta\phi$  to obtain initial guesses for the input signals. This reduces

measurement time and the risk to destroy the PA due to high input drive levels.

The resulting efficiency-optimized signals  $|x_{\rm mopt}|$ ,  $|x_{\rm Popt}|$ , and  $\Delta\phi_{\rm opt}$  and output phases  $\angle y$  versus output amplitude |y| are shown in Fig. 3(b). Note that, as small phase deviations did not influence the final efficiency, the optimal phase difference was kept constant at 92 degrees.

The relation between |y| and the efficiency-optimized signals,  $|x_{\text{mopt}}|$ ,  $|x_{\text{popt}}|$ ,  $\Delta\phi_{\text{opt}}$  and output phase  $\angle y$ , are used to define AM/AM and AM/PM corrections for the main and peaking PAs,

$$A_{\rm m}(|y|) = |x_{\rm m_{opt}}| \qquad A_{\rm p}(|y|) = |x_{\rm p_{opt}}|$$

(1)

$$\phi_{\rm m}(|y|) = -\angle y$$

$\phi_{\rm p}(|y|) = -\Delta\phi_{\rm opt} - \angle y$  (2)

where  $A_{\rm m}$  and  $\phi_{\rm m}$  are the AM/AM and AM/PM corrections for the main PA; and  $A_{\rm p}$  and  $\phi_{\rm p}$  are the AM/AM and AM/PM corrections for the peaking PA.

The corrections in (1) and (2) are approximated using piecewise polynomials. The approximated corrections  $\widehat{A}_{\rm m}$ ,  $\widehat{A}_{\rm p}$ ,  $\widehat{\phi}_{\rm m}$ , and  $\widehat{\phi}_{\rm p}$  are used to define the static splitter functions  $f_{\rm m}$  and  $f_{\rm p}$ , in Fig. 2, that map any input signal  $\widetilde{y}$  to the control signals to main and peaking PAs  $x_{\rm m}$  and  $x_{\rm p}$ . The static splitter functions are defined by

$$x_{\rm m} = f_{\rm m}(\tilde{y}) = \widehat{A}_{\rm m}(|\tilde{y}|)e^{j(\angle \tilde{y} + \widehat{\phi}_{\rm m}(|\tilde{y}|))} \tag{3}$$

$$x_{\mathbf{p}} = f_{\mathbf{p}}(\tilde{y}) = \widehat{A}_{\mathbf{p}}(|\tilde{y}|)e^{j(\angle \tilde{y} + \widehat{\phi}_{\mathbf{p}}(|\tilde{y}|))}$$

(4)

where  $|\tilde{y}|$  and  $\angle \tilde{y}$  represent the amplitude and phase of the input signal to the static splitter  $\tilde{y}$ . Note that, the static splitter functions  $f_{\rm m}$  and  $f_{\rm p}$  invert the static PA nonlinearity by providing input signals  $x_{\rm m}$  and  $x_{\rm p}$  to achieve a desired output signal. Therefore, these functions act like an efficiency-optimized quasi-static pre-distorter for the dual-input DPA.

#### B. Digital Predistortion

The static splitter cannot compensate dynamic distortions. Therefore, the linearity is enhanced using a digital predistorter, as shown in Fig. 2. Note that the combination of the static splitter and the PA may be considered as single-input-single-output system.

A vector-switched generalized memory polynomial (VS-GMP) is used as model for the DPD [4]. The VS-GMP classifies the input signal into a number of regions based on their amplitudes, and models each region separately. The VS-GMP model is therefore suitable to linearize amplifiers with difficult nonlinearities as is the case for dual-input DPAs [5].

#### III. MEASUREMENT SETUP

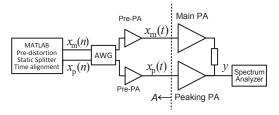

The measurement setup is illustrated in Fig. 4. A dual-channel arbitrary waveform generator (AWG Agilent M8190A) was used to generate the two RF input signals. The PA output signal was captured using a vector signal analyzer (Agilent N9030A).

The delay mismatch between RF branches at the reference plane A, Fig. 4, was determined before the static characterization using an oscilloscope (R&S RTO1044). The delay was

Fig. 3. Static measurements results (a) PAE vs output power (b) Efficiency-optimized input signals derived from static measurements.

Fig. 4. Block diagram of the measurement setup.

calculated using time-domain cross-correlation followed by frequency-domain phase shift [6]. The delay was compensated before the control signals were uploaded to the AWG.

The amplifier used was the dual-input DPA presented in [3]. The amplifier was operated at 2.0 GHz at a peak output power of 42 dBm. A 5 MHz LTE signal with 8.5 dB peak-to-average power ratio was used in the experiments.

#### IV. EXPERIMENTAL RESULTS AND DISCUSSIONS

The input signals to the PA were calculated using the static splitter derived in (3) and (4). The model used for the DPD was a VS-GMP with 16 regions, nonlinear order 5, memory depth 3 and cross-term length 1.

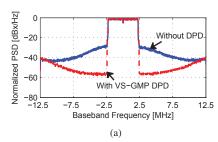

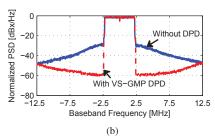

Fig. 5(a) shows the spectrum of the output of the amplifier, before and after applying DPD using a sampling rate of 25 MHz. After DPD, the adjacent channel power ratio (ACPR) was reduced from -30.7 dBc to -53.2 dBc with a PAE of 43%. The linearization results are summarized in Table I.

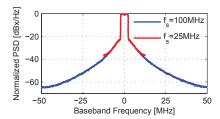

As seen from Fig. 5(a), the output signal spectrum contains residual spectral regrowth towards the edges of the spectrum. This indicates the presence of aliasing distortion in the control signals to the PA. This aliasing distortion is introduced because the sampling rate used in their generation is much smaller than their bandwidth, as shown in Fig. 6 for the control signal  $x_{\rm m}$ .

In order to reduce the effects of aliasing distortion, the scheme in Fig. 7 is proposed. The pre-distorted signal  $\tilde{y}$ , initially upsampled 5 times (5 MHz bandwidth with 25 MHz sampling rate), is upsampled L times before the static splitter. The high sampling rate input signals  $x_{\rm m}$  and  $x_{\rm p}$  are then lowpass filtered to eliminate any frequency components outside the available bandwidth. After that, the input signals are downsampled to the original sampling rate, to drive the dualinput DPA.

The results obtained using this approach are shown in Fig. 5(b) and in Table I. Compared with the results in Fig. 5(a),

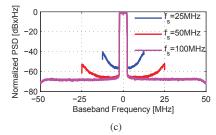

Fig. 5. Linearization results (a)using the linearization scheme in Fig. 2 and 25 MHz sampling rate, (b) using the linearization scheme in Fig. 7 and 25 MHz sampling rate, (c) using the linearization scheme in Fig. 2 and different sampling rates.

Fig. 6. Spectrum of the input signal to the main power amplifier.

the spectral regrowth at 12.5 MHz offset was reduced by more than 9 dB even before applying DPD. The NMSE and ACPR after DPD were further reduced to -43.7 dB and -55.8 dB, respectively. Nevertheless, spectral regrowth is still present at the output signal spectrum.

The remaining spectral regrowth can be either caused by limited linearization capabilities of the model, or bandwidth limitations. In order to test this, measurements using higher sampling rates were used. The results after DPD are shown in Fig. 5(c) and in Table I. Note that the ACPR was reduced by 10 and 11 dB when the sampling rates were increased to 50MHz and 100 MHz, respectively. Moreover, the residual spectral regrowth at the edges of the spectrum was considerably reduced as the sampling rate was increased, reaching the noise floor when 100 MHz was used. Thus, the model has sufficient linearization capabilities, but the limited bandwidth of the signal is causing the residual spectral regrowth. This is a significant finding that requires further investigation.

These results demonstrate that the linearity of dual-input DPAs can be improved using the linearization scheme described in Section II. In order to completely eliminate the spectral regrowth, the linearization requires higher sampling rates. However, high sampling rates are not desired in real applications. This is because they require fast and power hungry digital-to-analog converters (DAC) and analog-to-digital converters (ADC). Consequently, the linearization scheme proposed in Fig. 5(b) may provide an alternative to improve the linearity of dual-input DPAs without increasing the DAC and ADC requirements.

#### V. CONCLUSIONS

The linearity of dual-input DPAs has been studied. It is shown that by using a combination of an efficiency-optimized static splitter and a vector-switched digital predistorter the linearity of the amplifier can be improved by almost 20 dB

Fig. 7. Linearization scheme proposed to eliminate aliasing distortion caused by the large bandwidth of the control signals  $x_{\rm m}$  and  $x_{\rm p}$ .  $f_{\rm s}$  represents the initial sampling rate, L is the upsampling factor, and BW is the available bandwidth.

TABLE I Summary of the linearization results

| DPD                   | $f_s$ | NMSE  | ACPR  | $P_{out}$ | PAE  |

|-----------------------|-------|-------|-------|-----------|------|

| type                  | (MHz) | (dB)  | (dBc) | (dBm)     | (%)  |

| Splitter <sup>1</sup> | 25    | -23.5 | -30.7 | 33.3      | 43.8 |

| VS-GMP <sup>1</sup>   | 25    | -43.1 | -53.7 | 33.4      | 43.7 |

| Splitter <sup>2</sup> | 25    | -23.6 | -31.0 | 33.3      | 42.4 |

| VS-GMP <sup>2</sup>   | 25    | -43.7 | -55.8 | 33.3      | 42.4 |

| VS-GMP <sup>1</sup>   | 50    | -46.6 | -63.6 | 33.3      | 43.9 |

| VS-GMP <sup>1</sup>   | 100   | -48.9 | -64.7 | 33.3      | 43.9 |

<sup>&</sup>lt;sup>1</sup>calculated using linearization scheme in Fig. 2.

while maintaining high efficiency. Due to the wide bandwidth of the signals after the static splitter, residual spectral regrowth is still found at the edges of the output signal spectrum. To address this issue, a linearization scheme is proposed to reduce the residual spectral regrowth. The results show that the proposed approach can reduce the residual spectral regrowth by more than 9 dB without increasing DAC or ADC demands.

#### REFERENCES

- R. Darraji and F. M. Ghannouchi, "Digital Doherty amplifier with enhanced efficiency and extended range," *IEEE Trans. Microw. Theory Tech.*, vol. 59, no. 11, pp. 2898–2909, Nov. 2011.

- [2] J. H. Qureshi, N. Li, W. C. E. Neo, F. van Rijs, I. Blednov, and L. C. N. de Vreede, "A wide-band 20W LDMOS Doherty power amplifier," in *IEEE MTT-S Int. Microwave Symp. Dig.*, May 2010, pp. 1504–07.

- [3] D. Gustafsson, C. M. Andersson, and C. Fager, "A modified Doherty power amplifier with extended bandwidth and reconfigurable efficiency," *IEEE Trans. Microw. Theory Tech.*, vol. 61, no. 1, pp. 533–542, Jan. 2013.

- [4] S. Afsardoost, T. Eriksson, and C. Fager, "Digital predistortion using a vector-switched model," *IEEE Trans. Microw. Theory Tech.*, vol. 60, no. 4, pp. 1166–74, Apr. 2012.

- [5] H. Cao, J. Qureshi, T. Eriksson, C. Fager, and L. de Vreede, "Digital predistortion for dual-input doherty amplifiers," in *IEEE Topical Conf.* on Power Amplifiers for Wireless and Radio Applications, Jan. 2012.

- [6] M. Isaksson, D. Wisell, and D. Ronnow, "A comparative analysis of behavioral models for RF power amplifiers," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 1, pp. 348–359, Jan. 2006.

<sup>&</sup>lt;sup>2</sup>calculated using linearization scheme in Fig. 7.