THESIS FOR THE DEGREE OF LICENTIATE OF ENGINEERING

# A Taxonomy and Design Methodology for Hybrid Memory Systems

DMITRY KNYAGININ

Division of Computer Engineering Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Gothenburg, Sweden 2014

### A Taxonomy and Design Methodology for Hybrid Memory Systems

Dmitry Knyaginin

Copyright © 2014 Dmitry Knyaginin

Technical report 117L ISSN 1652-876X Department of Computer Science and Engineering Computer Architecture Research Group

Division of Computer Engineering Chalmers University of Technology SE-412 96 GOTHENBURG, Sweden Phone: +46 (0)31-772 10 00

Author e-mail: dmitry.knyaginin@chalmers.se

Printed by Chalmers Reproservice Gothenburg, Sweden 2014

### A Taxonomy and Design Methodology for Hybrid Memory Systems

Dmitry Knyaginin

Division of Computer Engineering, Chalmers University of Technology

### ABSTRACT

The number of concurrently executing processes and their memory demand in multicore systems continue to grow. Larger and still fast main memory is needed for meeting the demand and avoiding an increase in backing store accesses that are much slower and less energy efficient than main memory accesses. Luckily, Non-Volatile Memory (NVM) technologies can bridge the cost, density, performance, and energy efficiency gaps between backing store and DRAM, the conventional main memory technology. Thus, NVM can be combined with DRAM into *hybrid* main memory striving to enjoy both the larger capacity enabled by NVM and the speed and energy efficiency of DRAM.

NVM adds a new dimension to the system design space inspiring researchers to investigate sophisticated hybrid memories. This has resulted in a large body of work that, unfortunately, lacks systematization. The thesis at hand addresses this problem by proposing a taxonomy and a notation for classifying hybrid main memory organizations.

The design space of hybrid systems is large, and the best partitioning of resources between DRAM and NVM is nontrivial. The high implementation and computation efforts of detailed modeling impede extensive design space exploration required for finding the most promising design points. This thesis aids such extensive exploration by proposing a workload methodology and first-order models for system-level execution time and energy. Next, the thesis contributes with *Rock*, an insightful performance model showing how memory system throughput can be boosted by installing more DRAM and NVM thus motivating Design-time Resource Partitioning (DRP). The lack of an approach suitable for extensive partitioning is addressed by proposing *Crystal*, a DRP method powered by the system-level models and framing partitioning as an optimization problem, such that the first-order nature of the models does not restrict its applicability, as shown by validation. Crystal is practical and facilitates early and rapid DRP finding promising design points for further detailed evaluation. For instance, Crystal shows how for specific workloads higher performance and energy efficiency can be achieved by employing NVM with the speed and energy consumption of NAND Flash instead of a much faster and more energy efficient NVM technology like phase-change memory.

**Keywords:** DRAM, Non-Volatile Memory, Taxonomy, Methodology, Design Space Exploration, System-Level Models, Performance, Energy Efficiency.

ii

## Preface

The thesis at hand is for the degree of Licentiate of Engineering, a Swedish degree between MSc and PhD. Parts of the contributions presented in this thesis have previously been accepted to workshops:

- Dmitry Knyaginin, Sally A. McKee, and Georgi N. Gaydadjiev, "A hybrid main memory systems taxonomy," in *Memory Architecture and Organization Workshop, co-located with Embedded Systems Week*, Tampere, Finland, Oct. 2012, pp. 1–6.

- Dmitry Knyaginin, Georgi N. Gaydadjiev, and Per Stenström, "Crystal: A design-time resource partitioning method for hybrid main memory," in Workshop on Reproducible Research Methodologies, co-located with Int. Symp. on High Performance Computer Architecture, Orlando, FL, USA, Feb. 2014, pp. 1–6.

The following manuscript contains parts of the contributions presented in this thesis and has been submitted to an international conference:

Dmitry Knyaginin, Georgi N. Gaydadjiev, and Per Stenström, "Crystal: A design-time resource partitioning method for hybrid main memory," Under review since Mar. 2014.

PREFACE

## Acknowledgments

I cannot thank enough my advisor, Per Stenström, for his inspiration, mentorship, and guidance. Without Per I would not be able to navigate in the deep waters of research.

Many thanks to my co-advisor and examiner, Georgi N. Gaydadjiev, for his input and feedback, and for the opportunities to practice research discussions in Russian.

I am grateful to Sally A. McKee for her input at the early stages of my PhD program, for the successful collaboration on the taxonomy paper, and especially for her help with editing the text of the first draft of Crystal.

A big thank you to Lars Svensson for his support, advice, and weekly meetings during 2011-12. The work done during that period laid the ground for this thesis.

I would like to extend my gratitude to everybody with whom I have been fortunate to discuss my work. In particular, I would like to thank Anurag Negi and Magnus Själander for countless discussions inside and outside the premises of Chalmers, and Vinay Jethava for his help with various mathematical questions.

Many thanks to Eva Axelsson, Gerardo Schneider, Jan Jonsson, Johan Karlsson, Koen Lindström Claessen, Malin Nilsson, Marianne Pleen-Schreiber, Peter Helander, Rune Ljungbjörn, and Tiina Rankanen for providing administrative and technical support. I would also like to thank Bhavishya Goel and Jacob Lidman for maintaining the *ttitania* cluster. A special thank you to Anna-Lena Karlsson for her help during my first days at Chalmers and for finding a beautiful apartment for me.

I express my deep appreciation to everybody at the Department of Computer Science and Engineering and especially at the Division of Computer Engineering for contributing to the warm and professional environment. In particular, I thank Alen Bardizbanyan and Angelos Arelakis for the productive atmosphere inside our office. Finally, I would like to thank all my friends. Special thanks to Alex Geppert, Dima Mishenin, Jeff Jung, John Moyes, Katarina Steffenburg, Martin Lever, Morris Stuttard, Oleg Bogdanov, and Vilhelm Verendel for their support, and to my family—Victoria, Vladimir, and Oleg—for their love.

The thesis at hand is based upon work supported by the Swedish Research Council (Vetenskapsrådet) under the Chalmers Adaptable Multicore Processing Project (CHAMPP).

> Dmitry Knyaginin Gothenburg, May 2014

# Contents

| Ał | ostrac | rt -                                 | i   |

|----|--------|--------------------------------------|-----|

| Pr | eface  |                                      | iii |

| Ac | know   | vledgments                           | v   |

| Ac | rony   | ms                                   | xv  |

| 1  | Intr   | oduction                             | 1   |

|    | 1.1    | Problem Statements                   | 3   |

|    | 1.2    | Contributions                        | 4   |

|    | 1.3    | Thesis Organization                  | 5   |

| 2  | Wor    | kload Methodology                    | 7   |

|    | 2.1    | Program Profiling                    | 8   |

|    | 2.2    | Workload Representation              | 10  |

|    | 2.3    | Workload Classification              | 14  |

|    | 2.4    | Profiling Setup and Program Profiles | 14  |

|    | 2.5    | Summary                              | 17  |

| 3  | Mer    | nory Technologies                    | 19  |

|    | 3.1    | Basic Memory Cell Properties         | 20  |

|    |        | 3.1.1 DRAM                           | 20  |

|    |        | 3.1.2 Flash                          | 21  |

|    |        | 3.1.3 PCM                            | 21  |

|    |        | 3.1.4 Magnetic Memory                | 22  |

|    |        | 3.1.5 Other Technologies             | 22  |

### CONTENTS

|   | 3.2 | Device  | Organization and Operation             | 23 |

|---|-----|---------|----------------------------------------|----|

|   |     | 3.2.1   | Basic Solid-State Device               | 23 |

|   |     | 3.2.2   | DRAM Device                            | 24 |

|   |     | 3.2.3   | PCM Device                             | 25 |

|   |     | 3.2.4   | NAND Flash Device                      | 26 |

|   |     | 3.2.5   | NOR Flash Device                       | 27 |

|   |     | 3.2.6   | SSD                                    | 28 |

|   |     | 3.2.7   | HDD                                    | 28 |

|   | 3.3 | Device  | -Level Models                          | 28 |

|   |     | 3.3.1   | DRAM Models                            | 29 |

|   |     | 3.3.2   | PCM Models                             | 35 |

|   |     | 3.3.3   | NAND Flash Models                      | 36 |

|   |     | 3.3.4   | SSD and HDD Models                     | 39 |

|   |     | 3.3.5   | Example Estimates                      | 40 |

|   |     | 3.3.6   | Discussion                             | 42 |

|   | 3.4 | Summa   | a <b>r</b> y                           | 42 |

| 4 | Hyb | rid Men | nory Systems Taxonomy                  | 43 |

|   | 4.1 | Notatio | on                                     | 44 |

|   | 4.2 | Classif | ication                                | 45 |

|   |     | 4.2.1   | Flat Systems                           | 45 |

|   |     | 4.2.2   | Hierarchical Systems                   | 48 |

|   | 4.3 | Summa   | ary                                    | 50 |

| 5 | Hvh | rid Mer | nory Systems Design Methodology        | 53 |

| 2 | 5.1 |         | n-Level Models                         | 55 |

|   | 5.2 | 2       |                                        | 62 |

|   | 0.2 | 5.2.1   | Experimental Setup                     | 62 |

|   |     | 5.2.2   | Results                                | 64 |

|   |     | 5.2.3   | Discussion                             | 74 |

|   |     | 5.2.4   | Concluding Remarks                     | 74 |

|   | 5.3 |         | ······································ | 75 |

|   |     | 5.3.1   | Complexity of Equal-Area Partitioning  | 75 |

|   |     | 5.3.2   | Experimental Setup                     | 77 |

|   |     | 5.3.3   | Results                                | 81 |

|   |     | 5.3.4   | Validation                             | 86 |

|   |     |         |                                        |    |

viii

### CONTENTS

|    |       | 5.3.5   | Related Work       |   |       | 90  |

|----|-------|---------|--------------------|---|-------|-----|

|    |       | 5.3.6   | Concluding Remarks |   |       | 93  |

|    | 5.4   | Summa   | ary                | • | <br>• | 94  |

| 6  | Con   | clusion |                    |   |       | 95  |

|    | 6.1   | Contril | butions            |   |       | 96  |

|    | 6.2   | Future  | 2 Work             | • | <br>• | 100 |

| Bi | bliog | raphy   |                    |   |       | 101 |

### CONTENTS

# List of Figures

| 1.1  | Normalized bit cost vs. bit density and access dynamic energy vs. access                |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | latency of memory technologies                                                          | 2  |

| 2.1  | Example miss curve                                                                      | 9  |

| 2.2  | Algorithm of high- and low-utility DRA                                                  | 12 |

| 2.3  | Miss curves for illustrating high-utility, low-utility, and utility-agnostic            |    |

|      | DRA policies                                                                            | 13 |

| 2.4  | Miss curves of CG, lbm, mcf, sjeng, and soplex                                          | 16 |

| 4.1  | Baseline system                                                                         | 44 |

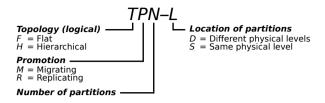

| 4.2  | <i>TPN</i> – <i>L</i> notation                                                          | 45 |

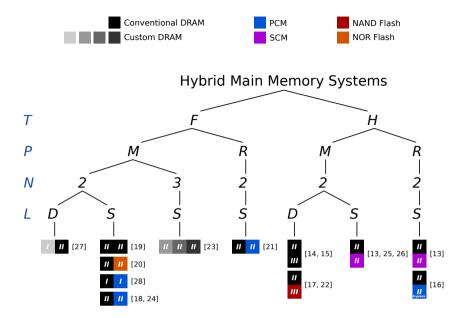

| 4.3  | <i>TPN–L</i> classification of contemporary hybrid memory systems                       | 51 |

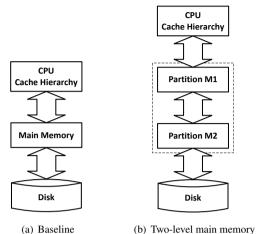

| 5.1  | Memory hierarchy organizations                                                          | 56 |

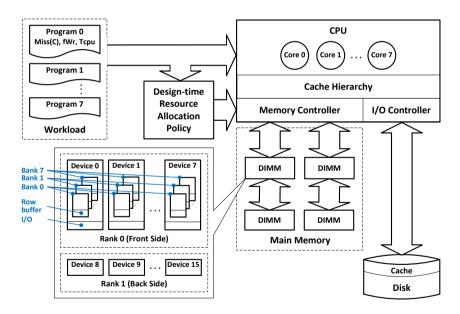

| 5.2  | Detailed diagram of system modeled                                                      | 56 |

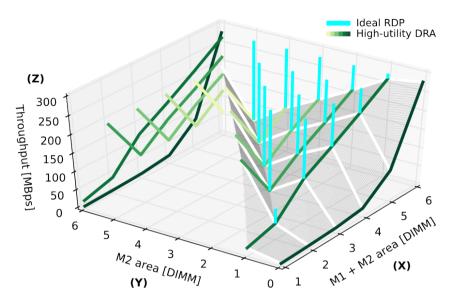

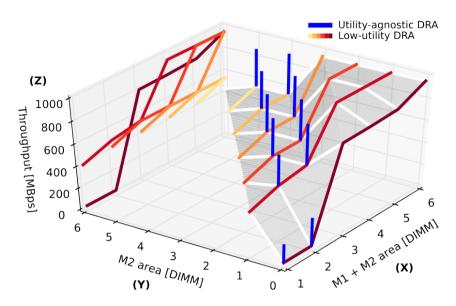

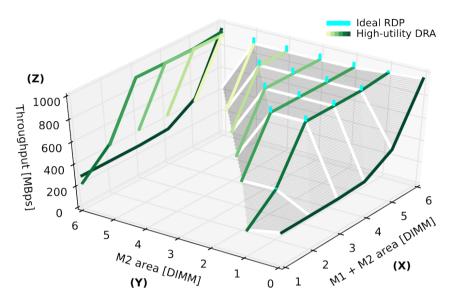

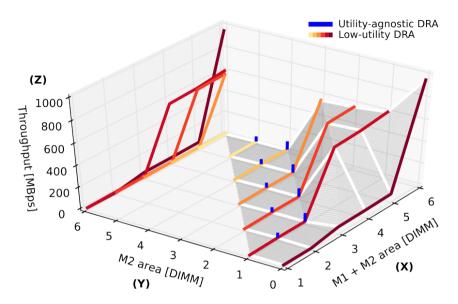

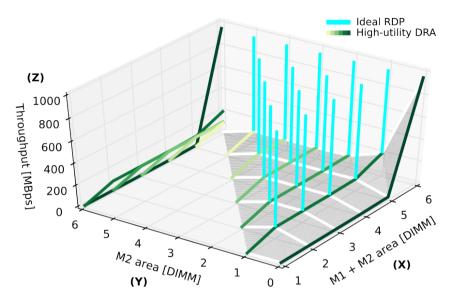

| 5.3  | Rock for WA and systems with PCM and SSD                                                | 65 |

| 5.4  | Rock for WB and systems with PCM and SSD (part I) $\hdots$                              | 66 |

| 5.5  | Rock for WB and systems with PCM and SSD (part II) $\hfill \ldots \ldots$               | 69 |

| 5.6  | Rock for WB and systems with NAND Flash and HDD (part I) $\ . \ . \ .$                  | 72 |

| 5.7  | Rock for WB and systems with NAND Flash and HDD (part II) $\ . \ . \ .$                 | 73 |

| 5.8  | Equal-area partitioning and multiple local minima of execution time                     | 76 |

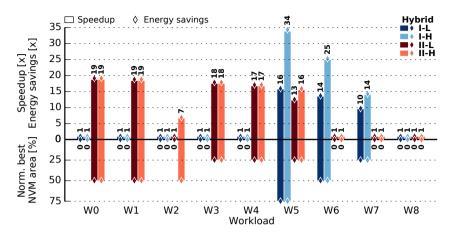

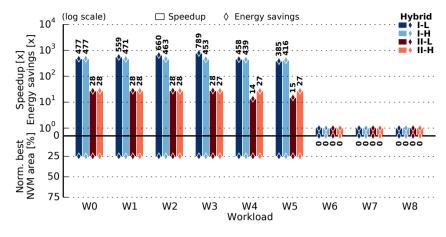

| 5.9  | Crystal for hybrids with HDD and <code>mcf/soplex</code> set                            | 82 |

| 5.10 | Crystal for hybrids with HDD and <code>lbm/sjeng set</code>                             | 83 |

| 5.11 | Crystal for hybrids III-L and III-H and <code>lbm/sjeng</code> set $\ldots\ldots\ldots$ | 84 |

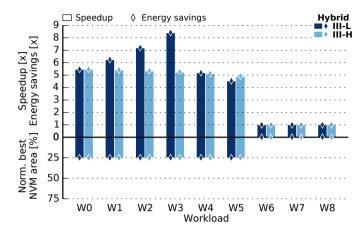

| 5.12 | Crystal for hybrids with HDD and CG/s jeng set                                          | 85 |

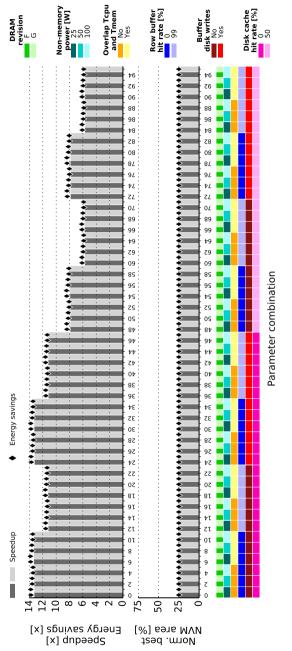

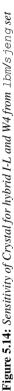

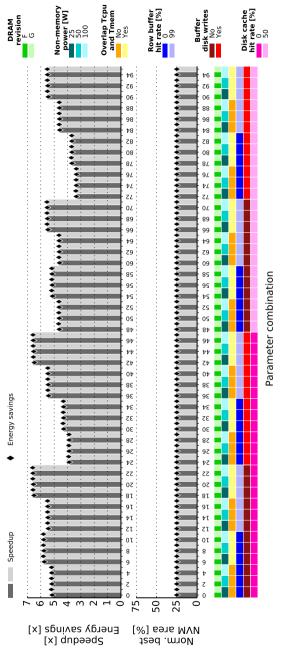

| 5.13 | Sensitivity of Crystal for hybrid II-L and W4 from <code>lbm/sjeng</code> set           | 87 |

|      |                                                                                         |    |

### LIST OF FIGURES

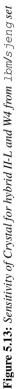

| 5.14 | Sensitivity of Crystal | for hybrid I-L and W4 from | lbm/sjeng set 8 | ;9 |

|------|------------------------|----------------------------|-----------------|----|

|------|------------------------|----------------------------|-----------------|----|

5.15 Sensitivity of Crystal for hybrid III-L and W4 from <code>lbm/sjeng set</code> . . 91

# List of Tables

| 2.1  | Selected characteristics of CG, lbm, mcf, sjeng, and soplex                   | 17 |

|------|-------------------------------------------------------------------------------|----|

| 3.1  | Characteristics of example DRAM, PCM, NAND and NOR Flash devices              | 25 |

| 3.2  | Subset of DDR3 SDRAM commands                                                 | 29 |

| 3.3  | Selected DRAM characteristics                                                 | 30 |

| 3.4  | Currents of DRAM revisions F and G                                            | 30 |

| 3.5  | PCM array latencies and energies normalized to those of DRAM                  | 35 |

| 3.6  | Selected NAND Flash characteristics                                           | 37 |

| 3.7  | Selected characteristics of SSD and HDD                                       | 39 |

| 3.8  | 64B access latencies of DRAM, PCM, and NAND Flash                             | 40 |

| 3.9  | $4 \mathrm{KB}$ access latencies of DRAM, PCM, NAND Flash, SSD, and HDD $\ .$ | 40 |

| 3.10 | 64B access dynamic energies of DRAM, PCM, and NAND Flash                      | 41 |

| 3.11 | 4KB access dynamic energies of DRAM, PCM, NAND Flash, SSD, and                |    |

|      | HDD                                                                           | 41 |

| 5.1  | Assumed model parameters                                                      | 57 |

| 5.2  | Variables in Equations (5.1) to (5.12)                                        | 58 |

| 5.3  | System configuration for Rock                                                 | 63 |

| 5.4  | Model parameters for Rock                                                     | 63 |

| 5.5  | Selected memory characteristics for Rock                                      | 63 |

| 5.6  | Low-utility DRA for WB when $M2$ area is zero $\ldots \ldots \ldots \ldots$   | 67 |

| 5.7  | Low-utility DRA for WB when total area is six DIMMs                           | 68 |

| 5.8  | High-utility DRA for WB when $M2$ area is zero $\ldots \ldots \ldots \ldots$  | 70 |

| 5.9  | High-utility DRA for WB when total area is three DIMMs                        | 71 |

| 5.10 | System configuration for Crystal                                              | 78 |

### LIST OF TABLES

| 5.11 | Default model parameters for Crystal                 | 78 |

|------|------------------------------------------------------|----|

| 5.12 | Characteristics of DRAM revisions F and G            | 79 |

| 5.13 | Selected memory characteristics for Crystal          | 80 |

| 5.14 | Hybrids and their baselines                          | 80 |

| 5.15 | Model parameters for sensitivity analysis of Crystal | 86 |

# Acronyms

| 1T     | One Transistor                                  |

|--------|-------------------------------------------------|

| 1T1C   | One Transistor and One Capacitor                |

| 1T1MTJ | One Transistor and One Magnetic Tunnel Junction |

| 1T1R   | One Transistor and One Resistor                 |

| CPU    | Central Processing Unit                         |

| DDR    | Double Data Rate                                |

| DIMM   | Dual In-line Memory Module                      |

| DLL    | Delay-Locked Loop                               |

| DRA    | Design-time Resource Allocation                 |

| DRAM   | Dynamic Random Access Memory                    |

| DRP    | Design-time Resource Partitioning               |

| FeRAM  | Ferroelectic Random Access Memory               |

| HDD    | Hard Disk Drive                                 |

| I/O    | Input/Output                                    |

| L1C    | Level-One Cache                                 |

| LLC    | Last Level Cache                                |

| LRU    | Least Recently Used                             |

| MLC    | Multi-Level Cell                                |

| MRAM   | Magnetoresistive Random Access Memory           |

| MTJ    | Magnetic Tunnel Junction                        |

| NVM      | Non-Volatile Memory                                        |

|----------|------------------------------------------------------------|

| ONFI     | Open NAND Flash Interface                                  |

| OS       | Operating System                                           |

| РСМ      | Phase-Change Memory                                        |

| RDP      | Run-time Data Placement                                    |

| RRAM     | Resistive Random Access Memory                             |

| SATA     | Serial Advanced Technology Attachment                      |

| SCM      | Storage-Class Memory                                       |

| SDRAM    | Synchronous Dynamic Random Access Memory                   |

| SLC      | Single-Level Cell                                          |

| SRAM     | Static Random Access Memory                                |

| SSD      | Solid-State Disk                                           |

| STT-MRAM | Spin Transfer Torque Magnetoresistive Random Access Memory |

| VLSI     | Very Large Scale Integration                               |

xvi

# Introduction

The contemporary trend of increasing core counts in computing systems [1] implies growing numbers of concurrently executing programs in the system workload. The problem sizes of contemporary programs continue to grow, too, especially in the domains of scientific computing, databases, and consolidated cloud environments. These two trends result in a continuously increasing demand for larger and still fast memory of computing systems.

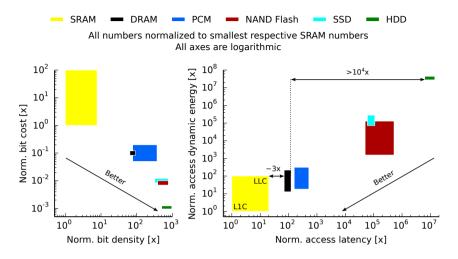

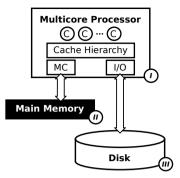

A typical high-performance memory system is organized as a hierarchy. Central Processing Unit (CPU) memory, such as the register file and a cache hierarchy from Level-One Cache (L1C) down to Last Level Cache (LLC), is followed by larger but slower main memory that is further followed by even more large and slow backing store. Caches are conventionally implemented as Static Random Access Memory (SRAM), main memory is built from Dynamic Random Access Memory (DRAM), and backing store is composed of magnetic Hard Disk Drives (HDDs). Each of the technologies has pros and cons, offering different bit densities (the number of bits per mm<sup>2</sup>), bit costs,

**Figure 1.1:** Normalized bit cost vs. bit density and access dynamic energy vs. access latency of memory technologies

access latencies, and dynamic energies. The purpose of the hierarchy is to enjoy the pros while hiding the cons that negatively impact the performance and energy efficiency of the entire system. However, the gaps between the adjoining levels of the conventional memory hierarchy are rather large and uneven. For instance, the access latency gap between SRAM LLC and DRAM main memory is about three times, while between DRAM and HDD this gap is at least four orders of magnitude. The larger the gaps, the more challenging it is to hide the cons of the hierarchy levels. Thus, bridging or reducing the gaps between DRAM and HDD remains a major design challenge.

Fortunately, technological progress in the field of solid-state memory [1, 2] has contributed a number of promising Non-Volatile Memory (NVM) technologies that fit in the gaps between DRAM and HDD. One such technology, Phase-Change Memory (PCM) [3, 4], is gaining maturity and has the potential to offer a higher bit density than DRAM but at a penalty of slower and less energy efficient accesses. Another technology, NAND Flash, is mature and offers a higher bit density and a lower bit cost than DRAM, but accessing it is even slower and less energy efficient than accessing PCM. NVM has enabled high-performance disks, such as Solid-State Disk (SSD) built from NAND Flash.

Figure 1.1 aggregates the bit density, cost, access latency, and dynamic energy numbers of representative memory technologies [1, 5–12], where access denotes both

random reads and writes of typical sizes. All of the numbers are normalized to the smallest respective numbers of SRAM and are expressed as ratios ( $\times$ ). They are of a sufficient accuracy to illustrate the gaps between the technologies. The numbers are represented by ranges, because they depend on many factors, including the implementation process and the type and size of access. Such ranges of values for each technology and characteristic are shown by the rectangles. For instance, consider the right part of the figure (normalized access dynamic energy vs. access latency). The bottom left corner of the SRAM rectangle shows the access latency and dynamic energy of L1C, and the top right corner shows those of LLC. The left edge of the DRAM rectangle depicts the latency of a read access, the right edge the latency of a write access, the bottom edge the dynamic energy of a read access served by a single DRAM device, and the top edge the dynamic energy of a write access served by a rank of eight less energy-efficient DRAM devices. For the purposes of this chapter no further details need to be discussed, as the figure clearly shows that the gaps exist even if broad ranges of technology characteristics are considered.

NVM technologies can help bridge the gaps between the levels of the conventional memory hierarchy from the main memory side by enabling *hybrid main memory*, i.e., main memory divided into two or more partitions where each partition is optimized for specific purposes (e.g., performance, energy efficiency, capacity, or cost). In addition, NVM technologies can help reduce the gaps from the backing store side by enabling faster and more energy efficient disks, such as SSD. This thesis investigates hybrid main memory. The rest of this chapter details the problems addressed by the thesis, lists my contributions, and explains the organization of the thesis.

### **1.1 Problem Statements**

Hybrid main memory systems have attracted vivid interest among researchers that have proposed and investigated a plurality of hybrid system organizations [13–30]. Unfortunately, this large body of work lacks systematization. This complicates positioning new hybrid memory proposals within the existing body of work. Systematization of hybrid main memory system organizations is one of the problems addressed by this thesis.

An obvious design challenge for hybrid main memory is that memory resources are restricted from the physical, technological, and cost perspectives. This boils the design process down to optimization of resources under design goals that can differ. For instance, if the goal is to reduce the cost of main memory, DRAM can be combined with a less expensive NVM technology to create hybrid memory of a lower cost but the same capacity as DRAM-only main memory. If the goal is to increase capacity, DRAM can be combined with a bit-denser NVM technology to store more bits in the same physical area as DRAM-only main memory. Finding the best amounts of DRAM and NVM is a nontrivial design-time resource partitioning problem. The best solution depends on many factors, including the workload, properties of memory technologies, and characteristics of subsystems other than main memory and disk (e.g., the CPU). Characteristics of hybrid systems implementing different partitioning options can vary widely. This makes design-time partitioning a fundamental problem for hybrid main memory systems with a multi-dimensional design space.

Partitioning of main memory resources between different technologies has been studied using simulators [14–16] and prototyping [13]. Simulation typically involves a significant implementation overhead and consumes large computational resources, impeding extensive design space exploration. Prototyping with, e.g., a virtual machine monitor [13], requires a substantial implementation effort and restricts exploration to a given host configuration (e.g., the total capacity of main memory). The lack of a design-time partitioning method suitable for rapid and extensive hybrid memory design space exploration is another problem tackled by this thesis.

### **1.2** Contributions

The thesis addresses the problems stated above by making the following contributions:

- First, a taxonomy of hybrid main memory organizations is proposed [31]. The taxonomy is applied to classify and illustrate the existing diversity of hybrid systems, highlighting organizations that have received most attention among researchers.

- Next, the thesis contributes models for first-order estimation of system-level execution time and energy of conventional and hybrid main memory systems. The models embody a light-weight tool for obtaining insights about memory system design trade-offs. They power a model named *Rock*, that illustrates the potential of design-time resource partitioning for improving memory system performance.

- Further, the models enable the final contribution of the thesis: *Crystal*, a designtime resource partitioning method for hybrid main memory [32]. Crystal facilitates quick and early identification of the most promising resource partitioning options for detailed evaluation. Thus, Crystal greatly simplifies the design process and represents a valuable addition to the system designer's toolbox.

### **1.3** Thesis Organization

The rest of the thesis is organized as follows. Chapter 2 first explains how programs and workloads—the stimuli of the memory system—are represented and classifies them by memory behavior. The chapter identifies the type of workloads that benefit from hybrid main memory and introduces programs used for composing workloads in this thesis. Next, memory technologies—the building blocks of hybrid memory systems—are presented in Chapter 3 from basic memory cell properties to device organization and operation to device modeling. The device models provide estimates of device characteristics used throughout this thesis (including Figure 1.1). Chapter 4 presents the first contribution, a taxonomy of hybrid main memory systems, systematizing the existing plurality of their organizations. Chapter 5 leverages the previous chapters and presents the second and third contributions of this thesis: Section 5.1 describes the models for system-level execution time and energy, Section 5.2 introduces Rock, and Section 5.3 presents Crystal. The thesis is concluded by Chapter 6 offering a review of the contributions in Section 6.1 and an overview of future work in Section 6.2.

CHAPTER 1. INTRODUCTION

# 2

# Workload Methodology

Workloads are the stimuli driving design decisions in computing systems. It takes a certain amount of time and energy to produce results for a particular workload on a particular system, and reducing system-level execution time and/or energy are major design goals. The goals can be achieved by optimizing system hardware, software, or the code of the workload. This thesis is about optimizing the main memory of computing systems by increasing its capacity for executing workloads faster and with less energy.

A workload may comprise one or more programs that are single- or multi-threaded. This thesis considers multi-program workloads where each program is single-threaded. Benefits from memory system optimization realizable by workloads depend on their memory behavior. This thesis uses workloads for which execution time and energy can be reduced by increasing main memory capacity.

Main memory optimizations can be evaluated using simulators of different degrees of detail (e.g., full-system, system-call emulation, execution-driven, or trace-driven) or analytic memory models. The latter approach represents systems at the highest level of abstraction compared to the other approaches and thus is the fastest. As has been stated in Section 1.1, the design space of interest in this thesis is large and detailed modeling impedes its extensive exploration. Analytic modeling facilitates such extensive exploration and thus suits the purposes of this thesis best. It requires representing each program by a profile (described in Section 2.1), and the procedure of recording profiles is labeled *profiling* here. The aggregate behavior of programs in a workload is modeled by distributing available main memory capacity among the programs in a way that represents their memory behavior (as defined by their profiles) as well as memory management.

The next section explains profiling of single-thread programs, Section 2.2 describes the representation of entire workloads, and Section 2.3 introduces a workload classification by the kind of benefits that workloads enjoy from memory system optimizations. Section 2.4 presents the profiling setup and the profiles of programs used for composing workloads in this thesis, and Section 2.5 summarizes the chapter.

### 2.1 Program Profiling

The goal of profiling in this thesis is to create compact representations of programs sufficient for quick evaluation of main memory optimization ideas in Chapter 5. Such profiling requires the detailed execution and analysis of a program just once, when recording its profile, as described further in this section. Each evaluation iteration reuses the profile instead of running the program in detail, and this dramatically reduces the computation effort of evaluation.

Memory system optimization is typically performed for specific program execution intervals of interest. Information in main memory is managed at the granularity of an Operating System (OS) page, and pages referenced by a program during an execution interval constitute the program's *working set* of that interval [33]. In this thesis, each program is profiled for its dominant execution interval in the *steady state*, i.e., after system warmup, when no cold (compulsory) misses in the LLC occur. A profile contains:

The miss curve below LLC, denoted by Miss(C), i.e., the number of main memory capacity misses as a function of its capacity C, where main memory is fully-associative and employs the Least Recently Used (LRU) replacement policy. In general, the miss curve can represent all memory references of the program, but here LLC filters them, such that the miss curve represents only accesses below LLC. It shows how the number of disk accesses reduces as the capacity of main

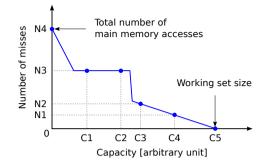

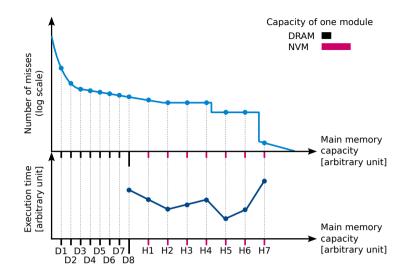

Figure 2.1: Example miss curve

memory is increased, and is thus an essential program characteristic for evaluation of memory system optimizations that increase main memory capacity.

- The fraction of writes below LLC, denoted by fWr, required for distinguishing read and write misses at each point of the miss curve: Among y = Miss(x) misses for each capacity x, (1 − fWr) · y are read misses, and fWr · y are write misses. Distinguishing reads and writes is important, because memory technologies can have asymmetric read and write access characteristics, as described in Chapter 3.

- 3. The time spent on computation plus all cache accesses, denoted by  $T_{CPU}$ , required for representing the constant part of execution time that is not affected by main memory optimization.

The miss curve represents the size of the working set and the reuse distance (LRU stack distance [34]) of pages within the working set, as explained below. Figure 2.1 shows an example miss curve, where capacity is expressed in arbitrary units. The total number of main memory accesses is defined by the Miss(0) point (e.g., N4 in Figure 2.1). Each point of the miss curve corresponds to the number of capacity misses made by the program if it is given the amount of memory denoted by the horizontal coordinate of the point, where that memory is fully associative and implements the LRU replacement policy. The number of disk accesses is given by the point with the horizontal coordinate equal to the main memory capacity allocated to the program. For instance, if the program is allocated capacity C4, it makes N1 disk accesses. The working set size is given by the horizontal coordinate of the point C4, it makes N1 disk accesses. The working set size is given by the horizontal coordinate of the point where the number of misses is zero, because cold misses are not profiled (e.g., C5 in Figure 2.1).

The reuse distance of pages within the working set is represented by the steepness of the miss curve: The number of misses y at each capacity x, expressed in the number of pages, is equal to  $N_{total} - N_{hit} - N_{cold}$ , where  $N_{total}$  is the number of accesses to all pages in the working set (the total number of main memory accesses), N<sub>hit</sub> is the number of accesses to pages with reuse distances less than x, and  $N_{cold}$  is the number of cold misses ( $N_{cold} = 0$  because cold misses are not profiled). If the miss curve decreases from point  $(x_0, y_0)$  to point  $(x_1, y_1)$ , i.e.,  $x_0 < x_1$  and  $y_0 > y_1$ , it means that there are pages with reuse distances greater than or equal to  $x_0$  and less than  $x_1$ , where both  $x_0$ and  $x_1$  are expressed in the number of pages. Thus, increasing main memory capacity from  $x_0$  to  $x_1$  reduces the number of disk accesses. For instance, such are capacities C3 and C4 in Figure 2.1, respectively (N2 > N1). If the miss curve is flat between the two points (forms a flat plateau), i.e.,  $x_0 < x_1$  but  $y_0 = y_1$ , it means that pages with reuse distances greater than or equal to  $x_0$  actually have reuse distances greater than or equal to  $x_1$ . Thus, increasing main memory capacity from  $x_0$  to  $x_1$  does not reduce the number of disk accesses. For instance, such are capacities C1 and C2 in Figure 2.1, respectively (the number of misses is N3 at both C1 and C2). In general, a program can have pages with different reuse distances, making the shape of the program's miss curve complex: It may contain a number of decreasing and flat fragments.

The shape of the miss curve is linked to the concept of *utility* of memory capacity as follows. A program's utility of a given capacity can be defined as the reduction in the number of misses that the program enjoys if it obtains the capacity. The steeper the miss curve between points  $(x_0, y_0)$  and  $(x_1, y_1)$ , i.e., the greater  $y_0 - y_1$ , the higher the program's utility of main memory capacity  $x_1 - x_0$ . The flatter the miss curve between the two points, i.e., the smaller  $y_0 - y_1$ , the lower the program's utility of that capacity. For instance, the utility of capacity C2 - C1 in Figure 2.1 is zero, and the utility of capacity C3 - C2 is N3 - N2. The concept of utility is used in the next section, when defining the aggregate behavior of programs in a multi-program workload.

### 2.2 Workload Representation

Multi-program workloads where each program is defined by its profile are represented as follows. All programs in a workload are single-threaded, assigned one per core, and run concurrently. Available main memory capacity is distributed among them at design-time by a procedure labeled *Design-time Resource Allocation (DRA)*. Each program is allocated memory capacity according to its utility of capacity relative to that of the

### 2.2. WORKLOAD REPRESENTATION

other programs in the workload. DRA represents characteristics of both the programs and memory management. A memory management policy is labeled *low-utility* DRA policy if it allocates more memory capacity to programs with low utility of it, and it is labeled *high-utility* if it allocates more capacity to programs with high utility of it.

A program's utility of a particular memory capacity slice is estimated by the program's miss curve. For instance, programs A and B have been allocated 1MB each, and there is another 1MB slice to allocate. Program A has 10M misses at capacity 1MB and 1M misses at capacity 2MB, and program B has 10M and 9M misses at these capacities, respectively. The difference in the number of misses between the two capacities is greater for program A, thus it has a higher utility of the 1MB slice than program B and wins it according to the high-utility DRA policy. Program B has a lower utility of the slice and thus wins it according to the low-utility DRA policy.

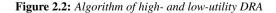

There are multiple ways of implementing DRA. For a given multi-program workload and DRA policy, the final distribution depends on an initial allocation and the granularity of DRA. The final distribution is represented by main memory slices allocated to each program in the workload. The initial allocation defines main memory capacity allocated to each program by default (the minimum that each program gets when it starts execution). The granularity of DRA defines how much memory is awarded to a program at each iteration of DRA. Figure 2.2 shows my implementation of the high- and low-utility DRA. The algorithm starts with an initial allocation where each program in the workload gets slice cs<sub>min</sub> of main memory capacity. Flag done for each program indicates if allocation has been completed, i.e., if the program has been allocated enough main memory capacity to fit its entire working set. The working set size of each program, denoted by  $wss_i$ , is the horizontal coordinate of the last point of the program's miss curve.  $C_{left}$  keeps track of available main memory (left for allocation). After initial allocation, the algorithm distributes available memory capacity iteratively at the granularity of a capacity slice delta ( $\Delta cs$ ). For each program, the difference in the number of misses  $\Delta N$  is estimated between two points on the miss curve: one at the current slice and one at the new capacity that is the current slice plus the slice delta. If the current capacity is such that it entirely fits the working set of a program, the program is labeled *done*. If the new capacity exceeds the working set size of a program, the last point of the miss curve is extended (then the number of misses at the new capacity is zero, since cold misses are not profiled). On the next step, a list is created of  $\Delta N$  of programs that still participate in DRA, i.e., those not yet labeled as *done*. If the high-utility policy is chosen, the list is sorted in descending order, such that the program with the largest  $\Delta N$  (the highest utility) is on the top of the

#### Data:

*n* programs defined by their miss curves  $Miss_i(C)$  and working set sizes  $wss_i, 0 \le i < n$ Total main memory capacity Ctotal Minimum capacity slice csmin allocated per program Capacity slice delta  $\Delta cs$  that is iterative allocation granularity DRA policy type dra\_type (high- or low-utility) Result: Capacity slices for each program  $cs_i$ ,  $0 \le i < n$ 1 foreach program  $i, 0 \le i \le n$  do  $cs_i = cs_{min}$ /\* Initial allocation \*/ 2  $done_i = False$ 3 4  $C_{left} = C_{total} - n \cdot cs_{min}$ 5 while  $C_{left}$  and allocation not done for all programs do foreach program  $i, 0 \le i \le n$  do 6 if  $cs_i \geq wss_i$  then 7  $\Delta N_i = 0$ /\* Allocation for program is done \*/ 8 9  $done_i = True$ else 10 if  $cs_i + \Delta cs > wss_i$  then 11  $\Delta N_i = Miss(cs_i) - Miss(wss_i)$ 12 else 13  $\Delta N_i = Miss(cs_i) - Miss(cs_i + \Delta cs)$ 14 Create list  $[\Delta N]$  of  $\Delta N_i$  for  $0 \le i < n$  such that  $done_i = False$ 15 if dra\_type is high-utility then 16 /\* High-utility DRA \*/ Sort  $[\Delta N]$  in descending order 17 else 18 /\* Low-utility DRA \*/ Sort  $[\Delta N]$  in ascending order 19 Programs with same  $\Delta N$  as program on top of list are *winners* 20 foreach program in winners do 21 if  $C_{left}$  then 22  $cs_i += \Delta cs$ /\* Award  $\Delta cs$  to program \*/ 23  $C_{left} = \Delta cs$ 24 **25 return**  $cs_i, 0 \le i < n$

**Figure 2.3:** *Miss curves for illustrating high-utility, low-utility, and utility-agnostic DRA policies*

list. If the low-utility policy is chosen, the list is sorted in ascending order, such that the program with the smallest  $\Delta N$  (the lowest utility) is on the top. Starting with the program on the top of the list, programs with the same  $\Delta N$  are labeled *winners*, awarded the capacity slice delta, and available memory capacity  $C_{left}$  is updated accordingly. When there is not enough memory available, some programs might not be awarded the slice delta even if they are *winners*. This iterative DRA repeats until either all programs in the workload have been allocated enough capacity to fit their entire working sets, or until there is no more main memory available.

The total number of disk accesses for a given workload is not always smaller if the high-utility DRA policy is employed instead of the low-utility one. Consider the example miss curves of programs P1 and P2 in Figure 2.3. P1 and P2 form a workload. Point 0 on the horizontal axis corresponds to an initial capacity allocation, and there are five capacity slices (expressed in arbitrary units) to distribute between the programs. Let us first consider the low-utility DRA policy. P1 wins the first slice because A - B < A - C, the second and third slices because B - B < A - C, and the fourth and fifth slices because B - D < A - C and D - 0 < A - C, respectively. The number of disk accesses is zero for P1, A for P2, and hence A for the entire workload. Let us now consider the high-utility DRA policy. P2 wins the first slice because A - B > P wins the second slice because A - B > C - E. Now P1 has hit its flat plateau, and P2 wins the remaining three slices because its miss curve is decreasing. The number of disk accesses is B for P1, D for P2, and hence B + D for the workload. The high-utility

DRA policy has resulted in a greater number of disk accesses made by the workload than the low-utility DRA policy (B + D > A).

Another distinct DRA policy is agnostic to utility and distributes the available capacity evenly among programs in the workload, as long as their working sets do not fit entirely into their respective capacity slices. I label this policy *utility-agnostic* DRA policy. For the example miss curves in Figure 2.3 and the five capacity slices in question, the policy results in three slices allocated to P1 and two slices allocated to P2, given that allocation starts with P1. The number of disk accesses made by the workload is thus B + E, which is by E - D greater than that if the high-utility DRA policy is used.

### 2.3 Workload Classification

A workload is labeled *in-memory* if it does not access disk in the steady state (after system warmup), i.e., its working set fits entirely into main memory. Likewise, a workload is labeled *not-in-memory* if it accesses disk in the steady state, i.e, its working set size exceeds the capacity of main memory.

As a result of memory system optimization, main memory capacity can be increased. For instance, the baseline memory technology can be partly replaced with a technology that enables storing more bits. In-memory workloads do not benefit in terms of execution time and energy from a larger memory capacity, because their working sets fit into the baseline capacity, and increasing capacity cannot decrease the number of capacity misses. Not-in-memory programs benefit from a memory capacity increase as long as there are pages with reuse distances greater than or equal to the baseline capacity and less than the increased capacity (where the capacities are expressed in the number of pages).

### 2.4 Profiling Setup and Program Profiles

A program profile contains the miss curve (Miss(C)), the fraction of writes (fWr), and the computation and cache time  $(T_{CPU})$ , as described in Section 2.1. A profile of a program can be extracted from its memory access trace and execution statistics recorded during the interval of interest. For instance, they can be obtained with: 1) a simulator (e.g., gem5 [35]) including models of a CPU and its cache hierarchy; or 2) an executiondriven (e.g., Pin [36] or Valgrind [37]) model of a cache hierarchy. In this thesis, I compile programs from SPEC CPU2006 [38] and NPB 3.3 [39] for the 64-bit extension of x86 and run them individually on gem5 to record main memory access traces and execution statistics in the system-call emulation mode (system calls are not profiled). For each program, the miss curve is reconstructed from its main memory access trace using Mattson's stack algorithm [34] at the granularity of a 4KB page. gem5 is configured to simulate an in-order CPU running at 1GHz with 64KB, 4-way, LRU, split L1 caches and a 1MB, 8-way, LRU, unified L2 cache. The cache line size is 64B. The SPEC CPU2006 programs are profiled with reference inputs and the NPB 3.3 programs are profiled with large problem sizes (e.g., size C for CG). For each program, I identify one major 2B-instruction execution interval using the SimPoint methodology [40] and simulate it after fast-forwarding and warming the system for 500M instructions. A single execution interval does not fully represent an entire program, but I observe that the working set sizes of the major execution intervals closely match those of the entire programs.

For brevity, I choose a subset of programs with larger working sets (above 150MB) and diverse behavior, as described below. The programs are:

- CG, a conjugate gradient kernel with irregular memory accesses as a result of sparse matrix-vector multiplications;

- 470.1bm, a computational fluid dynamics program implementing a lattice Boltzmann method;

- 429.mcf, a combinatorial optimization program implementing single-depot vehicle scheduling using a network simplex algorithm accelerated with a column generation;

- 458.sjeng, an artificial intelligence program playing chess by implementing game tree search and pattern recognition; and

- 450.soplex, a simplex linear program solver employing sparse linear algebra.

Program names are used as profile names for simplicity. For instance, lbm denotes 470.lbm with the reference inputs during its major 2B-instruction execution interval. Likewise, mcf, sjeng, and soplex denote 429.mcf, 458.sjeng, and 450.soplex, respectively.

Table 2.1 shows that the working set sizes of CG and 1bm are similar, but CG has about 100× smaller fraction of writes (fWr) and about 2× greater computation and cache time  $(T_{CPU})$ . Evaluating a memory system optimization first using workloads containing CG and then workloads containing 1bm can help reveal how the results of the optimization depend on fWr and  $T_{CPU}$ . The working set of mcf is the largest among the programs, and that of sjeng is the smallest (about 10× smaller than the working set of mcf, about 2.5× smaller than those of CG and 1bm, and about 1.5×

### 2.5. SUMMARY

|                       | CG  | lbm  | mcf  | sjeng | soplex |

|-----------------------|-----|------|------|-------|--------|

| Working set size [MB] | 419 | 403  | 1674 | 172   | 251    |

| fWr <b>[%]</b>        | 0.4 | 42.9 | 20.2 | 44.1  | 16.5   |

| $T_{CPU}$ [S]         | 8.4 | 4.4  | 6.6  | 3.4   | 4.6    |

Table 2.1: Selected characteristics of CG, 1bm, mcf, sjeng, and soplex

smaller than that of soplex). The programs can be used for composing multi-program workloads with aggregate working set sizes that differ by increments from hundreds of megabytes to gigabytes. Such workloads are essential for the evaluation of memory system optimizations that increase main memory capacity.

Figure 2.4 shows that the miss curve of each program, except sjeng, has a distinct plateau representing the bulk of the working set, and a relatively small part referenced significantly more than the remainder of the working set. For mcf, such part is about 100MB and forms a plateau itself. Decreasing fragments of the miss curves illustrate that pages have gradually increasing reuse distances. Flat fragments of the miss curves illustrate that pages have equal reuse distances. For instance, lbm's plateau is totally flat, and thus the pages of the bulk of its working set share the same reuse distance that is the size of the entire working set. On the contrary, sjeng has no plateaus, its miss curve decreases monotonically, and so the pages of its working set have different, gradually increasing reuse distances.

### 2.5 Summary

Programs in a multi-program workload are represented by compact profiles. The profiles are recorded once and reused throughout the evaluation of main memory optimizations. Memory management and the way programs affect each other's behavior are represented by DRA. The high- and low-utility DRA policies are two distinct cases of DRA driven by the program utility of memory capacity. The utility-agnostic DRA is a distinct example of a policy that neglects the program utility of memory capacity. Not-in-memory workloads are of primary interest in this thesis, since they benefit in terms of execution time and energy from a main memory capacity increase that can be achieved by memory system optimizations. The next chapter presents memory technologies that make such optimizations possible.

# **S** Memory Technologies

Memory technologies are the building blocks of memory systems. A number of technologies with different characteristics exist today, and they have to be well understood in order to choose the most appropriate technologies for a particular memory system. The characteristics vary among technologies and even across different device implementations of the same technology. In order to correctly interpret numbers reported by various sources and to be able to model the operation of memory devices, it is necessary to understand their basic organization and operational principles. This chapter describes these principles without going too deep into the nuances of Very Large Scale Integration (VLSI). Section 3.1 presents memory technologies as follows. First, the fundamental cell characteristics are presented: basic memory cell physics (the principles of storing data in the memory element), cell structure (the mechanism of accessing the memory element), and cell bit density (the number of bits per cell, i.e., the number of bits encoded by a single physical state of the memory element). They determine such memory characteristics as data retention (the period of time during which the cell remains stable without power)

and write endurance (the maximum number of cell state modifications that the cell can perform reliably). Next, Section 3.2 presents ways of organizing cells into arrays and accessing them on the device level that eventually affect the device access latencies, access energies, and maintenance overhead (e.g., for maintaining data integrity within the arrays and during transfers across the device interface). The specifics of device organization, implementation, and fabrication determine the area efficiency and thus the bit density of the device. Section 3.3 introduces my analytic, device-level models for estimating the timing, energy, and power characteristics of DRAM, PCM, NAND Flash, SSD, and HDD.

#### 3.1 **Basic Memory Cell Properties**

Memory technologies are classified as *charge-based* if they represent data as electric charge. Otherwise, e.g., if data are represented as resistance, memory technologies are classified as *non-charge-based*. Memory technologies are classified as *Single-Level Cell (SLC)* if one memory cell state encodes one bit of information, and as *Multi-Level Cell (MLC)* if it encodes two or more bits. Memory technologies are typically classified as *volatile* if their cells lose state within seconds after disconnecting from power, otherwise they are classified as *non-volatile*.

#### 3.1.1 DRAM

DRAM is a charge-based, One Transistor and One Capacitor (1T1C), SLC memory technology. One bit of data is stored as charge on the capacitor of the memory cell. The capacitor is accessed via the transistor. Charge leaks from the capacitor, thus DRAM is a volatile technology. It is typically required for data integrity that charge is *refreshed* each 64ms at temperatures from  $0C^{\circ}$  to  $85C^{\circ}$  and each 32ms at temperatures from  $85C^{\circ}$  to  $95C^{\circ}$  [41]. Primarily because the charge is unstable, one DRAM cell encodes a single bit. Reading (sensing) the cell depletes the capacitor, thus DRAM reads are destructive. DRAM cells have endurance of about  $10^{16}$  accesses, primarily defined by the endurance of the access transistor. DRAM is a mature technology and is conventionally employed in the main memory of computing systems. It is used as the baseline memory technology in this thesis.

#### 3.1.2 Flash

Flash is a charge-based, One Transistor (1T), SLC/MLC memory technology. The cell transistor has both the control gate and a *floating* gate that is not directly connected to any control signals. Data are stored as charge on the floating gate of the transistor. The cell is programmed by injecting electrons into the floating gate and erased by ejecting them out from the floating gate by means of quantum tunneling. The cell can be programmed only if it is first erased. The floating gate is electrically isolated from the control gate by the interpoly oxide and from substrate by the tunnel oxide, which prevents charge leakage. Thus, Flash is a non-volatile technology, and its retention time is typically above ten years. Because the charge is stable and can be controlled, the cell can encode a number of bits. However, the higher the number of bits per cell, the lower the cell endurance: Each program/erase cycle damages the tunnel oxide of the floating gate, creating defects that trap electrons thus degrading its electrical characteristics and narrowing margins between different cell states. As a result, the programmed and erased states of a worn-out cell cannot be reliably distinguished. The endurance of SLC Flash is about 10<sup>5</sup> program/erase cycles [9], and that of three-bit MLC Flash is about  $10^3$  cycles [42]. Flash is a mature technology and is of interest in this thesis because it enables high-density storage.

#### 3.1.3 PCM

PCM is a non-charge-based, One Transistor and One Resistor (1T1R), SLC/MLC memory technology. Bits of information are stored as the resistance of the chalcogenide alloy of the cell, as described below. The cell is programmed (set) when the alloy is in the polycrystalline phase (low resistance). This phase is achieved by first melting the alloy by injecting current and then cooling it at a rate slower than the crystal growth rate. If the melted alloy is cooled at a rate faster than the crystal growth rate, it gets locked in the amorphous phase (high resistance), and the cell becomes erased (reset). PCM is a non-volatile technology, but is prone to the resistivity drift effect: The resistance of the alloy in the amorphous phase continuously increases and is highly temperature-dependent. Resistivity drift does not matter for SLC PCM, but complicates the implementation of MLC PCM. However, there are mechanisms for coping with the negative effect of the drift [43, 44], and PCM is commonly used as an MLC technology. Because of thermal expansion and contraction, each set/reset cycle degrades the current injection contacts and the resistance uniformity of the chalcogenide alloy. The endurance of PCM cells is estimated from  $10^5$  to  $10^8$  set/reset cycles [10, 45, 46]. PCM is a relatively new

technology and is popular among researchers. It is of interest in the scope of this thesis because: 1) it is MLC-capable and 2) it employs different device physics compared to Flash and thus offers significantly different timing and electrical characteristics, as is shown later in this chapter.

#### 3.1.4 Magnetic Memory

One example of magnetic memory is Magnetoresistive Random Access Memory (MRAM): a non-charge-based, One Transistor and One Magnetic Tunnel Junction (1T1MTJ), SLC technology. The Magnetic Tunnel Junction (MTJ) comprises two ferromagnetic layers: one *fixed* (the direction of magnetization is fixed) and one *free* (the direction of magnetization can be changed). One bit of information is stored as the magnetization of the free layer relative to the fixed layer: The MTJ is in the reset state (low resistance) when the two layers are parallel (spin-aligned) and in the set state (high resistance) when the layers are anti-parallel. MRAM is a non-volatile technology and has the endurance of 10<sup>16</sup> write cycles, primarily defined by the endurance of the access transistor [47]. Spin Transfer Torque Magnetoresistive Random Access Memory (STT-MRAM) is a contemporary implementation of MRAM and uses spin-polarized current to change the magnetic orientation of the free layer [48]. It is a promising technology and attracts vivid interest of memory researchers. However, neither STT-MRAM nor MRAM are explicitly considered further in this thesis, because they do not currently offer higher bit densities than DRAM [47, 49].

Another representative of magnetic memory is the ferromagnetic material covering the platters of HDDs. One bit is stored as the direction of magnetization of a magnetic region on a track of a platter [5]. The direction of magnetization is read and written by an external head. This is a mature technology conventionally employed in the backing store of computing systems.

#### 3.1.5 Other Technologies

The plurality of memory technologies is not limited to those described above. For instance, one NVM technology of active research is Resistive Random Access Memory (RRAM): a non-charge-based, 1T1R, and MLC-capable. Data are stored as the resistance of the metal oxide of the cell. The cell is set (low resistance) when conductive *filaments* (paths) are formed in the metal oxide and reset (high resistance) when the filaments are ruptured.

The endurance of SLC RRAM ranges from  $10^6$  to  $10^{10}$  set/reset cycles [50, 51], and that of two-bit MLC RRAM is about  $10^7$  cycles [52].

Another prominent example of an NVM technology is Ferroelectic Random Access Memory (FeRAM): a non-charge-based, 1T1C, SLC memory technology. One bit is represented by the polarization of the thin film of a ferroelectric material placed between two electrodes in a way similar to the structure of a capacitor [53]. FeRAM endurance is estimated from 10<sup>10</sup> to 10<sup>13</sup> read/write cycles [54, 55].

Despite the specifics of their basic device physics and operational characteristics, these technologies are not explicitly considered further in this thesis. The term Storage-Class Memory (SCM) is used for collectively denoting such NVM technologies. The characteristics of interest for main memory optimization by increasing its capacity are represented by DRAM, Flash, and PCM.

#### 3.2 Device Organization and Operation

Memory devices are classified as *mechanical* if they contain moving parts, otherwise they are classified as *solid-state*. This section first describes the general organization and operation of a basic solid-state device. Then it illustrates by example implementation details specific to DRAM, PCM, and Flash, and concludes by describing SSDs (compound solid-state devices) and HDDs (mechanical storage devices).

#### 3.2.1 Basic Solid-State Device

Memory cells of a single solid-state device are organized into an array with *word lines* along rows and *bit lines* along columns. Memory arrays may be logically subdivided into smaller units such as *blocks*, *pages*, or *words* that define the granularity of memory array operations. A *die* may contain one or more memory arrays, each having dedicated sensing and buffering circuitry. The sensing circuits are often referred to as *sense amplifiers* and are required for reading data out from the memory array into the buffering circuitry (which may be integrated with the sense amplifiers). The buffering circuitry is further referred to simply as a *buffer*. Memory *array read* latency is the time required for reading data from the array into the buffer, and the memory *array write* latency is the time required for writing data back from the buffer to the array.

The buffer stores data for fast reads and writes (*column accesses*) via an Input/Output (I/O) interface. The number of I/O data pins, denoted by  $N_{DQ}$ , matches the *word width*

(or *device width*) that is denoted by  $\times N_{DQ}$ . For instance, an  $\times 8$  device has eight data pins. An input *data mask* pin can be used for masking nonvalid write data. The buffer is typically larger than one word and may be accessed at different granularities or *burst sizes*, i.e., one or more words may be transferred between the buffer and the I/O data pins per column access. *Peak data rate* is the product of the device width and the I/O interface speed. It is the maximum theoretical bandwidth of the I/O data interface. An I/O interface may be synchronous, and it is called a Double Data Rate (DDR) interface if it transfers data on both the rising and falling edges of the I/O clock. High-speed data interfaces require for signal integrity bidirectional *data strobe* pins (e.g., one differential pair) that are used for indicating when read and write data must be captured.

On-die control circuitry implements the command protocol and orchestrates internal operations. Data interfaces running at high frequencies require additional circuits, such as Delay-Locked Loop (DLL), and additional operations for signal integrity maintenance [41]. Static power (sometimes referred to as *background* power) is dissipated when the memory device is powered-on and clocked but not in use, i.e., there are no ongoing internal operations. Power-down (low power) modes may be entered by disabling parts of the die, e.g., the clock circuitry, DLL, and memory array periphery such as row and column decoders.

A single memory device may be composed of one or more dies within a package. Memory devices are often organized into *ranks* such that all devices within a rank are identical and operate in lock-step, servicing the same command simultaneously. The peak data rate of a rank is thus the sum of the peak data rates of all the devices composing it.

#### 3.2.2 DRAM Device

Organizational and performance characteristics of an example  $\times$ 8 DRAM device [8] are presented in the first column of Table 3.1. The DRAM cells are organized into eight arrays (*banks*), each of which is subdivided into pages (*rows*) of 1KB, such that one array contains 16K pages. The array buffer is referred to as a *row buffer*. A DRAM array is ready for a read operation when its bit lines are precharged. DRAM array reads are destructive, i.e., the page data in the array get lost after they have been read out into the row buffer. The operations of writing a page back and precharging the array bit lines for the next read are collectively referred to as a *precharge* operation. The DRAM device in Table 3.1 implements the widely used third generation of the double data rate (DDR3) Synchronous Dynamic Random Access Memory (SDRAM)

| Characteristic  | Units       | DRAM              | PCM                  | NAND Flash         | NOR Flash                |

|-----------------|-------------|-------------------|----------------------|--------------------|--------------------------|

| Volatile        |             | yes               | no                   | no                 | no                       |

| Cell endurance  | write cycle | $10^{16}$         | $10^{8}$             | $10^{5}$           | $10^{5}$                 |

| Cell capacity   | b/cell      | 1                 | 1-4                  | 1                  | 2                        |

| Die capacity    | Gb          | 1                 | 1-4                  | 16                 | 1                        |

| Block size      | KB          | _                 | Σ                    | 512                | 128                      |

| Page size       | В           | 1024              | as for DRAM          | 4096               | 32                       |

| Word width      | b           | 8                 | Ď                    | 8                  | 16                       |

| Clock frequency | MHz         | 800               | s fo                 | 83                 | 52                       |

| DDR             |             | yes               |                      | yes                | no                       |

| Peak data rate  | Mb/s        | $12.8{\cdot}10^3$ | Same                 | 1328               | 832                      |

| Burst size      | В           | 8                 | 0)                   | 1 - 4096           | 2-32                     |

| Latencies:      |             |                   |                      |                    |                          |

| Array read      | ns/page     | 13.75             | 48 - 250             | $25 \cdot 10^{3}$  | 100                      |

| Array write     | ns/page     | 13.75             | $150 - 2 \cdot 10^3$ | $230 \cdot 10^{3}$ | $(270 - 900) \cdot 10^3$ |

| Array erase     | ms/block    | _                 | _                    | 0.7                | 800                      |

Table 3.1: Characteristics of example DRAM, PCM, NAND and NOR Flash devices

interface [41], that yields a peak data rate of 12.8Gb/s at a device clock frequency of 800MHz. Such a high-speed interface requires signal integrity maintenance performed by output impedance (ZQ) calibration [41]. DDR3 supports the burst size of eight words, hence the granularity of a column access is eight bytes for the  $\times$ 8 device considered here. In addition, DDR3 supports the burst size of four words, but it is emulated, i.e., implemented by masking the last four words of the default eight-word burst. DRAM is volatile and requires periodic *refresh* operations that read data from the array into the row buffer and then write the data back.

#### 3.2.3 PCM Device

PCM device organization is commonly assumed to be similar to that of DRAM devices. Thus, the differences between PCM and DRAM devices lie primarily in the characteristics related to the memory cell: endurance, bit capacity, and array read and array write latencies and dynamic energies. Example  $\times 8$  PCM device organization and performance characteristics are presented in the second column of Table 3.1. The PCM device can be assumed to have from one to four times the capacity of the DRAM device discussed above because of its MLC capability and a potentially smaller cell area [16]. The device employs the same I/O interface as the DRAM device. PCM reads are non-destructive, and depending on the device implementation the array read latency can be from several times to at least  $10 \times$  greater than that of DRAM [10, 56]. The PCM array write latency can be from about  $10 \times$  to  $100 \times$  greater than that of DRAM, as determined by the time required for setting the cell into the low-resistance state. In this context, the main advantage of PCM over DRAM is its higher bit density.

#### 3.2.4 NAND Flash Device

NAND Flash is one of the flavors of Flash memory. Unlike DRAM and PCM arrays where each cell is directly connected to its bit line, NAND Flash physically organizes cells into *strings* (in series) such that all cells in one string share a single bit line contact [57]. Reducing the number of bit line contacts reduces the area overhead per cell and thus increases the bit density. The complication of NAND Flash is that reading and programming a single cell of a string requires setting all other cells of that string into specific temporary modes that enable modifying the state of the target cell only [58].

Example characteristics of an  $\times 8$  SLC NAND Flash device [9] are presented in the third column of Table 3.1. In this example device, cells are organized into two arrays (planes) that are subdivided into blocks of 512KB, and the blocks are subdivided into pages of 4KB. There are 128 pages per block and 2K blocks per array, giving each array 256K pages. Each page also contains additional data (224B) for book-keeping purposes, that are excluded from consideration here for ease of page size comparison among technologies. Array read and program operations are performed on the granularity of a page, and array erase operations are performed on the granularity of a block. The NAND Flash page of the example device is four times larger than that of the DRAM device discussed above. The capacity of the NAND Flash device is 16 times greater than that of the DRAM device and is at least four times greater than that of the PCM device. There are MLC NAND Flash devices of even greater capacities in production, but their cell endurance is lower (e.g.,  $3 \cdot 10^3$  program/erase cycles [42]) than the  $10^5$  cycles of the example SLC NAND Flash device. The endurance of the example NAND Flash device is three orders of magnitude lower than that of the PCM device discussed above. Memory technologies like RRAM have the promise to improve the endurance of high-density devices with array read and program latencies similar to those of NAND Flash [59]. Thus, the endurance problem of NAND Flash is not of interest in this thesis, and NAND Flash is used as an example NVM technology in terms of bit density and access characteristics. The NAND Flash I/O data interface (Open NAND Flash Interface (ONFI) [60]) supports double data rate with an approximately  $10 \times$  lower peak data rate than that of the example DRAM device. The NAND Flash protocol allows reading out an entire page in one burst. In addition, it allows changing the start word (column) and reading out as many words as needed up to the end of the page. The NAND Flash array read latency is at least three orders of magnitude greater than that of DRAM and at least  $100 \times$  greater than that of PCM. The array write latency is at least four orders of magnitude greater than that of PCM.

#### 3.2.5 NOR Flash Device

Another flavor of Flash memory is NOR Flash, that organizes cells into arrays such that each cell is directly connected to its bit line and can be accessed independently [61]. Characteristics of an example  $\times 16$  MLC NOR Flash device [62] are presented in the last column of Table 3.1. Despite its MLC capability, the device happens to have the same endurance as the example SLC NAND Flash device, and the same capacity as the example SLC DRAM device. NOR Flash cells are organized into blocks of 128KB, and one block is the granularity of the erase operation. The NOR Flash page is not an organizational unit of the memory array but just a small buffer that supports random accesses at the word granularity. Unlike the devices discussed above, the NOR Flash device is 16-bit wide, because it is a typical width of the parallel NOR Flash interface. The interface is word-addressable and can operate in the synchronous mode with a peak data rate of 832Mb/s, which is of the same order of magnitude but lower than that of the NAND Flash device. The NOR Flash protocol allows reading out an entire page in a burst at the word granularity. The NOR Flash array read latency is about 10× greater than that of DRAM, falls within the range of the PCM array read latencies, and is at least  $100 \times$  smaller than that of NAND Flash. The NOR Flash array write latency depends on the granularity of operation, from one word (which is comparable to the NAND Flash array write latency) to 512 words (which is about  $3.5 \times$  greater). The NOR Flash array erase latency is at least three orders of magnitude greater than that of NAND Flash.

NOR and NAND Flash storage arrays do not have to be taken as one with their respective legacy interfaces. Both NOR and NAND Flash can be assumed to employ the DDR3 interface, just like it is assumed for PCM. The greater device capacity of NAND Flash makes it a better representative of slow but bit-dense NVM technologies. Thus, NAND is the Flash flavor of primary interest in this thesis.

#### 3.2.6 SSD

NAND Flash has enabled Solid-State Disks (SSDs). NAND Flash devices inside an SSD are typically organized such that the I/O bandwidth is maximized by exploiting different forms of operation parallelism. SSDs typically implement mechanisms for hiding the long NAND Flash array write latency. In addition, SSDs can cache data, which further improves their access characteristics. A typical I/O interface employed by SSDs is the 6Gb/s Serial Advanced Technology Attachment (SATA) interface.

#### 3.2.7 HDD

Hard Disk Drives (HDDs) are the conventional backing store devices. An HDD comprises a number of magnetic platters (the storage medium) read and written by mechanical heads. Because of the moving parts, HDD access latencies are counted in milliseconds. The long read access latency can be significantly shortened by prefetching data from the storage medium into a cache [5]. Like SSDs, HDDs typically employ the 6Gb/s SATA interface.

#### **3.3 Device-Level Models**

This section presents device-level timing, power, and energy models for DRAM, PCM, NAND Flash, SSD, and HDD. The models for DRAM are derived from a device datasheet [8] and Micron's Power Calculator [63–66], that estimates power of a given memory utilization scenario. My models estimate dynamic energy per access and thus provide insights into device energy characteristics. Micron's models do not represent power mode transition overhead and can produce misleading results when power-down modes are modeled [67]. However, it is safe to derive from Micron's models here, because this thesis considers high-performance systems that do not use power-down modes. The models for PCM and NAND Flash adapt the DRAM models by sharing the DDR3 interface and by adding technology-specific modifications. For the purposes of this thesis, I model the following accesses:

- 1. A read access with one or more column reads that:

- a) misses in the buffer (requires an array read), denoted by read miss;

- b) hits in the buffer (the column read(s) are served immediately), denoted by read hit;

| Symbol | Description                   | Symbol | Description                     |

|--------|-------------------------------|--------|---------------------------------|

| ACT    | Activate command (array read) | PRE    | Precharge command (array write) |

| RD     | Read command (column read)    | REF    | Refresh command                 |

| WR     | Write command (column write)  | ZQCS   | ZQ Calibration Short command    |

Table 3.2: Subset of DDR3 SDRAM commands

2. A write access with one or more column writes that:

- a) misses in the buffer, denoted by write miss;

- b) hits in the buffer, denoted by write hit.

Accesses 1.a and 2.a are modeled for DRAM, PCM, and NAND Flash, but accesses 1.b and 2.b are modeled only for DRAM that satisfies the needs of Chapter 5.

#### 3.3.1 DRAM Models