## Symbolic Supervisory Control of Timed Discrete Event Systems

SAJED MIREMADI

Department of Signals and Systems

Automation Research Group

CHALMERS UNIVERSITY OF TECHNOLOGY

Gothenburg, Sweden 2012

## Symbolic Supervisory Control of Timed Discrete Event Systems SAJED MIREMADI ISBN 978-91-7385-765-9

© SAJED MIREMADI, 2012.

Doktorsavhandlingar vid Chalmers tekniska högskola Ny serie nr 3446 ISSN 0346-718X

Department of Signals and Systems Automation Research Group Chalmers University of Technology SE–412 96 Gothenburg Sweden Telephone + 46 (0)31 – 772 1000

Typeset by the author using LATEX.

Chalmers Reproservice Gothenburg, Sweden 2012

#### **Abstract**

With the increasing complexity of computer systems, it is crucial to have efficient design of correct and well-functioning hardware and software systems. To this end, it is often desired to *control* the behavior of systems to possess some desired properties. A specific class of systems is called *discrete event systems* (DES). DES deal with 'discrete' quantities, e.g., "number of robots in a manufacturing cell", and their processes are driven by instantaneous 'events', e.g., "start of a machine". In this thesis, the focus is on DES and an extension of such systems, which also considers the time points at which the events may occur, called *timed DES* (TDES). Real-time applications such as communication networks, manufacturing facilities, or the execution of a computer program, can be considered into TDES.

Having a DES or TDES, with some given *specifications*, by utilizing a well-known mathematical framework, called *supervisory control theory (SCT)*, it is possible to automatically generate a *supervisor* that restricts the system's behavior towards the specifications, only when it is necessary. Applying the SCT to large and complex systems, typically follows with some issues, concerning computational complexity and modeling aspects, which is tackled in this thesis.

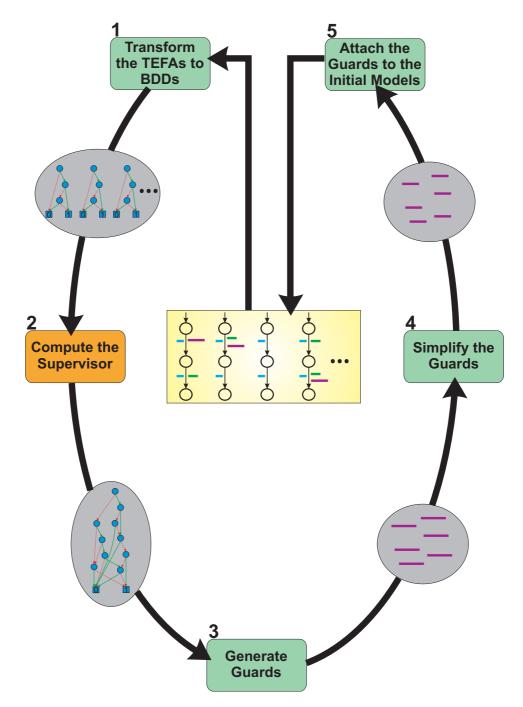

We model DES by *extended finite automata* (*EFAs*), state transition models that contain discrete-valued variables. TDES are modeled by an augmentation of EFAs, called *timed EFAs* (*TEFAs*), which contain a set of discrete-valued clocks. Based on EFAs or TEFAs, the supervisor can be *symbolically* computed, using *binary decision diagrams* (*BDDs*), data structures that could, in many cases, lead to smaller representation of the state space. For complex systems, the computed supervisor may consist of many states, causing representation and implementation difficulties. To tackle this, based on the states of the supervisor, we symbolically compute logical constraints that will be attached to the original models to restrict the system's behavior. Consequently, we present a framework, where given a set of EFAs or TEFAs, the supervisor is computed using BDDs, and represented in a modular manner based on the computed logical constraints. The framework has been developed, implemented, and applied to industrial case studies.

**Keywords:** Timed Discrete Event Systems, Supervisory Control Theory, Extended Finite Automata, Binary Decision Diagrams.

## Acknowledgments

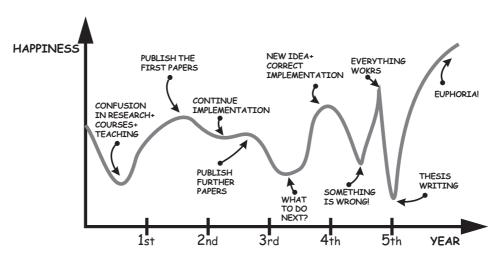

You start your PhD studies with the dream of making a major impact on the science! But soon you realize the reality is something different. More than contributing to the science, doing a PhD is about to learn how to 'think' in a structural and analytical manner. It is about to understand why you got correct results before getting happy, and why you got wrong results after becoming sad. Finally, it is about to write and formulate your results in a 'convincible' way, while meeting the 'deadlines'. And during this journey, you indeed realize the power of procrastination! As a result, in five years, you deal with more or less happy moments, which can be summarized as below:

I would therefore like to thank the people that let me share my 'peak' moments with them, and cheered me up during the 'troughs'. Initially, I want to thank my never-tiring supervisor Prof. Bengt Lennartson for supporting me in different aspects; and as the head of our research group, for treating it as his second family. And my co-supervisor Dr. Knut Åkesson for all the lively and fruitful discussions, which positively changed my way of thinking. I also would like to thank Prof. Martin "The Man in Black" Fabian for always being available for all kind of questions. All of my colleagues at the division of Automatic Control, Automation and Mechatronics really deserve a word of appreciation. Thank you guys, you are wonderful. A special appreciation goes to Zhennan "The Dude" Fei, for all the enjoyable discussions we had together and the unforgettable time

ACKNOWLEDGMENTS IV

we had in USA. Talking about USA, I would like to thank Prof. Spyros Reveliotis for giving us the opportunity to visit Georgia Tech. and experiencing the research environment at such a good university. Also, a special thank goes the administrative and technical staff at the department for always being so helpful and making everything work smoothly.

Finally, I would like to thank the family of Prof. Dadfar for their never-ending support, from the beginning of my studies in Sweden. My deepest gratitude goes to my family and friends, whom have always encouraged me and believed in me, especially, my parents and my brothers.

Sajed Miremadi

Gothenburg, November 2012

This work was carried out within the Wingquist Laboratory VINN Excellence Centre at Chalmers University of Technology and was also supported by Swedish Foundation for Strategic Research through the ProViking program.

## **Publications**

This thesis is based on the following papers, included in full in Part II:

- [Paper 1] S. Miremadi, K. Åkesson and B. Lennartson. Symbolic computation of reduced guards in supervisory control. *IEEE Transactions on Automation Science and Engineering*, vol. 8, no. 4, pp. 754-765, October 2011.

- [Paper 2] S. Miremadi, B. Lennartson and K. Åkesson. A BDD-based approach for modeling plant and supervisor by extended finite automata. *IEEE Transactions on Control Systems Technology*, vol. 20, no. 6, pp. 1421-1435, November 2012.

- [Paper 3] S. Miremadi, Z. Fei, K. Åkesson and B. Lennartson. Symbolic representation and computation of timed discrete event systems. Submitted to *IEEE Transactions on Automation Science and Engineering*, 2012.

- [Paper 4] S. Miremadi, Z. Fei, K. Åkesson and B. Lennartson. Symbolic supervisory control of timed discrete event systems. Submitted to *IEEE Transactions on Control Systems Technology*, 2012.

The following papers are relevant to this work but not included in the thesis:

- [1] S. Miremadi, Z. Fei, K. Åkesson and B. Lennartson. Symbolic computation of nonblocking control function for timed discrete event systems. To be published in *Proceedings of the* 8<sup>th</sup> *IEEE International Conference on Automation Science and Engineering*, December 2012.

- [2] S. Miremadi and A. Voronov. Symbolic reduction of guards in supervisory control using genetic algorithms. Chalmers University of Technology, Gothenburg, Sweden, *Technical Report*, August 2012, p. 7.

- [3] S. Miremadi, B. Lennartson and K. Åkesson. BDD-based supervisory control on extended finite automata. In *Proceedings of the 7<sup>th</sup> IEEE International Conference on Automation Science and Engineering*, August 2011, pp. 25-31.

PUBLICATIONS VI

[4] S. Miremadi, K. Åkesson and B. Lennartson. Extraction and representation of a supervisor Using guards in extended finite automata. In *Proceedings of the* 9<sup>th</sup> *International Workshop on Discrete Event Systems*, May 2008, pp. 193-199.

- [5] S. Miremadi, K. Åkesson, M. Fabian, A. Vahidi and B. Lennartson. Solving two supervisory control benchmark problems using Supremica. In *Proceedings of the* 9<sup>th</sup> *International Workshop on Discrete Event Systems*, May 2008, pp. 131-136.

- [6] Z. Fei, S. Miremadi, K. Åkesson and B. Lennartson. Efficient Supervisory Synthesis for Extended Finite Automata. Submitted to *IEEE Transactions on Control Systems Technology*, 2012.

- [7] Z. Fei, S. Miremadi, K. Åkesson and B. Lennartson. Efficient supervisory synthesis to large-scale discrete event systems modeled as extended finite automata. In *Proceedings of the* 8<sup>th</sup> *IEEE International Conference on Automation Science and Engineering*, August 2012.

- [8] Z. Fei, S. Miremadi, K. Åkesson and B. Lennartson. Modeling sequential resource allocation systems using extended finite automata. In *Proceedings of the* 7<sup>th</sup> *IEEE International Conference on Automation Science and Engineering*, August 2011, pp. 444-449.

- [9] Z. Fei, S. Miremadi, K. Åkesson and B. Lennartson. Efficient symbolic supervisory synthesis and guard generation: Evaluating partitioning techniques for the state-space exploration. In *Proceedings of the* 3<sup>rd</sup> *International Conference on Agents and Artificial Intelligence*, January 2011, pp. 106-115.

- [10] B. Lennartson, S. Miremadi, Z. Fei, M. Noori, M. Fabian and K. Åkesson. State-Vector Transition Model Applied to Supervisory Control. In *Proceedings of the* 17<sup>th</sup> *IEEE International Conference on Emerging Technologies and Factory Automation*, September 2012.

- [11] M. Fabian, S. Miremadi, Z. Fei and K. Åkesson. Supervisory control of manufacturing systems using extended finite automata. To be published in *Formal Methods in Manufacturing* (Series on Industrial Information Technology), J. Campos, C. Seatzu and X. Xie, CRC Press/Taylor and Francis, 2013, ch. 10.

- [12] M. R. Shoaei, S. Miremadi, K. Bengtsson and B. Lennartson. Reduced-order synthesis of operation sequences. In *Proceedings of the* 16<sup>th</sup> *IEEE International Conference on Emerging Technologies and Factory Automation*, September 2011, pp. 1-8.

- [13] M. R. Shoaei, B. Lennartson and S. Miremadi. Automatic generation of controllers for collision-free flexible manufacturing systems. In *Proceedings of the* 6<sup>th</sup> *IEEE Conference on Automation Science and Engineering*, August 2010, pp. 368-373.

- [14] K. Bengtsson, P. Bergagård, C. Thorstensson, B. Lennartson, K. Åkesson, C. Yuan, S. Miremadi and P. Falkman. Sequence planning using multiple and coordinated sequences of operations. *IEEE Transactions on Automation Science and Engineering*, vol. 9, no. 2, pp. 308-319, April 2012.

- [15] K. Bengtsson, C. Thorstensson, B. Lennartson, K. Åkesson, C. Yuan, S. Miremadi and P. Falkman. Relations identification and visualization for sequence planning and automation design. In *Proceedings of the* 6<sup>th</sup> *IEEE Conference on Automation Science and Engineering*, August 2010, pp. 841-848.

## **Contents**

| Al | bstrac | et                                          | i    |

|----|--------|---------------------------------------------|------|

| A  | cknov  | vledgments                                  | iii  |

| Pι | ıblica | tions                                       | v    |

| Co | onten  | ts                                          | ix   |

| Li | st of  | Acronyms                                    | xiii |

| Ι  | Int    | roductory Chapters                          | 1    |

| 1  | Intr   | oduction                                    | 3    |

|    | 1.1    | Discrete Event Systems                      | 3    |

|    | 1.2    | Verification                                | 4    |

|    | 1.3    | Supervisory Control Theory                  | 5    |

|    | 1.4    | Challenges                                  | 6    |

|    |        | 1.4.1 Supervisor Representation             | 6    |

|    |        | 1.4.2 Qualitative and Quantitative Analysis | 6    |

|    |        | 1.4.3 Computational Complexity              | 6    |

|    | 1.5    | Contributions                               | 7    |

|    | 1.6    | Outline                                     | 8    |

| 2  | Mod    | leling Formalisms                           | 9    |

|    | 2.1    | Finite Automata                             | 9    |

|    | 2.2    | Timed Extended Finite Automata              | 14   |

|    | 2.3    | Related Work                                | 21   |

| 3  | Sup    | ervisory Control Theory                     | 23   |

|    | 3.1    | SCT of Untimed DES                          | 24   |

|    |        | 3.1.1 DES Modeled by EFAs                   | 27   |

|    | 3.2    | SCT of Timed DES                            | 28   |

|    |        | 3.2.1 Transformation of TEFAs to EFAs       | 29   |

<u>CONTENTS</u> x

|    |       | 3.2.2 Controllability of TDES                         | 30  |

|----|-------|-------------------------------------------------------|-----|

|    | 3.3   | Synthesis                                             | 33  |

|    |       | 3.3.1 Untimed DES                                     | 33  |

|    |       | 3.3.2 Timed DES                                       | 36  |

|    | 3.4   | Supervisor Representation                             | 40  |

|    |       | 3.4.1 Representing the Supervisor as Guards           | 41  |

|    | 3.5   | Related Work                                          | 48  |

| 4  | Sym   | abolic Representation and Computation                 | 49  |

|    | 4.1   | Basics                                                | 50  |

|    |       | 4.1.1 Characteristic Function                         | 51  |

|    | 4.2   | Representation of Models                              | 52  |

|    |       | 4.2.1 Representation of DFAs                          | 52  |

|    |       | 4.2.2 Representation of TEFAs                         | 53  |

|    | 4.3   | Symbolic Synthesis                                    | 57  |

|    |       | 4.3.1 Size of Intermediate BDDs                       | 60  |

|    | 4.4   | Symbolic Guard Generation                             | 61  |

|    |       | 4.4.1 Symbolic Computation of the Basic State Sets    | 61  |

|    |       | 4.4.2 IDD Generation                                  | 62  |

|    |       | 4.4.3 Guard Generation                                | 63  |

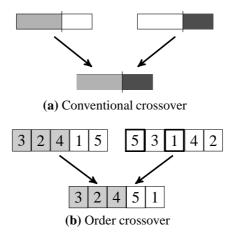

|    |       | 4.4.4 Guard Reduction by Genetic Algorithms           | 63  |

|    | 4.5   | Related Work                                          | 65  |

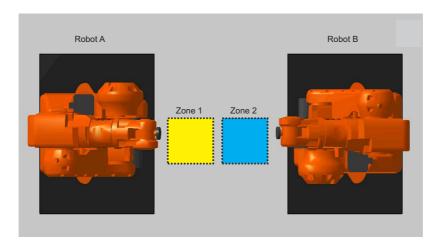

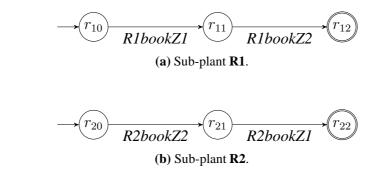

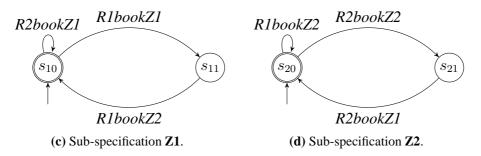

| 5  | Case  | e Studies                                             | 67  |

|    | 5.1   | Illustrative Example                                  | 67  |

|    | 5.2   | Industrial Case Study                                 | 72  |

|    | 5.3   | Implementation Remarks                                | 79  |

| 6  | Sum   | nmary of Appended Papers                              | 81  |

| 7  | Con   | clusions and Future Research                          | 83  |

| Bi | bliog | raphy                                                 | 87  |

|    |       |                                                       |     |

| II | A     | opended Papers                                        | 95  |

| Pa | per 1 | Symbolic Computation of Reduced Guards in Supervisory |     |

|    | Con   | trol                                                  | 100 |

|    | 1     | Introduction                                          | 100 |

|    | 2     |                                                       | 102 |

|    |       |                                                       | 102 |

|    |       |                                                       | 103 |

|    | 3     | Supervisor as Guards                                  | 104 |

XI CONTENTS

|         | 3.1        | Basic State Sets                                       | 105               |

|---------|------------|--------------------------------------------------------|-------------------|

|         | 3.2        | Guards                                                 | 107               |

| 4       | BDD F      | Representation                                         | 109               |

| 5       | From F     | BDDs to Guards                                         | 111               |

|         | 5.1        | BDD Computation                                        | 112               |

|         | 5.2        | IDD Generation                                         | 113               |

|         | 5.3        | Heuristic Minimization Techniques                      | 116               |

|         | 5.4        | Guard Generation                                       | 117               |

| 6       | From C     | Guards to EFA                                          | 118               |

| 7       | Case S     | tudy - Car Manufacturing Cell                          | 120               |

| 8       | Conclu     | sions and Future Works                                 | 124               |

| Refe    | rences.    |                                                        | 125               |

| D 4     | 4 DE       |                                                        |                   |

| Paper 2 |            | OD-based Approach for Modeling Plant and Supervisor    |                   |

| . •     |            | d Finite Automata                                      | 132               |

| 1 2     |            | action                                                 | 132<br>135        |

| 2       | 2.1        | inaries                                                | 135               |

|         | 2.1        | Extended Finite Automata                               | 139               |

| 2       |            | Binary Decision Diagrams                               | 139               |

| 3<br>4  |            | isory Control Theory                                   | $\frac{140}{141}$ |

| 4       | -          | blic Computation of $S_0$                              | 141               |

|         | 4.1        | BDD representation of an EFA                           | 142               |

| _       | 4.2        | BDD representation of EFSC on EFAs                     | _                 |

| 5       | Kepres 5.1 | entation of the Supervisor as EFAs                     | 153               |

|         |            | Guard Attackment                                       | 154               |

| 6       | 5.2        | Guard Attachment                                       | 155               |

| 6       |            | tudies                                                 | 156               |

|         | 6.1<br>6.2 | Model classification                                   | 156<br>158        |

|         | 6.3        | Benchmark examples                                     | 160               |

| 7       |            | Results                                                |                   |

|         |            | isions                                                 |                   |

| Kele    | rences.    |                                                        | 102               |

| Paper 3 | Symb       | oolic Representation and Computation of Timed Discrete | e                 |

| Ever    | nt Syste   | ms                                                     | <b>17</b> 0       |

| 1       | Introdu    | action                                                 | 170               |

| 2       | Timed      | Extended Finite Automata                               | 172               |

|         | 2.1        | Syntax and Semantics                                   | 172               |

|         | 2.2        | Extended Full Synchronous Composition                  | 176               |

| 3       | Superv     | isory Control Theory                                   | 178               |

| 4       | EFA se     | emantics of TEFA                                       | 179               |

| 5       | Symbo      | lic Representations and Computations                   | 181               |

|         | 5.1        | Abstraction of Tick-EFAs                               | 182               |

<u>CONTENTS</u> XII

|         | 5.2 BDD Representation of $\rightarrowtail_{S_0}$         | 184 |

|---------|-----------------------------------------------------------|-----|

| 6       | Case Study: A Production Cell                             |     |

| 7       | Conclusions and Future Works                              | 195 |

| Refe    | rences                                                    | 196 |

| Paper 4 | Symbolic Supervisory Control of Timed Discrete Event Sys- |     |

| tems    |                                                           | 204 |

| 1       | Introduction                                              | 204 |

| 2       | Preliminaries                                             | 205 |

|         | 2.1 Timed Extended Finite Automata                        | 206 |

|         | 2.2 Supervisory Control Theory                            | 210 |

| 3       | Supervisory Synthesis of TDES                             |     |

| 4       | Symbolic Representation and Computation                   |     |

|         | 4.1 Basics                                                |     |

|         | 4.2 BDD representation                                    |     |

|         | 4.3 Synthesis                                             |     |

| 5       | Industrial Case Study                                     |     |

| 6       | Conclusions and Future Work                               |     |

| Refe    | rences                                                    |     |

## **List of Acronyms**

BDD - Binary Decision Diagrams

CF - Characteristic Function

CS – Complement State

DES - Discrete Event System

DFA – Deterministic Finite Automaton

EFA – Extended Finite Automaton

EFSC – Extended Full Synchronous Composition

FA – Finite Automaton

FSC - Full Synchronous Composition

GA – Genetic Algorithms IS – Independent State

PCG – Process Communication Graph SCT – Supervisory Control Theory STS – State Transition System

TA – Timed Automaton

TDES – Timed Discrete Event SystemsTEFA – Timed Extended Finite Automaton

TGA - Timed Game Automaton

# Part I Introductory Chapters

## Chapter 1

## Introduction

As we progress in time, the dependence and inseparability of our daily lives to hardware and software systems grow rapidly. For instance, modern cars, mobile phones, medical devices, communication systems, audio and video systems, control systems, etc. contain various types of software.

#### 1.1 Discrete Event Systems

Historically, the systems that have been studied over the years involve quantities such as pressure, temperature, speed, and acceleration, which are continuous variables, evolving over time. Such systems have continuous states and are time-driven, i.e., a state changes as time changes. Since we can naturally define derivatives for continuous variables, modeling and analysis of such systems heavily rely on the theory and techniques related to differential and difference equations.

Nevertheless, not all system behaviors can be meaningfully represented by continuous variables and mathematical expressions. Most of the computer systems that we deal with include *discrete* properties. They are discrete in the sense that they are typically related to counting integer numbers such as the number of vehicles in a transportation system, number of faults in a system, or number of robots in a manufacturing cell. An interesting point about such systems is that most of them are driven by instantaneous *events* such as "start of a machine' or "a traffic light turning green". When an event occurs, the system transits from one *state* to another state, e.g., "the traffic light turns from amber to green". A system which its state evolution depends entirely on the occurrence of asynchronous events over time is called a *discrete event system* (DES)<sup>1</sup>, which is the scope of this thesis. Many systems are profitably modeled by DES such as manufacturing systems, operative systems, communication protocols and telephony systems.

<sup>&</sup>lt;sup>1</sup>In the thesis, for ease of reading, "DES" is also used in plural form, i.e., "discrete event systems".

In DES, merely the sequence of the visited states, i.e., the sequence that the events occur, is used to analyze different systems. In other words, the logical or the *qualitative* behavior of a system is in focus. For instance, in a manufacturing system a qualitative property could be "robot 1 should always complete its task before robot 2" or in a communication system "two users should not use a channel simultaneously". Nevertheless, the correct behavior of many real-time systems such as air traffic control systems and networked multimedia systems depends on the **delays** between events. In addition, in many cases, we also want to analyze the *quantitative* properties of the systems. For instance, in a manufacturing system we can check a property "if robot 1 does not finish its task in 20 seconds, let robot 2 finish its task" or in a communication system "if a channel is booked by a user for more than 1 minute, prohibit the user to use the channel and let another one use it". A DES that also considers the time points the events occur, is referred to as *timed DES (TDES)*. In this thesis, we analyze both DES and TDES.

With the increasing complexity of computer systems, it is crucial to have efficient design of correct and well-functioning hardware and software systems. Systems that do not work as expected can both lead to costly mistakes and disastrous consequences. In the early nineties, a bug was detected in Intel's Pentium II floating division unit, which caused the company a loss of about \$475 million to replace faulty processors [1]. In 1997, the Mars Pathfinder landed on Mars, however, the spacecraft contained a design flaw that once in a while resulted in system resets and loss of important data [2]. Between 1985 and 1987, an error in the control part of the radiation therapy machine Therac-25 led to an overdose of radiation, which caused the death of six cancer patients [3]. All of these programs included *design* errors that were not captured during the design or implementation phases. Hence, somehow we need to ensure that the programs are correct or error-free, before putting them into practice.

#### 1.2 Verification

As different systems are continuously used in larger contexts and in interaction with other components, they become more vulnerable to errors. It is known that the number of errors grows exponentially with the number of interacting system components. Thus, checking the correctness of complex systems with standard and conventional techniques such as random simulation or directed test are not always possible; especially, with the high demands on the system development time. Today, *formal verification* is mostly used for this purpose, that is mathematically-based techniques for proving or disproving the correctness of a property in a system [4, 5]. Investigations show that the design errors which were exposed in the aforementioned applications had been revealed if formal verification had been utilized. In formal verification, initially, the desired property

to be verified is identified. Then, an abstract model of the system including the surrounding environment is built. Finally, the parts of the system that are interesting w.r.t the property are identified, and it is mathematically shown whether the property holds in the region of interest. Hence, the final result after verifying a system could be either *yes*, i.e., the system satisfies the given property, or *no*, i.e., the system does not satisfy the given property. Consequently, the goal is to design a *control function* that that restricts the system's behavior towards all the given desired properties.

#### 1.3 Supervisory Control Theory

Basically, there are two conceivable ways of designing a control function: manually based on verification or automatically based on synthesis. In the verification method a control function candidate is designed manually in a fashion that supposedly controls the system in an appropriate manner. This is then verified towards some desired properties and if the result is satisfactory the control function design is finished. Preferably, the verification should give a hint about problems with the current control function so that the designer will have a better understanding of what needs to be changed. The verification method could be useful for applications, where changes are not applied frequently, e.g., microcontrollers. However, for applications, where the control function needs to be modified frequently due to changes to the system, the verification method could be quite time consuming. For instance, in a car manufacturing system, each time a new model is going to be produced, since much of the work is done on-line on the shop-floor, the production is down during the control function implementation. There are different tools such as UPPAAL [6] and KRONOS [7] that are based on the described verification procedure.

In the synthesis method, the above process is automated. Based on the specifications of the desired system behavior, synthesis generates a control function that makes sure the system does not violate the specifications. Naturally, synthesis can be carried out in different ways. For instance, it is possible to synthesize a control function that restricts the system more than necessary, which is typically not desired. In 1987, Ramadge and Wonham proposed a conceptual framework called *supervisory control theory (SCT)* for DES [8]. They showed that given a system, referred to as the *plant* and some desired properties, referred to as the *specifications*, there exists a control function, referred to as the *supervisor*, which is *minimally restrictive*. The supervisor is minimally restrictive in the sense that it restricts the plant only when it is necessary without violating the specifications. They also proposed a method to automatically synthesize such a supervisor. SCT has been applied to different domains such as manufacturing systems [9, 10], vehicular traffic [11], logistics [12], and communication networks [13, 14]. There are different tools such as Supremica [15] and TCT [16] that are based on the

SCT for generating control functions. In this thesis, we aim to compute control functions for DES and TDES, based on the SCT. Despite many benefits that can be gained by utilizing SCT, still, the control functions are mostly designed manually in the industry.

#### 1.4 Challenges

In the following, we discuss some of the existing challenges in the SCT.

#### 1.4.1 Supervisor Representation

The SCT is based on state-transition models; but industrial people are used to other representations such as sequential function charts (SFCs), ladder diagrams, Gantt charts, and PERT charts, that are exploited to represent the control functions. Specifically, the interpretation of a control function represented by a large and cluttered state-transition model requires the maintenance personnel to have other skills than are common today.

#### 1.4.2 Qualitative and Quantitative Analysis

Conventional SCT is not defined for TDES. To this end, researchers proposed different approaches to, based on the SCT, perform *qualitative* analysis on TDES [17–20]. Most of these approaches are based on discrete time. There also exists many models and implementations that are suitable for *quantitative* analysis, most of them based on continuous time [21–25]; yet there are few works considering both the qualitative and quantitative aspects of TDES.

#### 1.4.3 Computational Complexity

The complexity of a system represented by a state-transition model is often measured by its number of states, referred to as *state space*. The state space of a system grows exponentially by the addition of new components to the system. Since most of the industrial systems consist of many components, they include a huge state space, sometimes  $10^{100}$  states or even more. Obviously, representing and enumerating such state spaces *explicitly* is more or less impossible both in terms of time and memory. To tackle this problem, the state space can be represented *symbolically (implicitly)*, which in many cases results in a smaller representation of the state space. Symbolic representation implies that the state space is described by means of logic constraints and special data structures, which makes it possible to simultaneously perform operations on a set of states, rather than a single state. One such powerful data structure is called *binary decision diagram (BDD)* that is used to symbolically represent Boolean functions [26]. It has been

7 1.5. Contributions

shown that BDD-based algorithms can improve the efficiency of computing control functions dramatically. For instance, in [27] the supervisor of a system with more than  $10^{200}$  states was computed in a few minutes. However, in many cases it is quite complicated to represent models by BDDs and perform all the computations **purely** on these data structures, especially, with the introduction of time.

#### 1.5 Contributions

The aforementioned challenges have been tackled in this thesis, which has lead to the following contributions:

- C1: Symbolic representation of *extended finite automata (EFAs)*, finite automata extended with discrete variables, and their full synchronous composition operator, based on BDDs.

- C2: Symbolic representation of *timed extended finite automata (TEFAs)*, EFAs extended with discrete-values clocks, and their full synchronous composition operator, based on BDDs. This contribution mainly considers the symbolic representation of time without including *tick* events.

- C3: Symbolic computation of the supervisor of TDES, modeled by TEFAs, based on BDDs.

- C4: Identification of a subset of the states belonging to the supervisor as the *basic state sets*. Based on the basic state sets, some logical conditions, referred to as *guards*, are automatically generated. The guards express under which conditions an event is allowed to occur to fulfill the specifications.

- C5: Symbolic computation of the basic state sets, using BDDs; and simplification of the guards, by utilizing the structure of the model and applying different heuristic techniques.

- C6: Representation of a *modular* supervisor for a system that is modeled by TEFAs. The supervisor is modular in the sense that it is represented by the original TEFAs restricted by the computed guards.

- C7: All algorithms are developed, implemented, and verified in Supremica [15, 28–30], a software tool for automatic verification, synthesis and simulation of DES.

In Table 1.1, the relationship between the main contributions and each of the mentioned challenges, i.e., supervisor representation (SR), qualitative and quantitative analysis (QQA), and computational complexity (CC), is illustrated. Further, the table shows in which appended papers the challenges are addressed and the contributions are presented.

**Table 1.1:** Illustration of the relationships: challenges – main contributions – appended papers.

|              |    | Challenge |         |           |  |

|--------------|----|-----------|---------|-----------|--|

|              |    | SR        | QQA     | CC        |  |

| Contribution | C1 |           |         | Paper 2   |  |

|              | C2 |           | Paper 3 | Paper 3   |  |

|              | C3 |           | Paper 4 | Paper 4   |  |

|              | C4 | Paper 1   |         |           |  |

|              | C5 | Paper 1   |         | Paper 1   |  |

|              | C6 | Paper 2   |         |           |  |

|              | C7 |           |         | Paper 1-4 |  |

#### 1.6 Outline

The thesis is divided in two parts. Part I provides introductory chapters that present background and context of the appended papers in Part II. The papers in Part II constitute the base of this thesis. A list of references is included at the end of Part I and at the end of each paper presented in Part II. All the proofs of the propositions, lemmas, and theorems in Part I are included in the appended papers in Part II.

Chapter 2 describes the modeling formalisms, deterministic finite automata and timed extended finite automata, which we used to model the systems. In Chapter 3, the supervisory control theory of both untimed discrete event systems and their timed extension are explained. Chapter 4 gives an overview of the symbolic data structures, i.e., binary decision diagrams, that are used to perform the analysis. Chapter 5 includes an illustrative and an industrial case study. A summary of the scientific papers, appended in Part II, is provided in Chapter 6. Finally, Part I is concluded in Chapter 7.

## Chapter 2

## **Modeling Formalisms**

When it comes to analysis and control of discrete event systems (DES), using appropriate modeling formalisms for representing the system's behavior is a dilemma. The appropriate choice highly depends on the objectives of the analysis. There are various modeling formalisms used to model DES such as finite automata [31, 32], Petri nets [33], process algebra [34, 35] and logic-based models [36].

Since automata are intuitive, easy to use, suitable for analysis and applicable to composition operations, they are used quite often for modeling, compared to other formalisms. In this work, automata are used to model DES. The main reason for this choice, is that automata conform well with supervisory control theory (discussed in Chapter 3), as they were used originally in [8]. In addition, to improve the expressiveness and compactness of the models, we use an extended variant of ordinary automata, where discrete-value variables and clocks are introduced to the model. In this work, we are interested in deterministic systems, and thus all models that are used in this work are considered to be deterministic.

**Remark** (SOS-notation). A notation that will be used frequently is the *SOS-notation* (Structured Operational Semantics) [37]. The notation  $\frac{\text{premise}}{\text{conclusion}}$  should be read as follows: if the proposition above the "solid line" (premise) holds, then the proposition under the fraction bar (conclusion) holds as well.

#### 2.1 Finite Automata

A finite automaton (FA) is a state transition system or a state machine, formally defined as below.

#### **Definition 2.1** Finite Automaton

A finite automaton (FA) is a 4-tuple  $(Q, \Sigma, \mapsto, Q^0)$  where

- Q is a finite set of states;

- $\Sigma$  is a nonempty finite set of events;

- $\mapsto \subseteq : Q \times \Sigma \times Q$  is a transition relation; and

- $Q^0 \subseteq Q$  is a set of initial states.

The set of events  $\Sigma$  is sometimes referred to as the *alphabet* of the automaton. The notation |Q| denotes the number of states of the automaton. For an event  $\sigma$ , a *source-state* q and a *target-state*  $\acute{q}$ , a transition  $(q,\sigma,\acute{q}) \in \mapsto$  is written  $q \stackrel{\sigma}{\mapsto} \acute{q}$ , which means that by the occurrence of  $\sigma$ , the system evolves from q to  $\acute{q}$ . A state q is said to be *reachable* if the automaton can evolve into q by a number of event executions, starting with an initial state.

#### **Definition 2.2** Deterministic Finite Automaton (DFA)

An FA  $(Q, \Sigma, \mapsto, Q^0)$  is deterministic if there only exists a single initial state, i.e.,  $Q^0 = \{q^0\}$ ; and

$$\forall q \in Q: \frac{q \stackrel{\sigma}{\mapsto} \acute{q} \land q \stackrel{\sigma}{\mapsto} \grave{q}}{\acute{q} = \grave{q}}.$$

Informally, by executing an event at any state of a DFA, the next state can be determined. Hence, in a DFA, the transition relation will be a *function*. In the sequel, where ever we mention "automaton", we refer to deterministic automaton.

For an automaton A, we use  $\Gamma_A(q)$  to denote all the events in A that are enabled from state q. Formally,  $\Gamma_A(q) = \{ \sigma \in \Sigma \mid \exists \acute{q} \in Q_A : (q,\sigma,\acute{q}) \in \mapsto_A \}$ . We also use the notation  $Q_A^{\sigma}$  to represent all the states in A, where event  $\sigma$  is enabled, i.e.,  $Q_A^{\sigma} = \{ q \in Q_A | \sigma \in \Gamma_A(q) \}$ .

It is often easier to model complex systems *modularly*, in a structured way, by a number of automata. The global behavior of a modular model can be represented by composing the automata. The composition of two automata is defined by the *full synchronous composition* (*FSC*) operator  $\parallel$  [38]. In FSC, the shared events must be executed by all automata synchronously, while other events are executed independently.

#### **Definition 2.3** Full Synchronous Composition (FSC)

For k=1,2, consider two DFAs  $A_k=(Q_k,\Sigma_k,\mapsto_k,\{q_k^0\})$ . The full synchronous composition (FSC) of  $A_1$  and  $A_2$ , denoted by  $A_1\|A_2$ , is an automaton  $A=(Q,\Sigma,\mapsto,\{q^0\})$ , where

- $-Q = Q_1 \times Q_2$

- $\Sigma = \Sigma_1 \cup \Sigma_2$

- the transition relation  $\mapsto \subseteq Q \times \Sigma \times Q$  is defined based on the following rules:

$$(a) \ \sigma \in \Sigma_{1} \cap \Sigma_{2}:$$

$$\frac{(q_{1}, \sigma, \acute{q}_{1}) \in \mapsto_{1} \ \land \ (q_{2}, \sigma, \acute{q}_{2}) \in \mapsto_{2}}{((q_{1}, q_{2}), \sigma, (\acute{q}_{1}, \acute{q}_{2})) \in \mapsto},$$

$$(b) \ \sigma \in \Sigma_{1} \backslash \Sigma_{2}:$$

$$\frac{(q_{1}, \sigma, \acute{q}_{1}) \in \mapsto_{1} \ \land \ q_{2} \in Q_{2}}{((q_{1}, q_{2}), \sigma, (\acute{q}_{1}, q_{2})) \in \mapsto},$$

$$(c) \ \sigma \in \Sigma_{2} \backslash \Sigma_{1}:$$

$$\frac{(q_{2}, \sigma, \acute{q}_{2}) \in \mapsto_{2} \ \land \ q_{1} \in Q_{1}}{((q_{1}, q_{2}), (q_{1}, \acute{q}_{2})) \in \mapsto},$$

In the above definition,  $\Sigma_1 \backslash \Sigma_2$  denotes the set operation relative complement, indicating all the events that are included in  $\Sigma_1$  but are not included in  $\Sigma_2$ . FSC can indeed be extended to multiple automata [38]. After the composition, the size of  $A_1 \parallel A_2$ , in the worst case, is the product of the sizes of  $A_1$  and  $A_2$ . For the most, not all of these states are reachable—the size of  $A_1 \parallel A_2$  can even be smaller than both  $A_1$  and  $A_2$ —but the **growth** of the state-space can be considerable. This effect is particularly prominent when many automata are composed, in which the size of the state-space easily becomes unmanageable, a problem commonly referred to as the state space explosion problem. This is the problem that is tackled by representing the automata symbolically using binary decision diagrams, discussed in Chapter 4.

To show how a system can be modeled by FAs, let us take a look at an example, which is an extended version of the railroad example in [39].

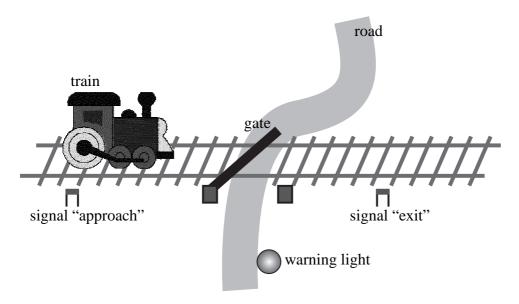

#### EXAMPLE 2.1 Railroad Crossing

$q^0 = (q_1^0, q_2^0).$

Consider a one-way railroad that crosses a one-way road, shown in Figure 2.1. It is desired to develop a control system that closes the gate when it receives a signal indicating that a train is approaching, and opens the gate when it receives a signal indicating that it has crossed the road and no other train has approached the crossing again. Furthermore, there exists a warning light on the road that has a reasonable distance to the crossing, indicating that a train is crossing the road to warn the drivers to slow down. The control system should only switch the light when the gate is closed and switch it off when the gate is opened. This

**Figure 2.1:** Railroad crossing example.

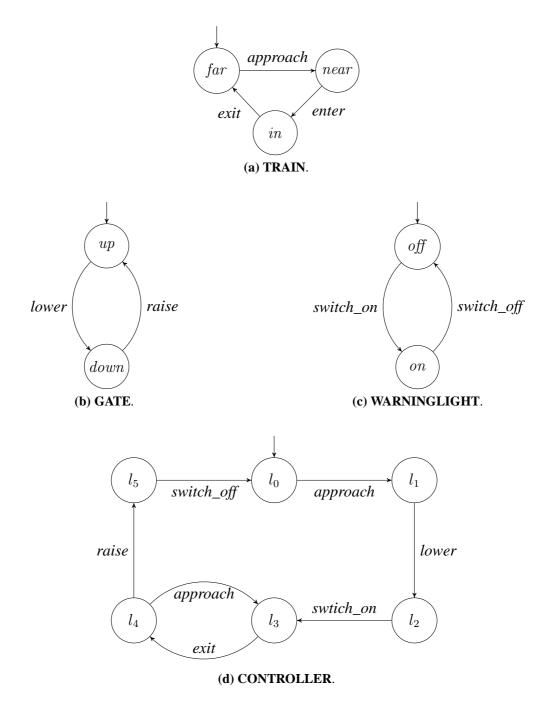

system can be modeled by four DFAs

```

\mathbf{TRAIN} = (\{far, near, in\}, \{approach, enter, exit\}, \mapsto_1, \{far\}),

\mathbf{GATE} = (\{up, down\}, \{lower, raise\}, \mapsto_2, \{up\}),

\mathbf{WARNINGLIGHT} = (\{off, on\}, \{switch\_off, switch\_on\}, \mapsto_3, \{off\}),

\mathbf{CONTROLLER} = (\{l_0, \dots, l_5\}, \{approach, lower, switch\_off, \\ switch\_on, exit, raise\}, \mapsto_4, \{0\}),

```

where their corresponding transition relations are depicted in Figure 2.2.

The states of the DFA representing the train (Figure 2.2a) have the following intuitive meaning: in state far the train is not close to the crossing, in state near it is approaching the crossing and has just sent a signal to notify this, and in state in it is at the crossing. The states of **GATE** and **WARNINGLIGHT** have the obvious interpretation. The DFA **CONTROLLER** (Figure 2.2d) will evolve from state  $l_0$  to  $l_1$  when the event approach occurs. At state  $l_1$ , the controller closes the gate by sending the signal lower to the gate, ending up in state  $l_2$ , and turns the warning light on by sending the signal  $switch\_on$  to the warning light, ending up in state  $l_3$ . When the event exit occurs, the train has left the crossing, ending up in state  $l_4$ . If at this moment, another train approaches the crossing, the controller will not open the gate and will evolve to state  $l_3$ ; otherwise it opens the gate by sending the signal  $exitch\_off$ .

The global behavior of the system can be observed by synchronizing the automata: **TRAIN**||**GATE**||**WARNINGLIGHT**||**CONTROLLER**. By considering the following two transitions in the synchronized DFA, it can be revealed

**Figure 2.2:** DFAs modeling the railroad crossing example.

that the system suffers from a design flaw:

$$((far, up, off, l_0), approach, (near, up, off, l_1))$$

and  $((near, up, off, l_1), enter, (in, up, off, l_1)).$

"At state  $(in, up, off, l_1)$  the gate is about to close (by executing the event *lower*), while the train is (already) at the crossing, which can cause collision. In fact, the basic concept of the design is correct if and only if closing the gate does not take more time than the train needs to get to the crossing once it sends the signal *approach*" [39]. Such real-time constraints cannot be formulated by DFAs and will be the main motivation of introducing timed extended finite automata.

#### 2.2 Timed Extended Finite Automata

In some cases, modeling complex systems with DFAs can lead to incompact and intractable models for the users. One way to obtain more compact models is by introducing variables to the model. Naturally, physical signals that are stored in memories or sent between controllers can be modeled as global variables. For instance, a convenient way to model sensors and actuators is by using variables. Also, systems that have a buffer-resembling behavior can be easily modeled by variables. To this end, a new modeling formalism called *Extended Finite Automaton (EFA)*, was presented in [40]. An EFA is an augmentation of an FA with a finite set of discrete-valued variables. The variables appear in the transitions of the automata as either logical conditions, called *guards*, or updating function, called *actions*. A transition in an EFA is enabled if and only if its corresponding guard formula is satisfied; and when a transition is taken it may be followed by updates of variables defined by the associated actions. We model DES by using EFAs.

However, in order to model TDES, EFAs are not complete models to represent timing properties. To this end, we introduce *timed extended finite automaton* (*TEFA*), which is an EFA, augmented with a finite set of discrete-valued clocks. Intuitively, a *clock* in a TEFA is a discrete variable in the sense of EFAs, restricted by some rules, mentioned later. The time implicitly elapses only at locations, whereas the transitions occur instantaneously with zero delay. It is worth to mention that by disregarding the clocks from TEFAs, the remaining formal discussions on TEFAs are equivalent to EFAs, and thus, in the following, we only discuss TEFAs.

#### **Definition 2.4** Timed Extended Finite Automaton

A timed extended finite automaton is a 10-tuple

$$TE = (L, D^{\mathcal{V}}, \mathcal{C}, \Sigma, \rightarrow, Inv, L^0, D^{\mathcal{V}_0}, L^m, D^m),$$

where

- L is a finite set of locations,

- $D^{\mathcal{V}} = D_1^{\mathcal{V}} \times \ldots \times D_n^{\mathcal{V}}$  is the domain of n variables  $\mathcal{V} = \{v_1, \ldots, v_n\}$ , where  $D_i^{\mathcal{V}}$  is a finite set of integers,

- C is a finite set of p discrete valued clocks  $\{c_1, \ldots, c_p\}$ ,

- $\Sigma$  is a nonempty finite set of events,

- $\rightarrow \subseteq L \times \mathcal{G}^{\mathcal{C}} \times \Sigma \times \mathcal{G} \times \mathcal{A} \times L$  is the transition relation,

- $Inv: L \to g^{\mathcal{C}}$ , is an invariant-assignment function,

- $L^0 \subseteq L$  is a set of initial locations,

- $D^{\mathcal{V}_0} = D_1^{\mathcal{V}_0} \times \ldots \times D_n^{\mathcal{V}_0}$  is a set of initial values of the variables,

- $L^m \subseteq L$  is a set of marked locations that are desired to be reached, and

- $D^m = D^{\mathcal{V}_m} \times D^{\mathcal{C}_m}$  is a set of pairs of marked valuations of the variables and clocks.

In addition to  $D^{\mathcal{V}}$ , we also define  $D^{\mathcal{C}}$  representing the domain of the p clocks. Later we will explain how the domain of a clock is defined and show that it is finite. The *global variable domain* denoted by  $D^{\mathcal{V}}_{\cup}$  is the set that contains the values of all variables, defined formally as:

$$D_{\cup}^{\mathcal{V}} = \bigcup_{i=1}^{n} D_{i}^{\mathcal{V}}.$$

The global clock domain denoted by  $D_{\cup}^{\mathcal{C}}$  is defined similarly. The largest value in  $D_{\cup}^{\mathcal{V}}$  and  $D_{\cup}^{\mathcal{C}}$  is denoted by  $\mu$ max $^{\mathcal{V}}$  and  $\mu$ max $^{\mathcal{C}}$ , respectively. If a variable exceeds its domain, the result is not defined, and from an implementation point of view, it is upon the developer to decide how to implement such cases. For instance, the program can give the user a warning. In our implementation, values outside the domain will be ignored and will not be included in our computations. In contrast to variables, it is assumed that if a clock  $c_i$  reaches its maximum value, it will keep its value until it is reset. For a clock  $c_i$ , this behavior is modeled by a saturation function  $\varrho_i: \mathbb{N} \to D_i^{\mathcal{C}}$ :

$$\varrho_i(x) = \begin{cases}

0 & \text{if } x < 0 \\

x & \text{if } 0 \le x < \mu \max_i^{\mathcal{C}} \\

\mu \max_i^{\mathcal{C}} & \text{if } x \ge \mu \max_i^{\mathcal{C}}

\end{cases},$$

where  $\mathbb{N}$  is the set of natural numbers. The function  $\varrho: \mathbb{N}^p \to D^{\mathcal{C}}$  is used to saturate the current value of all clocks.

The elements  $\mathcal{G}$  and  $\mathcal{A}$  are the sets of guards (conditional expressions) and action functions, respectively. In the TEFA framework, an arithmetic expression  $\varphi$  is formed according to the grammar

$$\varphi := \nu \mid v \mid c \mid (\varphi) \mid \varphi + \varphi \mid \varphi - \varphi \mid \varphi * \varphi \mid \varphi / \varphi \mid \varphi \% \varphi,$$

where  $v \in \mathcal{V}$ ,  $c \in \mathcal{C}$ ,  $\nu \in D_{\cup}^{\mathcal{V}} \cup D_{\cup}^{\mathcal{C}}$ , and % is the modulo operator. We use  $\varphi^{\mathcal{V}}$  to denote an expression that does not contain any clocks and thus  $\nu \in D_{\cup}^{\mathcal{V}}$ . A variable evaluation for a variable  $v_i \in \mathcal{V}$  is a function  $\mu_i^{\mathcal{V}} : v_i \to D_i^{\mathcal{V}}$ , assigning a value to the variable. A clock evaluation  $\mu_i^{\mathcal{C}} : c_i \to D_i^{\mathcal{C}}$  is defined similarly. A set of evaluations for all variables and clocks is represented by  $\mu^{\mathcal{V}}$  and  $\mu^{\mathcal{C}}$ , respectively.

A guard  $g \in \mathcal{G}$  is a propositional expression formed according to the grammar

$$g := (g) \mid g^{\mathcal{V}} \wedge g^{\mathcal{C}} \mid g^{\mathcal{V}} \vee g^{\mathcal{C}},$$

where  $g^{\mathcal{V}} \in \mathcal{G}^{\mathcal{V}}$  and  $g^{\mathcal{C}} \in \mathcal{G}^{\mathcal{C}}$  are guards that are based on regular variables and clocks, respectively,

$$g^{\mathcal{V}} := \varphi^{\mathcal{V}} < \varphi^{\mathcal{V}} \mid \varphi^{\mathcal{V}} \le \varphi^{\mathcal{V}} \mid \varphi^{\mathcal{V}} > \varphi^{\mathcal{V}} \mid \varphi^{\mathcal{V}} \ge \varphi^{\mathcal{V}} \mid \varphi^{\mathcal{V}} == \varphi^{\mathcal{V}} \mid (g^{\mathcal{V}}) \mid g^{\mathcal{V}} \wedge g^{\mathcal{V}} \mid g^{\mathcal{V}} \vee g^{\mathcal{V}} \mid \top \mid \bot,$$

$$g^{\mathcal{C}} := c < \omega \mid c \le \omega \mid c > \omega \mid c \ge \omega \mid c == \omega \mid (g^{\mathcal{C}}) \mid g^{\mathcal{C}} \wedge g^{\mathcal{C}} \mid \top \mid \bot,$$

where  $\top$  and  $\bot$  represent Boolean logic true and false, respectively, and  $\omega \in D_{\cup}^{\mathcal{C}}$ . This implies that clocks can only be compared to constants. All nonzero values are considered as  $\top$ . The semantics of a guard g is specified by a satisfaction relation  $\models$ , indicating the pair of variable and clock evaluations  $(\mu^{\mathcal{V}}, \mu^{\mathcal{C}})$  for which guard g is  $\top$ . It is written  $(\mu^{\mathcal{V}}, \mu^{\mathcal{C}}) \models g$ .

An action  $a \in A$  is a tuple of functions:

$$\mathbf{a} = (\mathbf{a}^{\mathcal{V}}, \mathbf{a}^{\mathcal{C}}) = ((a_1^{\mathcal{V}}, \dots, a_n^{\mathcal{V}}), (a_1^{\mathcal{C}}, \dots, a_p^{\mathcal{C}})).$$

A variable action  $a_i^{\mathcal{V}}:D^{\mathcal{V}}\times D^{\mathcal{C}}\to D_i^{\mathcal{V}}$  is a function that updates a variable; and a reset action  $a_i^{\mathcal{C}}:D^{\mathcal{C}}\to 0$  is a function that only resets a clock. Hence, for a variable, the action is formed as  $v_i=\varphi$  and for a clock it is formed as  $c_i=0$ . An action function  $a_i$  that does not update a variable or clock is denoted by  $\xi$ , which is later used in the synchronization process to determine the updated value of  $v_i$ . Function Inv assigns to each location a location invariant that constrains the amount of time that may be spent in the location. Specifically, the location should be left before the invariant becomes invalid. Semantically, this situation causes time evolution to halt. Intuitively, if a location invariant consists of a less than relation, the invariant can be considered as a deadline.

For a variable  $v_i$ ,  $D_i^{\nu_0}$  consists of the initial values of  $v_i$ . Since TEFAs are specifically designed to conform to the supervisory control theory (described in Chapter 3), it becomes natural to include a set of marked location and values in the tuple of definition of a TEFA. If the set of marked locations, evaluations of a variable or a clock is empty, then the entire domain is considered as marked. The states of a TEFA is defined as  $Q \subseteq L \times D^{\nu} \times D^{\mathcal{C}}$ . The state for a location  $\ell$ , variable evaluations  $\mu^{\nu}$ , and clock evaluations  $\mu^{\mathcal{C}}$  is represented as  $\langle \ell, \mu^{\nu}, \mu^{\mathcal{C}} \rangle$ . Based on the states of a TEFA, a state transition system can be defined.

#### **Definition 2.5** State Transition System of a TEFA

Let  $TE = (L, D^{\mathcal{V}}, \mathcal{C}, \Sigma, \rightarrow, Inv, L^0, D^{\mathcal{V}_0}, L^m, D^m)$  be a TEFA. Its corresponding state transition system (STS), denoted by  $STS(TE) = (Q, \Sigma, \mapsto, Q^0, Q^m)$ , is a 5-tuple where

- $Q = L \times D^{\mathcal{V}} \times D^{\mathcal{C}}$  is a finite set of states,

- $\Sigma$  is a set of events,

- $\mapsto \subseteq Q \times \Sigma \times Q$  is an explicit state transition relation defined by the following rule:

$$\frac{(l, \sigma, g, \mathbf{a}, \hat{l}) \in \to \land (\mu^{\mathcal{V}}, \mu^{\mathcal{C}}) \models g \land (\mu^{\mathcal{V}}, \mu^{\mathcal{C}}) \models Inv(l)}{(\langle l, \mu^{\mathcal{V}}, \mu^{\mathcal{C}} \rangle, \sigma, \langle \hat{l}, \mathbf{a}^{\mathcal{V}}(\mu^{\mathcal{V}}, \mu^{\mathcal{C}}), \mathbf{a}^{\mathcal{C}}(\mu^{\mathcal{C}}) \rangle) \in \mapsto}; \tag{2.1}$$

- $Q^0 = L^0 \times D^{\mathcal{V}_0} \times \mathbf{0}^p$  is a set of initial states ( $\mathbf{0}^p$  is a p-tuple of zeros),

- $Q^m = L^m \times D^m$  is a set of marked states, i.e., the states that are desired to end up in.

Indeed an STS is a FA with marked states. We deliberately use this new terminology to avoid confusions.

As mentioned earlier, we are only interested in deterministic systems.

#### **Definition 2.6 Deterministic TEFA**

A TEFA is deterministic if its corresponding STS is deterministic (based on Definition 2.2).

In the sequel, where ever we mention "TEFA", we refer to deterministic TEFA.

**Remark** (Nonzenoness). We have omitted requirements on the definition necessary for executability. From every reachable state, the TEFA should admit the possibility of time to diverge. For example, the automaton should not enforce infinitely many events in a finite interval of time. A TEFA satisfying this operational requirement is called *non-zeno* [39].

Similar to DFAs, FSC can be defined for TEFAs, referred to as *extended FSC* (*EFSC*). For a model with a number of TEFAs, we assume that the variables  $\mathcal{V}$  and clocks  $\mathcal{C}$  are all *global*, i.e., they are shared between the TEFAs, and that the clocks evolve synchronously with the same rate.

#### **Definition 2.7 Extended Full Synchronous Composition**

Consider the following two TEFAs

$$TE_k = (L_k, D^{\mathcal{V}}, \mathcal{C}, \Sigma_k, \rightarrow_k, Inv_k, L_k^0, D^{\mathcal{V}_0}, L_k^m, D^m),$$

for k = 1, 2. The Extended Full Synchronous Composition (EFSC) of  $TE_1$  and  $TE_2$ , denoted by  $TE_1 || TE_2$ , is defined as

$$TE_1 \parallel TE_2 = (L, D^{\mathcal{V}}, \mathcal{C}, \Sigma, \rightarrow, Inv, L^0, D^{\mathcal{V}_0}, L^m, D^m),$$

where

- $L = L_1 \times L_2$ ,

- $\Sigma = \Sigma_1 \cup \Sigma_2$ :

- the transition relation  $\rightarrow \subseteq L \times \mathcal{G}^{\mathcal{C}} \times \Sigma \times \mathcal{G} \times \mathcal{A} \times L$  is defined as follows,

$$\rightarrow = \{ (l, \sigma, g, \mathbf{a}, \hat{l}) \mid \forall (l, \sigma, g, \hat{\mathbf{a}}, \hat{l}) \in \rightarrow : \\ \forall i \in \{1, \dots, |\mathcal{V}|\} : \\ (\hat{a}_i = \xi \land a_i = v_i) \lor \\ (\hat{a}_i \neq \xi \land a_i = \hat{a}_i) \},$$

(2.2)

where

(a)

$$\sigma \in \Sigma_1 \cap \Sigma_2$$

:

$$\frac{(l_1, \sigma, g_1, \mathbf{a_1}, \acute{l_1}) \in \rightarrow_1 \land (l_2, \sigma, g_2, \mathbf{a_2}, \acute{l_2}) \in \rightarrow_2}{((l_1, l_2), \sigma, g, \hat{\mathbf{a}}, (\acute{l_1}, \acute{l_2})) \in \rightarrow}$$

such that,

\*

$$q = q_1 \wedge q_2$$

,

\* For

$$i = 1, ..., |\mathcal{V}|$$

,

$$\hat{a}_{i}^{\mathcal{V}} = \begin{cases} a_{1,i}^{\mathcal{V}} & \text{if } a_{1,i}^{\mathcal{V}} = a_{2,i}^{\mathcal{V}} \\ a_{1,i}^{\mathcal{V}} & \text{if } a_{2,i}^{\mathcal{V}} = \xi \\ a_{2,i}^{\mathcal{V}} & \text{if } a_{1,i}^{\mathcal{V}} = \xi \\ \xi & \text{otherwise} \end{cases},$$

where  $a_{k,i}^{\mathcal{V}}$  is the action function belonging to  $\rightarrow_k$ , updating the *i*-th variable, and  $\hat{\mathbf{a}}^{\mathcal{C}}$  is defined exactly as  $\hat{\mathbf{a}}^{\mathcal{V}}$  but on clocks,

(b)

$$\sigma \in \Sigma_1 \backslash \Sigma_2$$

:

$$\frac{(l_1, \sigma, g_1, \mathbf{a_1}, \acute{l_1}) \in \to_1 \land l_2 \in L_2}{((l_1, l_2), \sigma, g_1, \mathbf{a_1}, (\acute{l_1}, l_2)) \in \to},$$

(c)

$$\sigma \in \Sigma_2 \backslash \Sigma_1$$

:

$$\frac{(l_2, \sigma, g_2, \mathbf{a_2}, \acute{l_2}) \in \rightarrow_2 \land l_1 \in L_1}{((l_1, l_2), \sigma, g_2, \mathbf{a_2}, (l_1, \acute{l_2})) \in \rightharpoonup},$$

-

$$\forall (l_1, l_2) \in L : Inv(l_1, l_2) = Inv(l_1) \wedge Inv(l_2),$$

-

$$L^0 = L_1^0 \times L_2^0$$

, and

-

$$L^m = L_1^m \times L_2^m$$

.

Intuitively, in (2), an action function of form  $\hat{a}_i = \xi$  indicates that variable  $v_i$  keeps its current value. Similar to the proof in [38], it can be proved that the EFSC operator is both commutative and associative and can be extended to multiple TEFAs. Note that, in the case of multiple TEFAs, the transition relation  $\rightharpoonup$  in (2) refers to all TEFAs. In other words,  $\rightharpoonup$  should first be computed for all TEFAs and then replace  $\xi$  with the current value. In the above definition, also observe that when the action functions of  $TE_1$  and  $TE_2$  explicitly try to update a shared variable to different values, we assume that the variable is not updated. It can indeed be discussed whether such a transition should be executed, nevertheless, such a situation is usually a consequence of bad modeling.

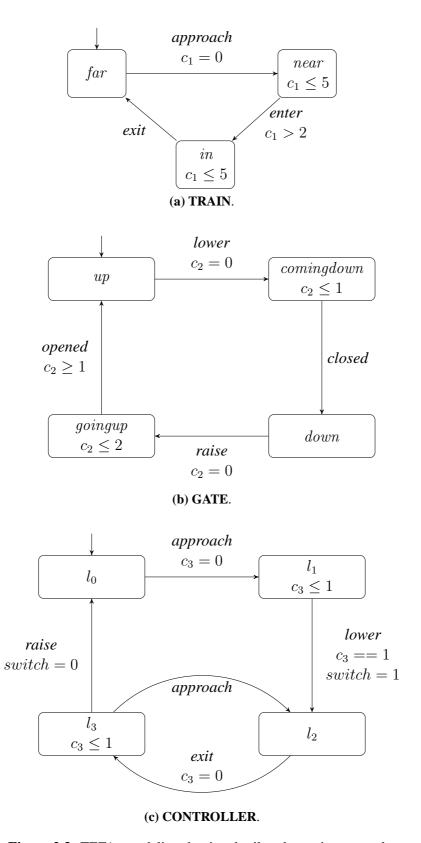

## EXAMPLE 2.2 Timed Railroad Crossing

Recall Example 2.1, and the issue of not being able to specify real-time constraints. Let us assume that a train does not exceed a certain maximum speed. For each component, the following timing properties are considered:

- **TRAIN** The train needs more than 2 minutes to reach the crossing after sending the *approach* signal; and it leaves the crossing 5 minutes after approaching it, at the latest.

- **GATE** Lowering the gate takes at most 1 minute, and raising it takes at least 1 and at most 2 minutes.

- **CONTROLLER** When the controller receives the signal *approach*, after exactly 1 minute it will close the gate by sending the signal *lower*. After receiving the *exit* signal, the controller raises the gate only if another train does not approach the crossing within 1 minute.

This timed system can be modeled by the following TEFAs

```

\textit{Train} = (\{\textit{far}, \textit{near}, \textit{in}\}, \emptyset, \{c_1\}, \{\textit{approach}, \textit{enter}, \textit{exit}\}, \rightarrow_1, Inv_1, \\ \{\textit{far}\}, \emptyset, \{\textit{far}\}, \emptyset), \\ \textit{Gate} = (\{\textit{up}, \textit{comingdown}, \textit{down}, \textit{goingup}\}, \emptyset, \{c_2\}, \\ \{\textit{lower}, \textit{closed}, \textit{raise}, \textit{opened}\}, \rightarrow_2, Inv_2, \{\textit{up}\}, \emptyset, \{\textit{up}\}, \emptyset), \\ \textit{Controller} = (\{l_0, \dots, l_3\}, \{0, 1\}, \{c_3\}, \{\textit{approach}, \textit{lower}, \textit{exit}, \textit{raise}\}, \rightarrow_3, \\ Inv_3, \{0\}, \{0\}, \{0\}, \{0\}), \\ \end{aligned}

```

where their corresponding transition relations and invariants are depicted in Figure 2.3. The invariants are illustrated by putting guards in the locations and a marked location is illustrated by a double line around the location. Compared to the DFA in Figure 2.2, it can be observed that the events *switch\_off* and *switch\_on* have been modeled by a variable *switch* with domain {0,1}, where values 0 and 1 correspond to events *switch\_off* and *switch\_on*, respectively.

In the TEFA GATE, clock  $c_1$  is set to zero on the occurrence of event *lower* and thus measures the elapse of time since that occurrence. Hence, the invariant  $c_1 \leq 1$  at location comingdown models the fact that the time delay between the occurrence of event lower and the change to location down is at most 1 minute. Note that this would not have been established by putting a guard  $c_1 \leq 1$  on the transition (comingdown, closed, down), as the value of  $c_1$  would not refer to the time of occurrence lower. Similarly, the invariant  $c_1 \leq 2$  at location goingup indicates that raising the gate takes at most 2 minutes. No constraints are imposed on the residence time for locations up and down, i.e.,  $Inv_1(up) = Inv_1(down) = \top$ .

21 2.3. Related Work

In the TEFA **TRAIN**, on approaching the gate, clock  $c_2$  is reset, and only if  $c_2 > 2$  is the train allowed to enter the crossing.

The TEFA of the controller is depicted in Figure 2.3c and is forced to send the signal *lower* to the gate exactly after 1 minute after the train has signaled its approaching. In location  $l_3$ , the invariant  $c_3 \leq 1$  indicates that if no other train comes within 1 minute, the signal *raise* should be sent to the gate.

The synchronized TEFA **GATE**||**TRAIN**||**CONTROLLER** represents the global behavior of the system. From the definition of STS (2.5), the reachable states of the synchronized model is a subset of

$$\{far, near, in\} \times \{up, comingdown, down, goingup\} \times \{l_0, \dots, l_3\} \times \{0, \dots, 6\} \times \{0, \dots, 3\} \times \{0, \dots, 2\} \times \{0, 1\},$$

where  $\{0,\ldots,6\}$ ,  $\{0,\ldots,3\}$ ,  $\{0,\ldots,2\}$ , and  $\{0,1\}$  correspond to the domains of  $c_1, c_2, c_3$ , and switch, respectively. Note that in the synchronized TEFA, the location  $(in, up, l_1)$  is not reachable. In this location, the train is at the crossing while the gate is open. The location can only be reached when  $c_1 > 2$ , but as  $c_1$  and  $c_3$  are reset at the same time (on entrance of the preceding location),  $c_1 > 2$  implies  $c_3 > 2$ , which is impossible due to  $l_1$ 's invariant  $c_3 \le 1$ .

## 2.3 Related Work

In model checking, a well-known modeling formalism that is used to model realtime applications, is timed automata (TAs) [21]. A timed automaton is a finite automaton extended with a finite set of real-valued clocks. Automated analysis of timed automata relies on the construction of a finite quotient of the infinite space of clock valuations. In an extended version, TAs can also include integer variables, denoted as ETAs [41]. Syntactically, TEFAs and ETAs are quite similar, however, from a semantical point of view, TEFAs are specifically designed to conform with the supervisory control theory. The main difference is how the composition operator is defined for TEFAs and TAs. In TEFAs, full synchronous composition is considered, where the synchronization is performed on all shared events and variables. In particular, two transitions can only be synchronized if both are labeled with the same shared event and if the guards are satisfied, while in TAs they also introduce a new type of events called urgent channels that can be taken as soon as they are enabled. Furthermore, the variable updates are treated differently. For a more elaborate and verbose exposition of TAs and their composition operator, refer to [41].

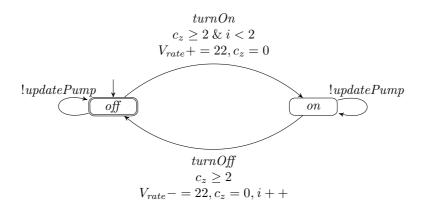

Figure 2.3: TEFAs modeling the timed railroad crossing example.

# **Chapter 3**

## **Supervisory Control Theory**

In 1987, Ramadge and Wonham showed that, for a DES, given a set models representing the behavior of the system, *plant*, and some desired properties, *specification*, there exists a unique control function, referred to as *supervisor*, that restricts the plant towards the specification, only when it is **necessary**. They called such a supervisor *minimally restrictive*. The main feature of a minimally restrictive supervisor is that it contains all the possible solutions a plant can be safely restricted towards the given specifications. This solution can later be used for quantitative analysis as well, such as time optimization. Later, they proposed a framework called *supervisory control theory (SCT)* [8], which is a mathematical framework for formal reasoning about supervision of systems modeled as DES. Traditionally, in SCT, a DES is based on formal languages, modeled by DFAs, and thus all the theory is defined on such models. In this chapter, in order to obtain compact models, we discuss how DES can also be modeled by EFAs. The supervisor will then be computed by transforming the EFAs to their corresponding FAs and applying conventional SCT.

However, the correct behavior of many real-time systems such as air traffic control systems and networked multimedia systems depends on the **delays** between events. Consequently, the researchers started to propose different approaches to apply SCT to TDES. There have been many attempts to model TDES and generalize SCT considering the real-time aspects [42]. These works can be divided into two categories; they are either based on *continuous* time or *discrete* time. In continuous time, the time is represented as real values while in discrete time, it is represented as integers. The question of which one to choose to model the systems is highly dependent on the structure of the specific applications and the properties that we want to check. For instance, in a manufacturing cell, where the components are synchronized by a PLC, discrete time is adequate to model the system and express most of its timing properties. A comparison between continuous and discrete time, according to their complexity and expressiveness, can be found in [43, 44]. In this thesis, we merely focus on discrete time.

The most settled framework, where SCT has been applied to TDES is a work

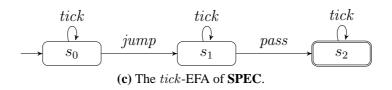

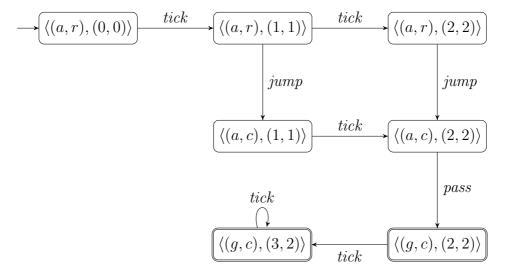

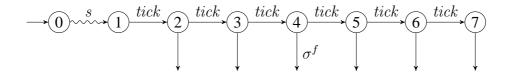

carried out by Brandin and Wonham in 1994 [17], where a TDES is modeled by *timed transition models (TTMs)* [45]. In this framework, it is assumed that there exists a global digital clock. Furthermore, lower and upper time bounds are associated to the events to restrict their occurrence time points. To be able to apply the theory to TTMs, they transform such models to FAs by introducing a special event called *tick*, which represents the passage of time, and is generated by the global clock.

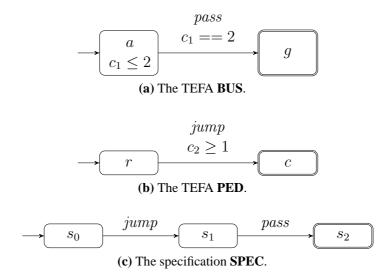

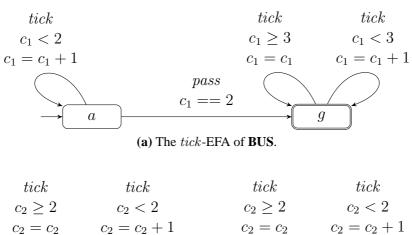

Similarly, in our framework, we model TDES by TEFAs; and in order to apply SCT, we transform the TEFAs to their corresponding EFAs by introducing a *tick* event to the model. Note that in this manner, we do not need to directly define SCT for TEFAs and thus refer all the formal discussions about SCT on TEFAs to [17].

Finally, in this chapter, we discuss how the computed supervisor can be represented modularly by generating guards based on the states of the computed supervisor and attach them to the original models, in order to restrict their behaviors towards the specifications. Representing the supervisor modularly can be beneficial in cases where the supervisor consists of a large number od states.

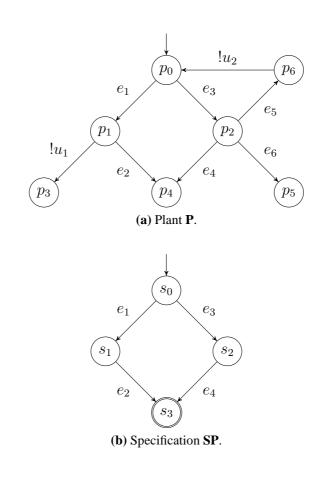

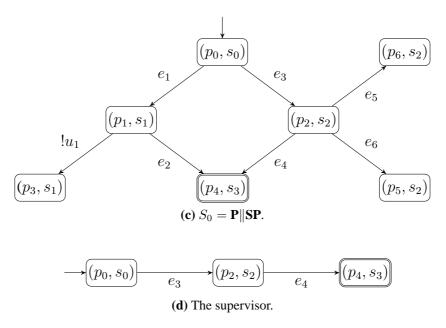

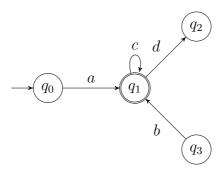

## 3.1 SCT of Untimed DES

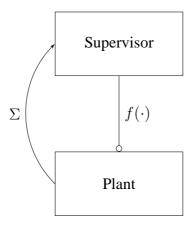

In this section, we describe the main concepts of SCT, defined for untimed DES. Figure 3.1 shows the *feedback loop* in the SCT. The plant spontaneously generates events in  $\Sigma$  that the supervisor can enable or disable as a function  $f(\cdot)$  of the earlier behavior of the plant (the observed sequence of events). As assumed earlier, the plant is modeled by DFAs. In [46], it was shown that the FSC operator can be used to model the supervision. That is, the supervisor can be considered as an automaton too. For example, when a supervisor S supervises a plant S, the behavior that S tries to enforce is S0. Notably, if S1 is not designed properly, some parts of the plant may not be susceptible to the control imposed by S3, so the actual behavior may be another. This is the reason why S3 should be synthesized using formal methods that guarantee that S3 does not try to control parts of the plant that can not be controlled or, in other words, that the *closed loop behavior* really is S1. In this work, we assume that the supervisor always refines the plant, that is, S2 is S3. We refer to the states of the supervisor as safe states and denote it by S3.

The supervisor decides to enable or disable events based on a given specification in terms of an automaton. It is also possible to explicitly specify some states in the plant or the specification as *explicitly forbidden* states, that are states where the system should not end up in. As pointed out earlier, for real systems, modeling the plant or the specification as a single automaton may become very large and complex. Therefore, the plant and specification are typically modeled as a set of sub-plans  $P_1, P_2, \ldots$  and sub-specifications  $Sp_1, Sp_2, \ldots$ , and thus the

Figure 3.1: The feedback loop in the SCT.

plant and the specification will be represented by the composition of their sub-components, i.e.,  $P = P_1 \| P_2 \| \dots$  and  $Sp = Sp_1 \| Sp_2 \| \dots$  For a composed automaton, a state is explicitly forbidden if at least one of its sub-states is explicitly forbidden in its corresponding automaton.

## Controllability

In general, it is reasonable to assume that some events in the plant are not susceptible to disablement by a supervisor. For example, the plant may sometimes act randomly or have internal doings that the supervisor can have no influence on. To incorporate this, the SCT introduces the notions of *controllable* and *uncontrollable* events. Controllable events can be disabled by the supervisor while uncontrollable can not.

It is important that the supervisor is *controllable*, meaning that while it restricts the plant towards the specification, it never tries to disable uncontrollable events. To this end, the alphabet  $\Sigma$  of the plant is divided into two disjoint sets of controllable events  $\Sigma^c$  and uncontrollable events  $\Sigma^u$ . Controllability, is assumed to be universally defined, that is, if an event  $\sigma$  is controllable in one automaton it is controllable in all other automata that consider that event. In figures, uncontrollable events are prefixed by an exclamation mark "!".

The formal definition of controllability is defined as follows.

## **Definition 3.1** Controllability

Let G and K be two DFAs. A state  $(p,q) \in Q_G \times Q_K$  is controllable if,

$$\forall \sigma \in \Sigma^u : \sigma \in \Gamma_G(p) \Rightarrow \sigma \in \Gamma_{G \parallel K}((p,q)).$$

K is controllable with respect to G if, for every state (p,q) that is reachable in G||K it holds that (p,q) is controllable.

Intuitively, K is controllable with respect to G if, in any reachable state in the composition, the enabled uncontrollable events in G are also enabled in  $G \| K$ . For the event to be enabled in  $G \| K$ , it must not be disabled in the corresponding state of K. That is, the event must either be enabled in the current state of K or not even present in the alphabet of K, in which case that event can be thought of as enabled in all states of K.

## **Nonblocking**

Even though a supervisor is controllable, it is not necessarily very useful. The supervisor guarantees that the plant does not violate the specification, however, the case may be that the supervisor restricts the plant from doing what it was supposed to do. For instance, the supervisor may allow the plant to get stuck somewhere, referred to as deadlock, or end up in a loop from which it can not get out, referred to as deadlock. To care of this, states of particular interest in the plant and in the specification can be marked, denoted by  $Q^m$ . The idea, then, is to design the supervisor so that it always allows the plant to reach at least one of the states that both plant and the specification have marked. Such a supervisor is called nonblocking, which in SCT is a property that a supervisor should have.

In the following, the definition of the nonblocking property is given.

## **Definition 3.2** Nonblocking

Let G be a DFA. A state  $q \in Q_G$  is said to be nonblocking if, starting from q at least a marked state belonging to  $Q^m$  could be reached. G is nonblocking if, for every state q that is reachable, it holds that q is nonblocking.

That is, an automaton is nonblocking when "all" reachable states can continue to reach some marked state. In a composed automaton, a state is marked if all its sub-states are marked in their corresponding automata. Essentially, the nonblocking states can be computed by taking the intersection between the reachable states and *coreachable states*, which are the states from which a marked state can be reached by a number of event executions.

## **Minimally Restrictiveness**

A careful reader may have realized that there does not exist a unique controllable and nonblocking supervisor. It is possible to supervise one and the same system in many different ways. More specifically, it is possible to design a controllable and nonblocking supervisor that restricts the plant more than necessary. It is natural to regard a supervisor that restricts the plant at little as possible, referred to as a *minimally restrictive*<sup>1</sup> supervisor. Designing a minimally restrictive supervisor

<sup>&</sup>lt;sup>1</sup>In some literature, it is also called maximally permissive, supremal, or optimal.

has several advantages. It gives the designers all the possible ways they can control a system, which could be beneficial from different perspectives. Especially, in this work, since we deal with timed systems, the supervisor will include some timing information, which can later be used for timing analysis. For instance, we may want to minimize the total time it takes to reach a marked state from any state in the supervisor. One way to this, is to have all possible solutions and select the proper ones.

In this thesis, we are interested in computing the **unique** controllable, non-blocking, and minimally restrictive supervisor, from now on, shortly "supervisor".

## 3.1.1 DES Modeled by EFAs

So far, we have assumed that DES are modeled by FAs. It is also possible to model DES by EFAs that also include discrete-valued variables. The main benefit of using EFAs, as a modeling tool, is that the values of the variables in state transitions can be hidden, yielding compact models.

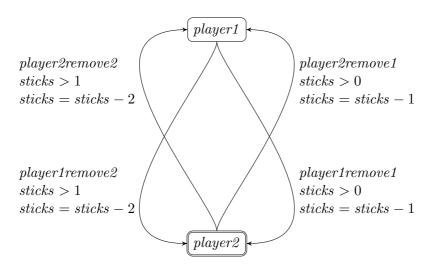

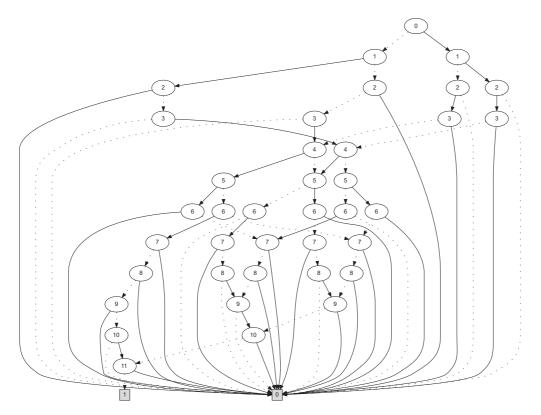

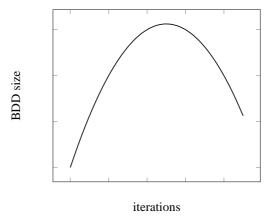

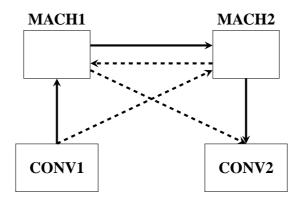

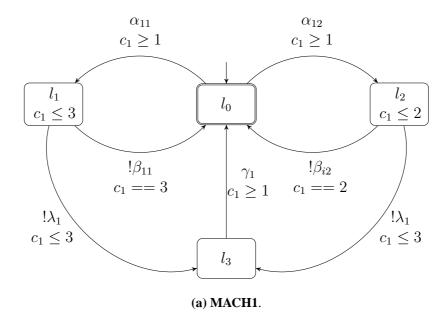

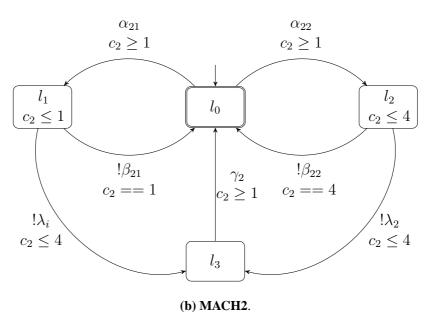

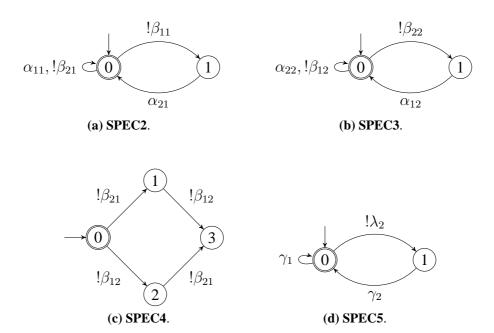

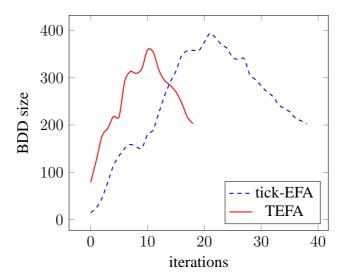

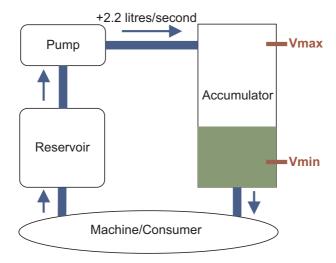

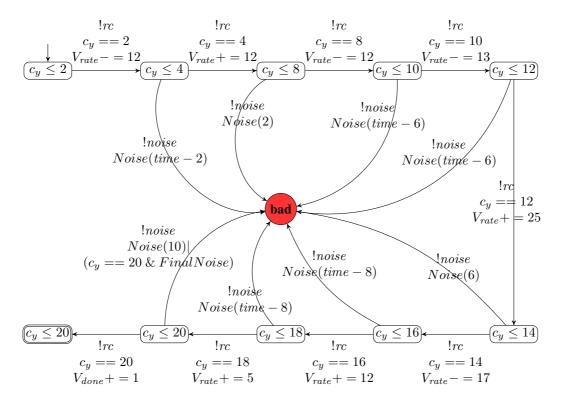

In the previous section, we explained the conventional SCT on DES modeled by FAs, where their transition relations are represented explicitly by their states and events. Hence, the theoretical framework of the conventional SCT cannot be directly applied to EFAs, where the states are implicitly represented in the models. The SCT can be applied to EFAs in two ways: 1) define a new theoretical framework for EFAs that conforms with the conventional SCT, or 2) transform the EFAs to their corresponding STS, i.e., FAs, and then apply the conventional SCT.