THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## EMI from Switched Converters – Simulation Methods and Reduction Techniques

ANDREAS KARVONEN

Department of Energy and Environment Division of Electric Power Engineering Chalmers University of Technology Göteborg, Sweden 2011 EMI from Switched Converters – Simulation Methods and Reduction Techniques ANDREAS KARVONEN ISBN 978-91-7385-568-6

© ANDREAS KARVONEN, 2011.

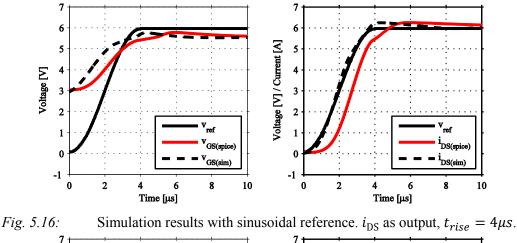

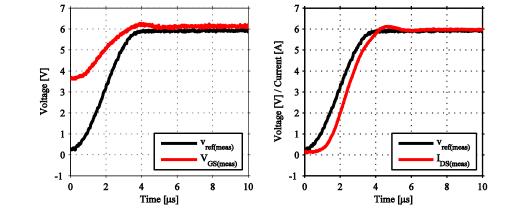

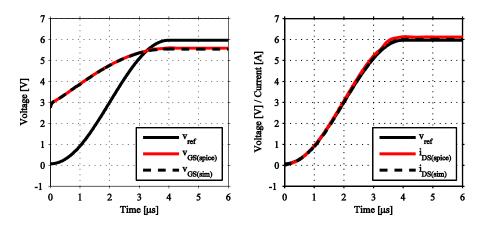

Doktorsavhandlingar vid Chalmers Tekniska högskola Ny serie nr. 3249 ISSN 0346-718X

Department of Energy and Environment Division of Electric Power Engineering Chalmers University of Technology SE–412 96 Göteborg Sweden Telephone +46 (0)31–772 1000

Chalmers Bibliotek, Reproservice Göteborg, Sweden 2011 To those who believed...

EMI from Switched Converters – Simulation Methods and Reduction Techniques ANDREAS KARVONEN Department of Energy and Environment Chalmers University of Technology

### Abstract

In this thesis, the conducted EMI from switched power converters has been analyzed using various existing models, own-derived models as well as measurements. The ingoing passive components in a switching converter have been modeled with respect to their high frequency behavior and the static and dynamic behavior of the active semiconductors has been analyzed. To understand the origin of EMI, the sources of EMI within a switching converter are investigated and measures how to reduce conducted emissions are analyzed. Once the background theory is known, all models of the ingoing components are verified as standalone units; i.e. the high frequency behavior of resistors, inductors, capacitors, printed circuit boards and relevant semiconductors are presented. The verified components are then put together to complete converters from which the emission levels are analyzed. As a measure to reduce EMI directly at the source, a new method of reducing EMI referred to as active gate control is investigated. The principle aims at reducing the high frequency content in the otherwise sharp voltage and current transitions by controlling the gate voltage during a switching event.

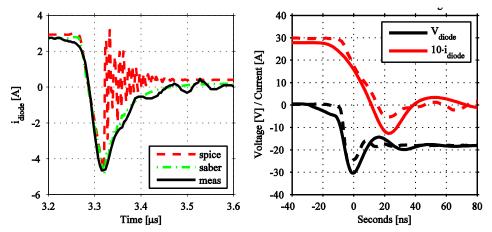

It has been found that many component models are insufficient for the purpose of EMI simulations; e.g. is the diode model in the widespread electric simulator SPICE unsuitable due to snappy reverse recovery behavior. Other simulation languages such as Simplorer and SABER<sup>®</sup> have solved this by incorporating more advanced diode models with adequate reverse recovery behavior that can be adapted to different diodes by more or less advanced parameter extraction procedures. Regarding MOSFET models, the black-box models provided by manufacturers have shown to exhibit good static and dynamic performance which in general makes them suitable for analysis of switching applications. Most analyzed IGBT models showed incorrect switching times and the most suitable model found in this thesis is the Simplorer model that requires more than 100 hand-tuned elements to show sufficient switching performance.

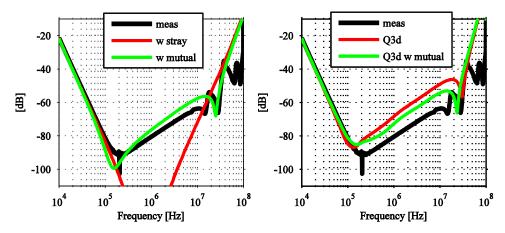

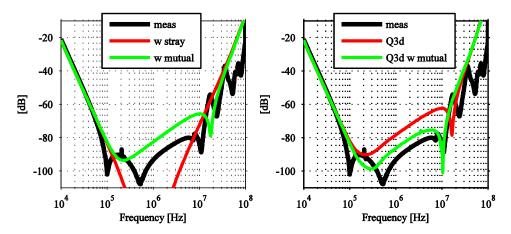

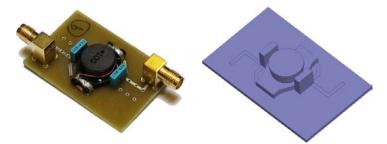

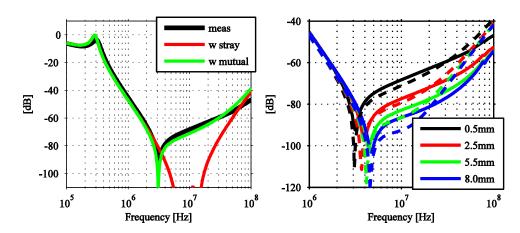

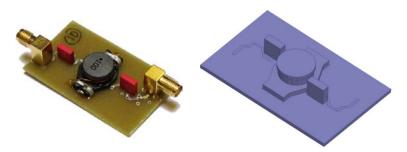

When a complete converter is to be simulated, it is concluded that it is essential to include parasitic elements (e.g. stray inductances and capacitances in the PCB and in the components) in the simulations to obtain correct switching behavior. By such a consideration by e.g. Ansoft Q3d that determine the parasitic elements within a PCB, the often unwanted oscillations in the circuit can be determined to a large extent. However, the conducted emission levels are not just determined by

stray elements and it has been has been shown both experimentally and in simulations that the levels are strongly determined by the mutual couplings in the input filter. The need for a diode model with correct reverse recovery behavior was shown to be important since the reverse recovery event affects the conducted EMI in the frequency region of 5 - 30MHz. The connection between reverse recovery current and emission levels has been verified in simulations and measurements for two different types of converter topologies.

The derived strategy of active gate control was verified both theoretically and by measurements that establish the operation principle. The method was shown to give a reduction in the conducted EMI of a MOSFET switching circuit and the most suitable unit to control was found to be the drain current. Finally, a reduced-order MOSFET model was shown to be sufficiently accurate to model static as well as switching applications due to its thorough characterization of the gate-drain capacitance as a function of applied voltages.

**Index Terms:** Semiconductor device measurements, semiconductor device modeling, diode modeling, diode reverse recovery, EMI, conducted emissions, DC/DC converters, state space methods.

## Acknowledgements

The financial support given by Volvocars AB, SAAB AB, Ericsson AB, SKF AB, Haldex AB and Vinnova is gratefully acknowledged. I would also like to thank all members in the project group, Björn Bergqvist who has been the project leader, Johan Fält, Anders Frick, Göran Lindsten and Nils Bjelk. A special thank is directed to Tryggve Tuveson who initiated the project and kept coming with new ideas throughout the project. Also, thanks to Pierre Gildert who supported me to start this thesis and Henrik Holst whose experiments gave me a literally flying start.

At the department I would like to thank my supervisor Torbjörn Thiringer who always find some extra time for discussions, no matter the time and reason. My supportive colleagues are gratefully acknowledged; Stefan Lundberg for constructive discussions, Massimo Bongiorno for technical support. A special thank to Johan Åström who always listen to my reflections and contribute with new creative ideas. Thanks to Kristofer Andersson and Mattias Thorsell at the Microwave Electronics Laboratory on Chalmers for helping me with the equipment. The enlightenment from Professor Claes Breitholtz is highly appreciated; the words shall act as a commandment for all coming work. Least but not last a thank you to all Master Thesis workers that have contributed, especially Niklas Fransson, Gustav Johanneson, Mattias Hedenskog, Joachim Härsjö and Emanuel Hallgren for their good spirit and valuable results.

Finally has the most important support been given by my friends and my family. A warm thank to all of you that have supported, motivated and encouraged me when disbelief have struck. Without you this would not have been possible.

Andreas Karvonen

Göteborg, Sweden

Summer, 2011

## Contents

| AbstractV |                                            |                                |                                     |     |  |  |  |  |

|-----------|--------------------------------------------|--------------------------------|-------------------------------------|-----|--|--|--|--|

| A         | cknov                                      | vledgen                        | nents                               | VII |  |  |  |  |

| Co        | onten                                      | ts                             |                                     | IX  |  |  |  |  |

| 1         | Intr                                       | oductio                        | n                                   | 1   |  |  |  |  |

|           | 1.1                                        | Proble                         | 1                                   |     |  |  |  |  |

|           | 1.2                                        | Literature overview            |                                     | 2   |  |  |  |  |

|           | 1.3                                        | 1                              | se of the Thesis                    |     |  |  |  |  |

|           | 1.4                                        | Contri                         | 5                                   |     |  |  |  |  |

|           | 1.5                                        | Outlin                         | e of Thesis                         | 6   |  |  |  |  |

|           | 1.6                                        | Public                         | ations                              | 7   |  |  |  |  |

| 2         | Converter Components and Behavioral Models |                                |                                     |     |  |  |  |  |

|           | 2.1                                        | Passiv                         | ve Components                       |     |  |  |  |  |

|           |                                            | 2.1.1                          | Wires and PCB Tracks                |     |  |  |  |  |

|           |                                            | 2.1.2                          | Resistive Components                |     |  |  |  |  |

|           |                                            | 2.1.3                          | Capacitive components               |     |  |  |  |  |

|           |                                            | 2.1.4                          | Inductive components                |     |  |  |  |  |

|           |                                            | 2.1.5                          | Mutual Coupling between Components  |     |  |  |  |  |

|           | 2.2                                        | 2 Semiconductors and Materials |                                     |     |  |  |  |  |

|           | 2.3                                        | The D                          |                                     |     |  |  |  |  |

|           |                                            | 2.3.1                          | The PiN-Diode                       |     |  |  |  |  |

|           |                                            | 2.3.2                          | The Schottky Diode                  |     |  |  |  |  |

|           |                                            | 2.3.3                          | Diode Modeling                      |     |  |  |  |  |

|           |                                            | 2.3.4                          | Modeling of the Schottky Diode      |     |  |  |  |  |

|           | 2.4 The MOSFET                             |                                |                                     |     |  |  |  |  |

|           |                                            | 2.4.1                          | Internal Capacitances of the MOSFET |     |  |  |  |  |

|           |                                            | 2.4.2                          | Turn-On Behavior of the MOSFET      |     |  |  |  |  |

|           |                                            | 2.4.3                          | Turn-Off Behavior of the MOSFET     |     |  |  |  |  |

|           |                                            | 2.4.4                          | Modeling of the MOSFET              |     |  |  |  |  |

|           | 2.5 The IGBT                               |                                |                                     |     |  |  |  |  |

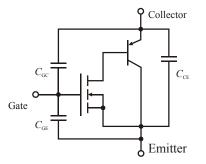

|           |                                            | 2.5.1                          | Internal Capacitances of the IGBT   |     |  |  |  |  |

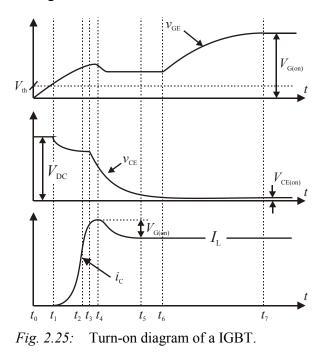

|           |                                            | 2.5.2                          | Turn-On Behavior of the IGBT        |     |  |  |  |  |

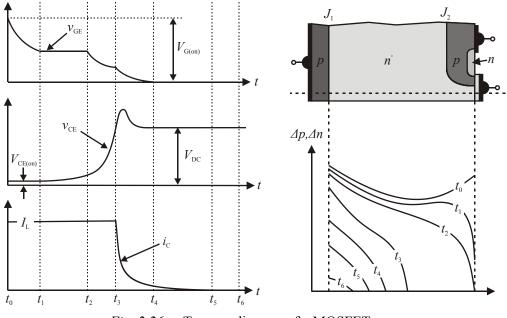

|           |                                            | 2.5.3                          | Turn-Off Behavior of the IGBT       |     |  |  |  |  |

|           |                                            | 2.5.4                          | Modeling of the IGBT                |     |  |  |  |  |

| 3         | Test                                       |                                |                                     |     |  |  |  |  |

|           | 3.1                                        |                                | 39                                  |     |  |  |  |  |

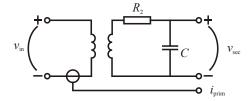

|           | 3.2                                        | Ramp                           |                                     |     |  |  |  |  |

|           | 3.3                                        | Induct                         | tive Test Circuit                   |     |  |  |  |  |

|           |                                            |                                |                                     |     |  |  |  |  |

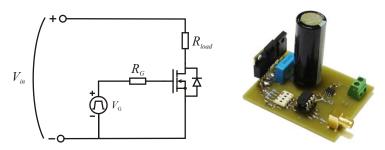

|   | 3.4  | Switching Circuit with Resistive Load                          |                                                 |     |  |  |  |  |  |

|---|------|----------------------------------------------------------------|-------------------------------------------------|-----|--|--|--|--|--|

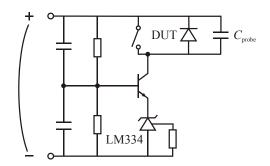

|   | 3.5  | 5 Capacitance Test Circuit                                     |                                                 |     |  |  |  |  |  |

|   | 3.6  | Impeda                                                         | nce Test Set-up                                 |     |  |  |  |  |  |

|   |      | 3.6.1                                                          | Inductive components                            |     |  |  |  |  |  |

|   |      | 3.6.2                                                          | PCB Impedance Test Board                        |     |  |  |  |  |  |

|   |      | 3.6.3                                                          | Circuits for Mutual Coupling                    |     |  |  |  |  |  |

|   | 3.7  | Comple                                                         | te Converters                                   |     |  |  |  |  |  |

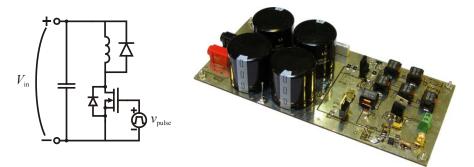

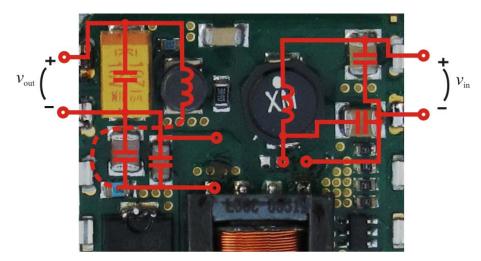

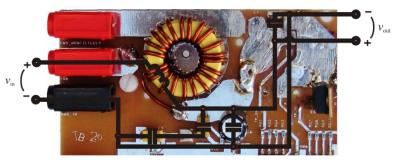

|   |      | 3.7.1                                                          | Flyback DC/DC Converter                         |     |  |  |  |  |  |

|   |      | 3.7.2                                                          | Synchronous Step-Down Converter                 | 45  |  |  |  |  |  |

| 4 | Mod  | Modeling and Measurements of Components in Switched Converters |                                                 |     |  |  |  |  |  |

| • | 4.1  | Passive                                                        | Components                                      |     |  |  |  |  |  |

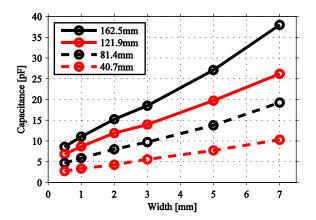

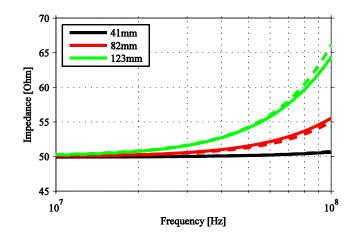

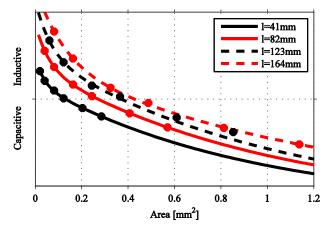

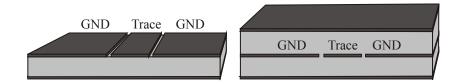

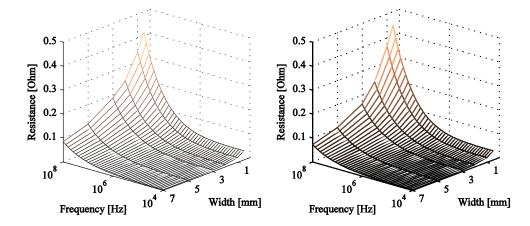

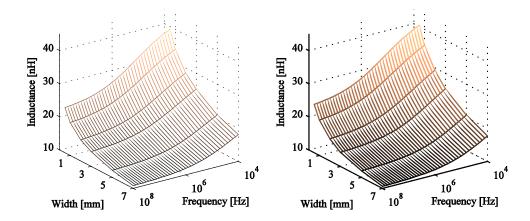

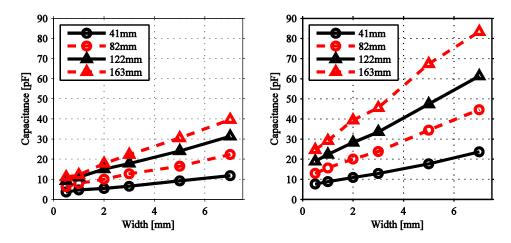

|   |      | 4.1.1                                                          | Parasitic Properties of PCB Traces              |     |  |  |  |  |  |

|   |      | 4.1.2                                                          | Parasitic Properties for Different PCB Stackups |     |  |  |  |  |  |

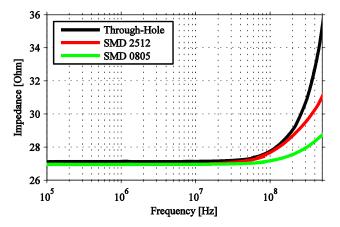

|   |      | 4.1.3                                                          | Resistive Components                            |     |  |  |  |  |  |

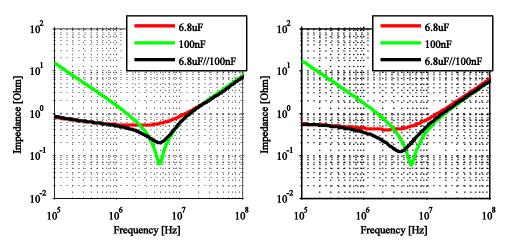

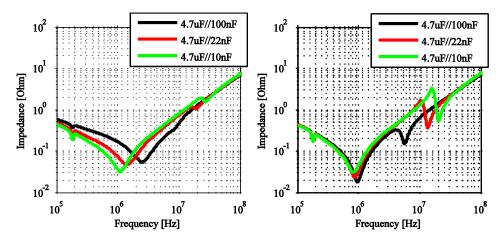

|   |      | 4.1.4                                                          | Capacitive Components                           |     |  |  |  |  |  |

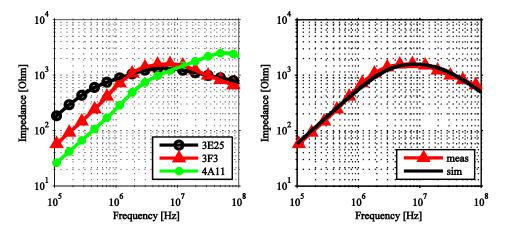

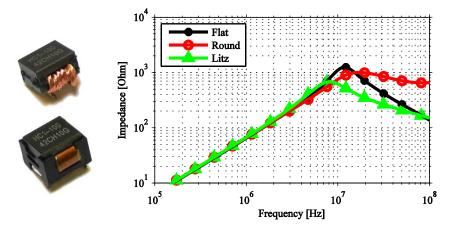

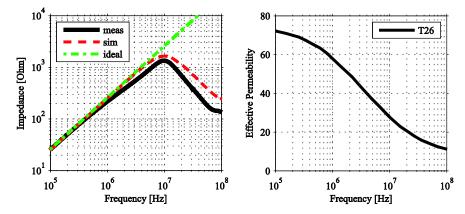

|   |      | 4.1.5                                                          | Inductive Components                            |     |  |  |  |  |  |

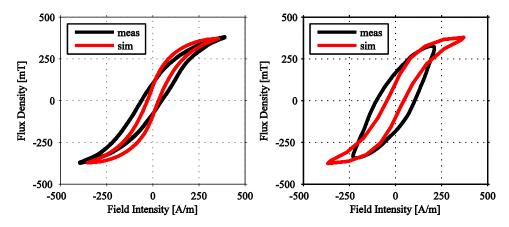

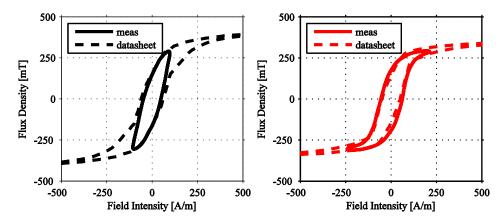

|   |      | 4.1.6                                                          | Temperature Effects in Ferrites                 | 64  |  |  |  |  |  |

|   | 4.2  | Diodes                                                         | 65                                              |     |  |  |  |  |  |

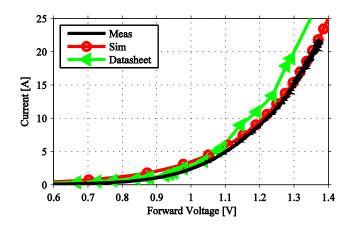

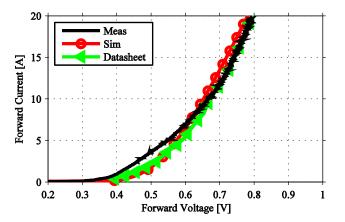

|   |      | 4.2.1                                                          | Static Performance                              | 65  |  |  |  |  |  |

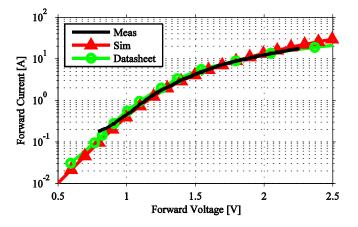

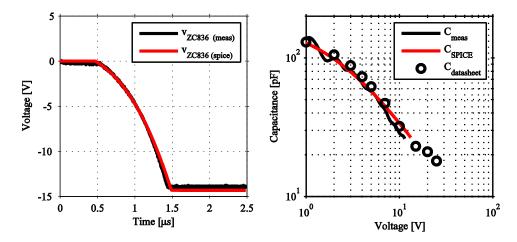

|   |      | 4.2.2                                                          | Determining the Junction Capacitance            | 67  |  |  |  |  |  |

|   |      | 4.2.3                                                          | Validation of the Reverse Recovery              | 69  |  |  |  |  |  |

|   |      | 4.2.4                                                          | Temperature Effects of Diode Performance        | 72  |  |  |  |  |  |

|   | 4.3  | MOSFE                                                          | ET                                              |     |  |  |  |  |  |

|   |      | 4.3.1                                                          | Nodal Analysis vs. State Variable Approach      | 75  |  |  |  |  |  |

|   |      | 4.3.2                                                          | A Novel Model Based on Circuit Analysis         |     |  |  |  |  |  |

|   |      | 4.3.3                                                          | Parameter Extraction for a Power MOSFET         |     |  |  |  |  |  |

|   |      | 4.3.4                                                          | MOSFET Model under Static Conditions            |     |  |  |  |  |  |

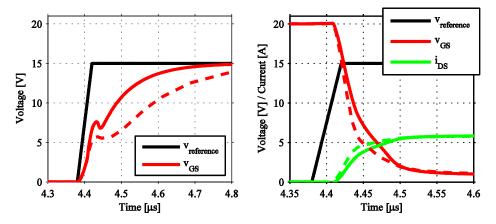

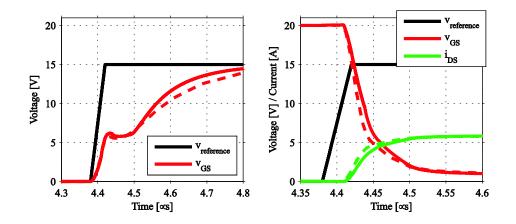

|   |      | 4.3.5                                                          | MOSFET Model under Dynamic Conditions           |     |  |  |  |  |  |

|   |      | 4.3.6                                                          | Switching With Resistive Load                   |     |  |  |  |  |  |

|   |      | 4.3.7                                                          | Validity for Different Components               | 90  |  |  |  |  |  |

|   | 4.4  | IGBT                                                           | 91                                              |     |  |  |  |  |  |

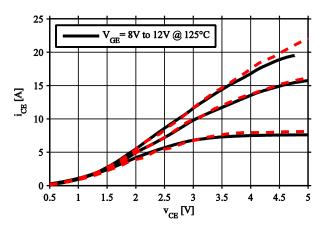

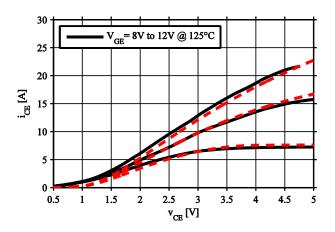

|   |      | 4.4.1                                                          | The IGBT Model under Static Conditions          |     |  |  |  |  |  |

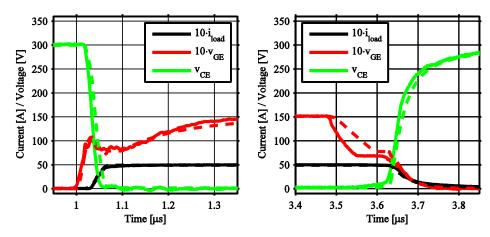

|   |      | 4.4.2                                                          | Dynamic Properties of the IGBT Model            |     |  |  |  |  |  |

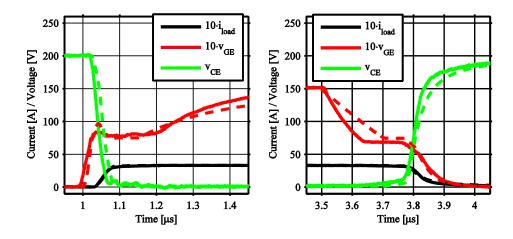

|   |      | 4.4.3                                                          | Switching with Purely Resistive Load            |     |  |  |  |  |  |

|   |      | 4.4.4                                                          | Temperature Effects in the IGBT                 |     |  |  |  |  |  |

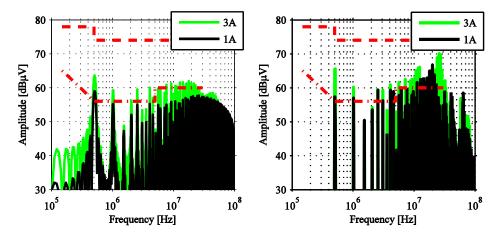

| 5 | Acti | Active Gate Control                                            |                                                 |     |  |  |  |  |  |

|   | 5.1  | Active (                                                       | Gate Control - Theoretical Derivation           |     |  |  |  |  |  |

|   | 5.2  |                                                                |                                                 |     |  |  |  |  |  |

|   | 5.3  | Selecting the Output of the System                             |                                                 |     |  |  |  |  |  |

|   | 5.4  | Implem                                                         | entation of Active Gate Control                 |     |  |  |  |  |  |

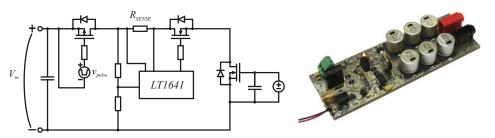

|   |      | 5.4.1                                                          | Step Response of the System                     | 111 |  |  |  |  |  |

|   |      | 5.4.2                                                          | Sinusoidal Step Response of the System          |     |  |  |  |  |  |

|   |      |                                                                |                                                 |     |  |  |  |  |  |

|    |                                | 5.4.3                                                    | Controller Design with Varying Parameters   | 119 |  |

|----|--------------------------------|----------------------------------------------------------|---------------------------------------------|-----|--|

|    |                                | 5.4.4                                                    | Robustness of the Circuit                   |     |  |

|    |                                | 5.4.5                                                    | Switching Losses with Active Gate Control   | 125 |  |

| 6  | Implementation into Converters |                                                          |                                             |     |  |

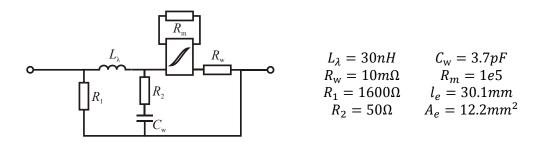

|    | 6.1                            | Switch                                                   | ning Circuit Modeling                       | 129 |  |

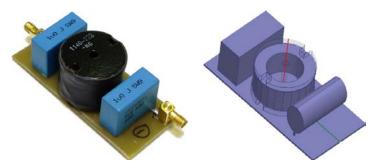

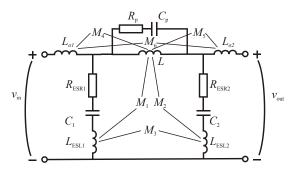

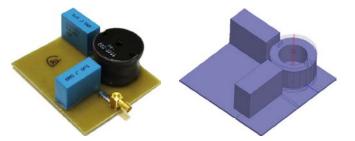

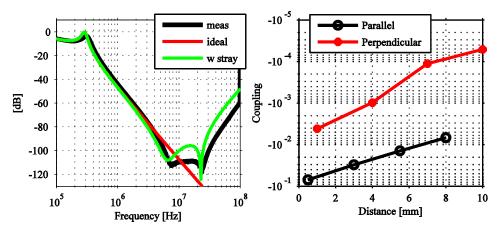

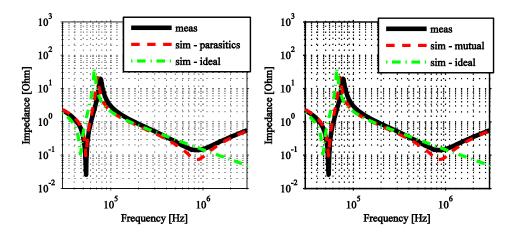

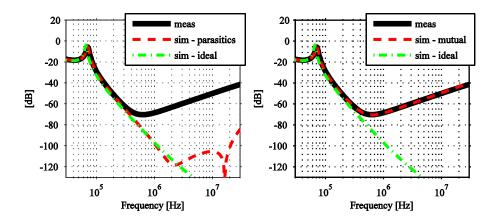

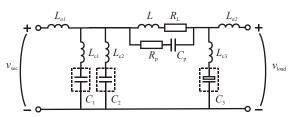

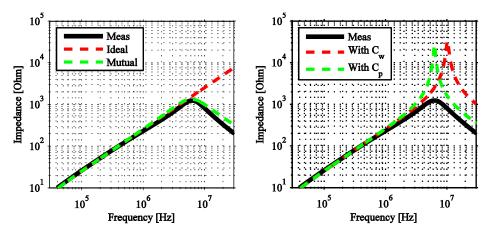

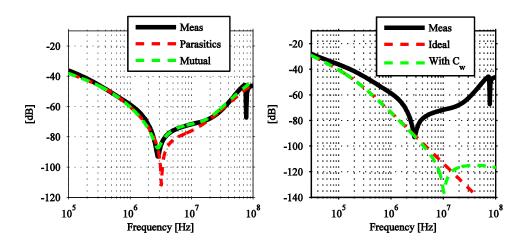

|    | 6.2                            | Mutua                                                    | l Couplings and Filter Performance          | 130 |  |

|    |                                | 6.2.1                                                    | Mutual Inductive Couplings                  | 130 |  |

|    |                                | 6.2.2                                                    | Component Placement                         | 132 |  |

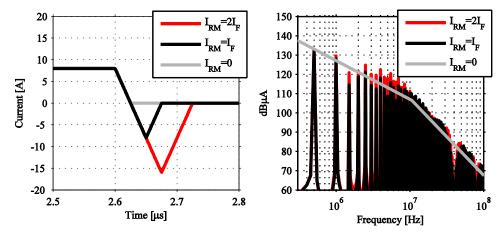

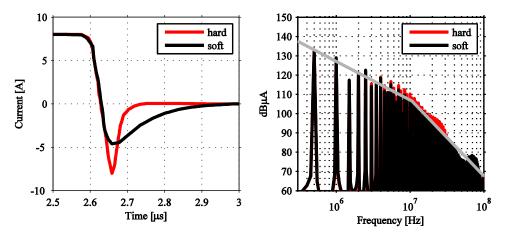

|    | 6.3                            | The In                                                   | fluence of Reverse Recovery on EMI          | 136 |  |

|    | 6.4                            | Implementation into a Flyback Converter and Influence of |                                             |     |  |

|    |                                |                                                          | Reverse Recovery                            | 138 |  |

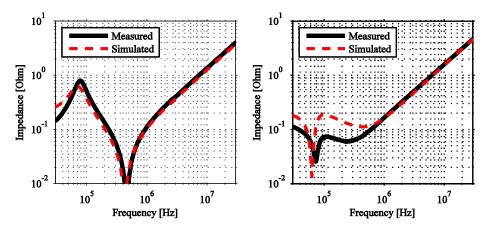

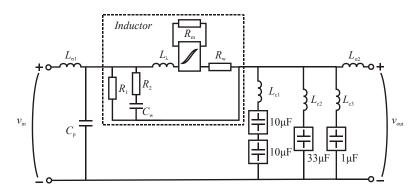

|    |                                | 6.4.1                                                    | The Input and Output Filters                | 140 |  |

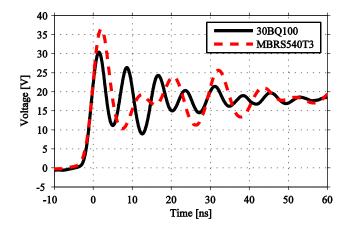

|    |                                | 6.4.2                                                    | Oscillations in the Circuit                 | 143 |  |

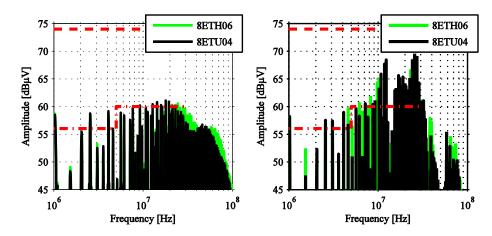

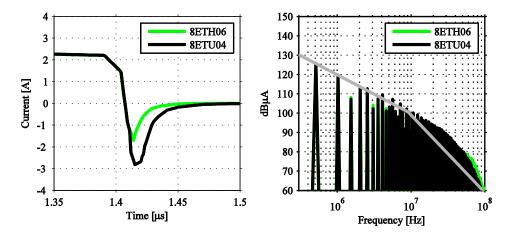

|    |                                | 6.4.3                                                    | Conducted Emissions with pn-diodes          | 144 |  |

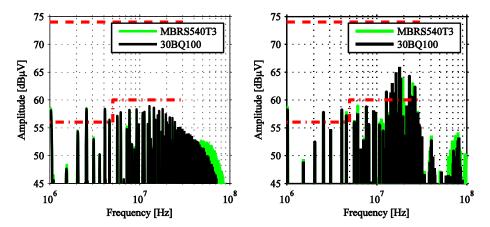

|    |                                | 6.4.4                                                    | Emissions with Schottky diodes              | 146 |  |

|    | 6.5                            | Step D                                                   | own Converter and the Effect of Synchronous |     |  |

|    |                                |                                                          | Rectification                               | 147 |  |

|    |                                | 6.5.1                                                    | The Step-Down Input Filter                  | 148 |  |

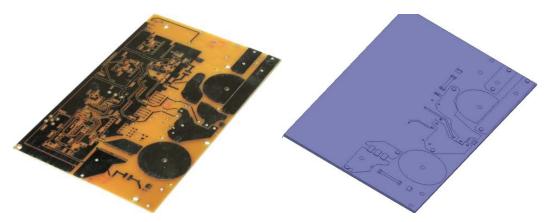

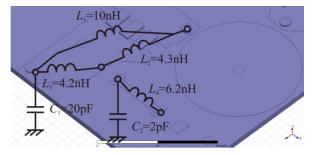

|    |                                | 6.5.2                                                    | Stray Elements within the PCB               | 151 |  |

|    |                                | 6.5.3                                                    | Oscillations in the Circuit                 | 152 |  |

|    |                                | 6.5.4                                                    | Diode Rectification                         | 152 |  |

|    |                                | 6.5.5                                                    | Synchronous Rectification                   | 155 |  |

| 7  | Con                            | cluding                                                  | Remarks                                     | 159 |  |

|    | 7.1                            | Conclu                                                   | usions                                      | 159 |  |

|    |                                | 7.1.1                                                    | Component Modeling                          | 159 |  |

|    |                                | 7.1.2                                                    | Active Gate Control                         | 160 |  |

|    |                                | 7.1.3                                                    | System Modeling                             | 161 |  |

|    | 7.2                            | Future                                                   | Work                                        | 161 |  |

| Re | eferer                         | 1ces                                                     |                                             | 163 |  |

# **Chapter 1**

## Introduction

### **1.1 Problem Background**

Power electronic converters can be found wherever there is a need to modify the properties of electrical energy, i.e. voltages, currents or frequencies. The area of application ranges over a wide span such as point-of-load supplies on computer motherboards, traction control for electric drives and connection of windpower plants to the grid. One trend in the automotive industry is that objects that originally were mechanically operated are being replaced by electronically controlled ones. These electrical loads often demand variable power at a varying voltage level; hence DC/DC converters and AC/DC inverters are employed. The trend of employing multiple switched converters can also be applied to the server and telecom industry, not due to the plentiful occurrence of mechanical loads, but rather to the high demand of multiple voltages that supplies processors and other consumers. Another aspect that emphasizes the importance of reduced electromagnetic interference from switched converters is the aspect of area and volume. In e.g. the automotive industry, all locations where electronic equipment can be placed are often strictly predetermined due to the restricted volume that all components have to coexist within. Since a switched converter often carry high currents and utilizes large magnetic and inductive components, it may act as a source of disturbance to sensitive equipment located nearby. Due to the aspect of limited volume, the work in this has been focused on methods and means to reduce EMI from a switched converter without adding extra filtering or shielding. Hence, a new method to reduce EMI directly at the source is proposed by directly attacking the high derivatives that occur in a converter.

The perhaps most important incitement for the increased concern of EMI is the relatively new EMC Directive, 2004/108/EC, that is valid from July 2007 within the entire EU. It is by some considered as one of the most comprehensive standards ever to originate from the European Commission and consists of directives that govern both the electromagnetic emission and immunity of a

Chapter 1 - Introduction

device. The levels are governed by standards (CISPR and IEC) and cover several different areas e.g. CISPR 25 (Vehicles, boats and internal combustion engines - Radio disturbance characteristics) which is directly used by several large automotive companies. In addition to ensure equipment functionality, the EC directive 2004/40/EC aims at protecting workers from adverse health effects resulting from exposure to non ionizing electromagnetic fields. The directive contains minimum requirements concerning electromagnetic fields that an employer must fulfill; this certainly affects the automotive industry and gives another incentive to keep electromagnetic disturbances as low as possible. All in all, these new directives in combination with the growing electrification and increase of converter power density are the major reason for investigating new methods that can minimize EMI from switched DC/DC converters.

To facilitate the design process of a new product it is often of paramount importance to be able to simulate the design before it is being tested as a prototype. This has not been the case for the prediction of the electromagnetic emissions from a device and the reasons for omission have often been numerous; lack of knowledge how to simulate EMI, insufficiency in the electric simulator tools and a least but not last the complex nature of a switched converter. In order to be able to simulate a more adequate EMI signature, a multi domain simulation tool is needed where different simulators, e.g. electric circuits and FEM calculations can be connected together. This feature has been developed during the last year and as a new emerging technology it gives new possibilities, in this thesis multi domain simulation tools have been applied on switched converters to form a more covering scope of how to predict EMI issues.

## **1.2** Literature overview

The first topic that needs to be considered when the EMI from a switched converter is investigated is the point of generation. The major sources of EMI from a switched converter are well known and an extensive study is presented in [1]. To be able to quantify how much each of these sources contribute to the total EMI and to facilitate the design process, proper simulation tools are needed and numerous studies of how to simulate EMI from a switched converter have previously been performed. The first category of simulations is the electrical circuit simulators that are based on analytical approximations of the parasitic element [2-5]. In general, these models shows discrepancies between simulation results and measurements for higher frequencies and the versatility is drastically reduced due to difficulties in determining the parasitic capacitances in the circuit. A more general approach for simulating EMI is proposed in [6, 7] where an EMI prediction tool based on approximating the switching event is implemented. By finding the correct current and voltage derivatives during the switching event, the EMI noise can be reconstructed. The major deficit is that it only can be quantified

once the switching event is known in detail. Regarding field simulations, full 3D models based on the finite difference time-domain (FDTD) have been investigated in [8] but with lack of the converter that generate EMI and in [9] that investigate FDTD co-simulations with SPICE aimed for low power electronics and radiated fields. 3D-simulations with the Partial Element Equivalent Circuit (PEEC) method have also been investigated in [10] but with lacking integration of electric circuit models. Other methods simulating the electric fields have also been proposed in e.g. [11] where the stray parameters are extracted from a PEEC-program and [12] where a completely new programs has been developed. These methods are often based on several simplifications and do not show any good possibilities to be reused for different applications which make their versatility limited. A comprehensive study of how parasitics with a converter can be modeled is presented in [13] where both circuit simulations are supplemented with PEEC-simulations, but without the advantage to co-simulate both environments.

The effect of electric and magnetic fields from a converter and component placement has been investigated in e.g. [14] that analyzed where the highest electric fields are located but without any quantification on how it impacts EMI performance. The work regarding mutual couplings can be divided into to two major branches where the first branch focuses on letting the mutual couplings interact in a positive way so that they improve filter performance. The analysis have either been lacking a system aspect [15-17] or been based on numerical approximations of the parasitic elements [18, 19]. The second field of investigation is how mutual couplings affect conducted emissions and filter performance directly [20, 21] but without analyzing a total system performance. Perhaps the most extensive and thorough investigation is found in [22] where the influence of mutual couplings on conducted emissions has been investigated with good results. The analysis have however been focused on low power devices and no quantification of the different mutual couplings has been made which motivate the analysis performed in this thesis.

Several different approaches to reduce the EMI by controlling the gate signal have been studied but none have been aimed at controlling the entire transition. Methods of gate driving have been studied where an intermediate gate voltage slightly over the threshold voltage is applied to the gate terminal during the switching event. The technique require simple control and claims to lower EMI due to reduced dv/dt and also reduce the switching losses [23, 24]. A similar approach is to apply different sizes of gate resistors during different phases of the turn-on and turn-off process respectively which reduces the di/dt [25]. The closest technique that resembles the proposed technique with active gate control is the two-stage method [26, 27] where the di/dt of the transistor current is controlled by an external current generator. Developments of this method with more advanced control strategies have been presented in [28] and [29]. Several other measures of EMI reduction techniques can also be used like snubbers [30], random switching [31] and interleaving of converters [32]. However, a well designed converter can to some extent reduce the need of these additional measures which the main goal with this thesis. This aim has become even more relevant during the last year when a new possibility has opened for electric simulators to in an elementary way co-simulate the functionality of an electric circuit with other domains such as electric field calculations and even take temperature effects into account.

## **1.3 Purpose of the Thesis**

As stated above, various areas of EMI from switched converters have been a target for investigation under a long time. The general objectives of this thesis can be divided into two major parts; to analyze a new strategy of how EMI can be reduced directly at the source and to analyze, simulate and validate the mechanisms of low frequency EMI generation in a switched converter both on component and system level. The purpose can be summarized as follows:

- Analyze ways to reduce the EMI from a switched converter by attacking the cause of harmonics directly at the source. The proposed way to do this in this thesis is to control the voltage and current derivatives in an advantageous way so that the harmonic content is reduced. By doing this, use of additional components such as extra filtering, shielding and snubber circuits is reduced.

- Establish suitable models for the ingoing components in a switched converter. The models shall be valid for all operation points and account for both correct high frequency behavior and temperature effects where found necessary. Most important of all shall the model be easy to parameterize which shall make the results reproducible and widely applicable to different types on converters.

- Quantify which types of components and design methods that can be used in order to enhance the EMI performance of a drive system. All ingoing components and are analyzed with respect to EMI performance and a quantification is made where different components are favorable to use.

- Make comparative studies of how different parameters affect the EMI performance on a switched converter. Once the most suitable components are selected, the parasitic properties still contribute to the total EMI signature, but with a quantification of how the different parameters affect the total EMI signature, even more enhancements can be made.

• Analyze the temperature behavior of the ingoing components and ensure that the developed models correspond well to the simulations. Once the temperature behavior is established, the effect of the changes in the characteristics is analyzed with respect both to switching behavior and EMI signature.

## **1.4 Contributions with Present Work**

Due to the wide range of topics in this thesis, most contributions relate to comparative studies that quantify differences between the components that are used in a modern switched converter and how these differences can be used to reduce EMI levels. To the best knowledge of the author the contributions are summarized as follows.

- A strongly reduced MOSFET model in the state-space form intended for usage in the derivation process of active gate control has been developed. The static (e.g. output characteristics) and dynamic behavior (e.g. switching characteristics) of the model has been verified against measurements and a detailed SPICE model of the same component provided by the same manufacturer.

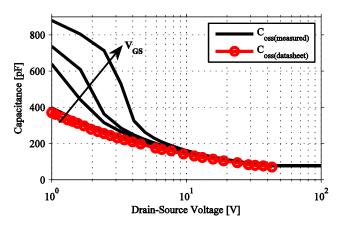

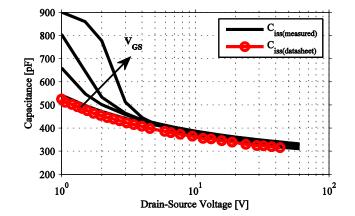

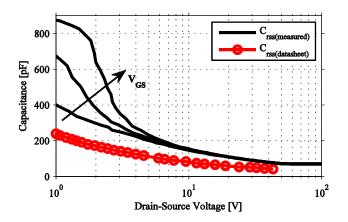

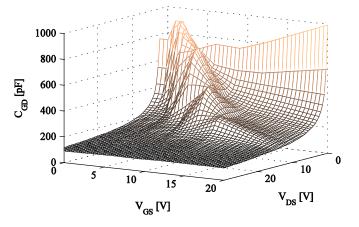

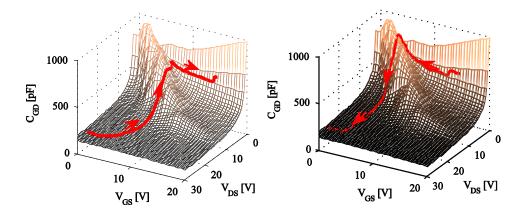

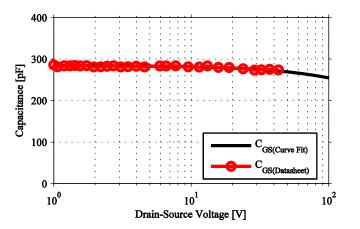

- Quantification of the changes in gate-drain capacitance in a MOSFET during a switching event both by measurements and simulations. Also, the importance of the gate-drain capacitance magnitude to obtain a correct switching event is determined.

- Experimental and theoretical implementation of active gate control to reduce the emissions in a switched converter. Both the drain-source voltage and the drain current of a MOSFET were analyzed and controlled and where the drain current was found to be more straightforward to control via a current feedback loop. The controller parameters for the implementation were found using the previously derived MOSFET state-space model.

- The reverse recovery behavior of different diodes has been investigated and verified against both simulations and measurements with good agreement. To obtain this, many different diode models have been analyzed where the one found in Simplorer has the most comprehensive coverage of the recovery phenomenon.

- Quantification of the importance of diode reverse recovery with respect to conducted emissions. Different diodes with different recovery behavior have been simulated where it is found that the reverse recovery event

#### Chapter 1 - Introduction

affects the conducted emissions. The models were verified by analyzing the conducted emissions from two different converters (step-down and flyback) which verified the connection between reverse recovery and increased emission levels.

- Demonstrating the dynamic behavior and performing an accurate analysis of the ingoing components in a switching converter. Passive components such as resistors and capacitors have been analyzed and their high frequency behavior has been modeled and simulated. Many semiconductor models available on the market have been analyzed and both advantages and deficiencies have been pointed out for the different models.

- The importance of using an adequate PCB model when predicting the conducted emissions in a switched converter has been demonstrated. This was done by implementing a 60W step down converter into Ansoft Q3D and co-simulating with an electric circuit software to obtain correct quantification of the ingoing parasitic elements.

- Determination and analysis of the mutual couplings for the ingoing components in a switching converter. The mutual coupling have been identified and implemented as a part of the complete converter modeling and the result points out that the mutual couplings must be taken into account if correct EMI levels are needed.

- Complete converter modeling (converter including input filter) with multi domain simulation software. The previous work regarding converter modeling that has been identified by the author has either been aimed at electric circuit simulations, FEM-calculations, the input and output filter, or a small part of a converter. This thesis aims to quantify the importance of including parasitic elements as well as mutual couplings in the input filter when the conducted emission levels are to be simulated.

## **1.5 Outline of Thesis**

The thesis starts with a background investigation of how all ingoing components in a switching converter can be modeled with respect to high frequency behavior and EMI. After that, a literature study of present work within both the field of switched converter modeling and the field of how to predict correct EMI behavior is presented. Also, a short overview of the causes of EMI within a switching converter and measures how to reduce disturbances is presented. Once the background theory is known, all models of the ingoing components are verified as standalone units; i.e. verifications of the high frequency behavior of resistors, inductors, capacitors, PCB traces and relevant semiconductors are presented. A new method of reducing EMI from a switched converter referred to as active gate control is investigated with both relevant background theory and measurements that verify the operation principle. The last chapter summarizes the previous analysis and of single components and investigate principles of how components interact, e.g. mutual couplings and how it affects filter performance. Furthermore, different complete converters act as a base to verify the previously stated theories.

## **1.6 Publications**

The publications originating from this thesis can be found in Appendix A and are summarized below.

I J. Paixão, A. Karvonen, J. Åström, T. Tuveson, and T. Thiringer, "EMI Reduction Using Symmetrical Switching and Capacitor Control" published at 2008 Asia-Pacific Symposium on Electromagnetic Compatibility in conjunction with the 19<sup>th</sup> Intern. Zurich Symposium on Electromagnetic Compatibility, Singapore, 2008.

II A. Karvonen, H. Holst, T. Tuveson, T. Thiringer, and P. Futane, "Reduction of EMI in SwitchedMode Converters by Shaped Pulse Transitions" published at SAEWorld Conference 2007. Detroit, Michigan, USA. Copyright SAE International, 2007.

A. Karvonen, "MOSFET Modeling Aimed at Minimizing EMI in Switched DC/DC Converters Using Active Gate Control," Institutionen för energi och miljö, Elteknik, Chalmers tekniska högskola, 2009.

A. Karvonen and T. Thiringer, "MOSFET Modeling Adapted for Switched Applications Using a State-Space Approach and Internal Capacitance Characterization " in PEDS 2009 - The Eighth International Conference on Power Electronics and Drive Systems, Taipei, Taiwan, R.O.C, 2009.

A. Karvonen and T. Thiringer, "On Dynamic Diode Characteristics and EMI Performance of an Inverter with Undeland Snubber," presented at: The 9th International Power and Energy Conference, Singapore, 2010.

A. Karvonen and J. Åström, "Simulating the EMI Characteristics of Step-Down DC/DC Converters," presented at the VPPC'2011, Chicago, IL, USA, 2011.

A. Karvonen and T. Thiringer, "Simulating the EMI Characteristics of Flyback DC/DC Converters," presented at the Intelec 2011, Amsterdam, Netherlands, 2011.

Chapter 1 - Introduction

## Chapter 2

# **Converter Components and Behavioral Models**

### 2.1 **Passive Components**

### 2.1.1 Wires and PCB Tracks

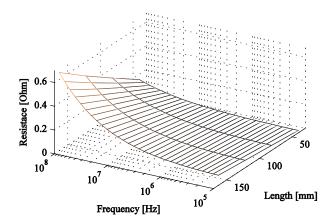

The conductors of a system are frequently overlooked being a part of a system since they often are assumed to be ideal connectors. If a wire carrying a high frequency current is considered, the current tends to crowd closer to the outer periphery, a phenomena known as skin effect. When the skin depth ( $\delta$ ) is less than the radius of a wire, it can be calculated as

$$\delta = \frac{1}{\sqrt{\pi f \mu_0 \sigma}} \tag{2.1}$$

where  $\mu_0$  is the permeability and  $\sigma$  is the conductivity of the conductor (5.96  $\cdot$  10<sup>7</sup>S/m for copper). For a circular copper wire excited with a 100 kHz current, the skin depth becomes 0.21mm which means that a high frequency current can only utilize a small fraction of the available conductor. If the wire is operating in the skin-effect region, the resistance can be calculated as

$$R_{(HF)} = \frac{1}{\sqrt{2r}} \sqrt{\frac{\mu_0}{\pi\sigma}} \sqrt{f}$$

(2.2)

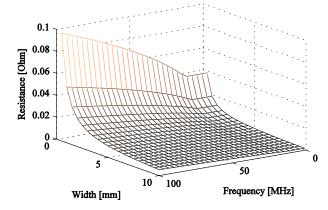

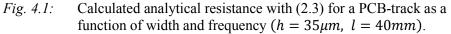

where r is the radius of the wire and f is the excited frequency. For a rectangular PCB-trace it is shown that when the skin depth ( $\delta$ ) becomes significant at  $\delta \cong h/2$ , the current crowds uniformly round the edges of the track [33] which gives that (2.2) can be simplified to

$$R_{\rm HF} = \frac{1}{2\sigma\delta(w+h)} \tag{2.3}$$

where  $\sigma$  is the conductivity of the conductor and w and h is the width and height of the PCB trace respectively.

For frequencies that concern EMI, the inductance of a conductor is often considerably more important than the resistance. The inductance of a wire can be divided into two parts; a frequency dependent internal inductance (50nH/m for low frequencies without influence from the skin effect [33]) due to storage of magnetic energy within the conductor and an external inductance due to the external flux created by the current in the conductor. As for the resistance, the internal inductance of a wire due to magnetic flux within the conductor becomes frequency dependent because of the skin effect. The current crowds towards the surface of the wire and hence the magnetic flux internally in the wire decreases toward zero as the frequency increases. The internal inductance is often relatively small compared with the external partial and mutual inductance which makes it reasonable to neglect in most cases [34].

The external inductance of a wire that comes from external magnetic fields is usually referred to as the partial inductance and can in turn be divided into two parts; self and mutual inductance. The partial self inductance comes from one segment of a wire due to external fields and for a straight length of a round section wire at high frequencies is can be expressed as

$$L_{\rm p(self)} = \frac{\mu_0}{2\pi} l \left[ \ln \left( \frac{2l}{r} \right) - 1 \right] \quad [{\rm H/m}] \tag{2.4}$$

where l is the length of the wire and r is the radius [35]. The self inductance of a normal connecting wire can be said to be 10nH/cm [33, 36] since the diameter of the wire affects the inductance only marginally. The mutual inductance arise due to interaction with the return current and if it needs to be considered, the geometry becomes important and the equations significantly more complex. An extensive explanation of the partial inductance concept can be found in [33].

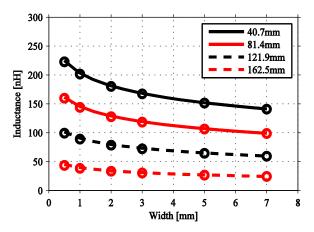

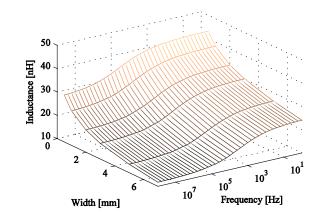

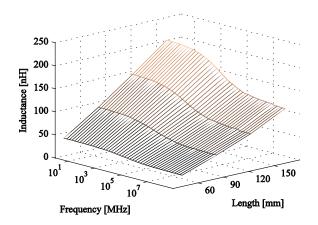

The same reasoning regarding internal and external inductance can also be applied for PCB-tracks. The calculation of internal inductance becomes significantly more difficult for a rectangular cross section, but since it once again is very small compared to the partial inductance it usually can be neglected. The external DC inductance of a PCB-track depends on the return path of the current; for a microstrip it can be calculated as

$$L = 0.2l \left[ \ln \left( \frac{2l}{w+h} \right) + 0.2235 \left( \frac{w+h}{l} \right) + 0.5 \right]$$

[nH] (2.5)

where l is the length of the microstrip, w is the width and h is the height over the ground plane [37]. As the equation tells, the inductance decreases as the width

increases and is almost directly proportional to the length of the strip.

If a conductor carries a sufficiently high frequency signal, it can no longer be treated as a simple conductor but must instead be treated as a transmission line; a rule of thumb states that when the wavelength of the highest frequency carried is less than ten times its physical length ( $L > \lambda/10$ ), transmission line theory must be considered. For a printed circuit board, the signal integrity is often discussed in terms of transmission lines where the conduction path usually consists of a microstrip or stripline. For a 30MHz signal traveling on a FR4 substrate, an inner layer conductor longer than 40cm needs to be considered as a transmission line. Transmission line theory is more aimed at high speed digital design and therefore not so applicable to the switching circuits investigated in this thesis. The interested reader can find an extensive explanation of how transmission line theory affects PCB design in [33, 35, 38].

In addition to PCB-parasitics, the package parasitics of a component also needs to be taken into account. Semiconductor manufacturers often state a well measured value for the lead inductance and resistance in their datasheets that works well for EMI-simulations, but the influence of skin-effect is often neglected in the given values. The package resistance has been shown to increase significantly with frequency and the package inductance will decrease due to the skin effect phenomenon. This phenomenon becomes even more significant for packages that attach the die with wire bonds (e.g. TO-220) where the package resistance can vary as much as 100% for a frequency increase from 500kHz to 4MHz [39]. The best way to reduce package inductance is to use flip-chip technology which connects semiconductor chips to external circuitry with solder bumps deposited directly onto the chip pads instead of traditional bond wires.

Even vias needs to be considered if correct high-frequency behavior of a PCB is needed. A significant amount of current can flow through via holes, especially high frequency currents from bypass capacitors, which give that parasitic effects may affect the behavior. The parasitic inductance of a via is based on its length and diameter and can be calculated as

$$L_{\rm via} = 0.129h \left[ \ln \left( \frac{4h}{d} \right) + 1 \right] \quad [nH] \tag{2.6}$$

where h is the height of the via and d is the diameter of the via in meters. The parasitic capacitance of a via is based on its length and the diameter of the pad surrounding the via and can be calculated as

$$C_{\rm via} = \frac{55.5\varepsilon_{\rm r}hd_{\rm p}}{d_{\rm c} - d_{\rm p}} \ [\rm pF]$$

(2.7)

where *h* is the height of the via,  $\varepsilon_r$  is the dielectric constant of the surrounding material,  $d_p$  is the diameter of the pad surrounding the holes and  $d_c$  is the diameter of the clearance hole. For EMI-modeling purposes, it can be sufficient to only consider the series inductance of the via, but if the via is carrying a high speed digital signal, a  $\pi$ -model with a series inductance and capacitors to ground on either side gives a more correct representation [40].

### 2.1.2 Resistive Components

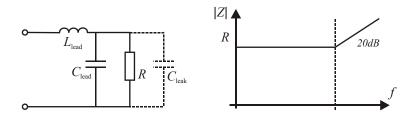

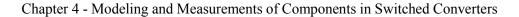

The ideal frequency response of a resistor has a magnitude equal to the value of the resistor and a phase angle of 0° for all frequencies. However, for an actual resistor the impedance will vary with frequency mainly due to the physical properties of the resistor. The origin of parasitics mainly lie in the construction of the resistor; a through-hole mount component shows both inductance and capacitance due to the leads attached to the component, see Figure 2.1 for an equivalent circuit and bode plot. For a 0.125W through-hole mounted resistor with 2cm lead length and 5mm lead spacing, the lead inductance is typically  $L_{\text{lead}} \approx 15nH$  and the lead capacitance is  $C_{\text{lead}} \approx 1pF$ . The bridging capacitance from end-to-end due to charge leakage around the resistor body is usually larger than the capacitive coupling between the leads, a reasonable estimation is that the total parasitic capacitance lies in the magnitude of 1pF which makes it reasonable to neglect in many cases [33].

*Fig. 2.1:* The nonideal resistor including effects of the leads.

Even for a surface mounted component with infinitesimally small contact electrodes, a parasitic capacitance within the resistive layer remains due to the potential drop and the field lines in the surrounding air. The parasitic self-capacitance and inductance for surface mounted resistors (size 2512 and smaller) are relatively small and lies in the range of hundreds of femtofarads [41, 42] and may therefore be neglected for the EMI simulation purposes in this thesis.

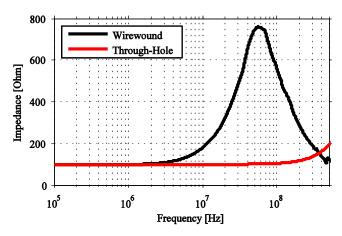

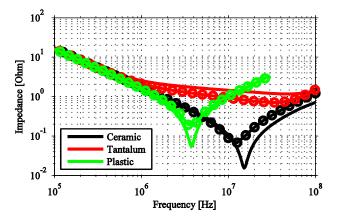

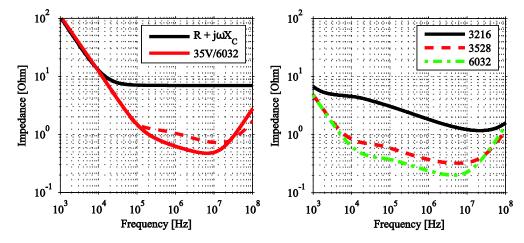

### 2.1.3 Capacitive components

There are many types of capacitors available on the market today, but in general are tantalum electrolytic and ceramic capacitors used for EMI suppression and aluminum electrolytes used for energy storage in low voltage applications. Ceramic capacitors have traditionally been modeled as a series RLC network

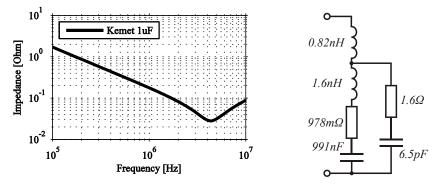

where the capacitor is described in terms of its capacitance, equivalent series resistance (ESR) and equivalent series inductance (ESL). This model works well for low frequency cases since the resistive element changes moderately with frequency and usually shows a minimum near the self-resonant point. The capacitance and ESL change is also very small at frequencies below self-resonance [43]. These assumptions work well for moderately high ESR capacitors with a low Q and when a capacitor is mounted on pads that dominate the ESL. But as the frequency goes up, the inductance associated with the height of the capacitor causes current to closer to the connectors, i.e. lower down in the capacitor. A smaller part of the capacitor carries most of the current which results in higher ESR. The current stays closer to the return current in PCB power planes leading to lower inductance. The Q of the capacitor and the anti-resonant peak is reduced at high frequencies by this effect. A distributed circuit SPICE model, captures this effect [44] and variants of this model is used by manufacturers such as Kemet and Murata, see Figure 2.2 for the Kemet SPICE model.

*Fig. 2.2:* A nonideal ceramic capacitor model with corresponding impedance as function of frequency for Kemet C1210C105K3RAC.

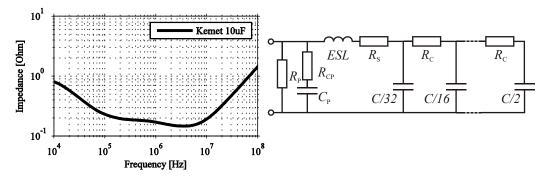

The capacitance of a tantalum capacitor usually shows a large frequency variation; a decay of 20% of decade per frequency is common. The electrode that penetrates the tantalum block within the capacitor have limited width but must yet penetrate to the center of the capacitor to electrically connect the deepest capacitive elements. The deeper the penetration, the higher becomes the resistance of that path. As frequency increases, the period for each capacitor element to respond and contribute to the total capacitance decreases; starting at the center and working out towards the surface, more and more capacitive elements are unable to make any contribution to the total capacitance. This electrical presentation of this phenomenon can be seen in Figure 2.3 where the capacitance increases with increasing resistance. The capacitance available to the circuit at higher frequency is all located near the outer surface of the anode [43]. A similar approach where the capacitance roll-off is implemented by exponentially decreasing the capacitance together with a constant resistance value seems to work well also for aluminum electrolytic capacitors [45].

Chapter 2 - Converter Components and Behavioral Models

*Fig. 2.3:* A nonideal tantalum capacitor model with corresponding impedance as function of frequency for Kemet T494D106M035AT [43].

### 2.1.4 Inductive components

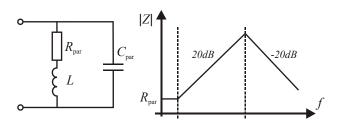

The parasitic components of an inductor are more complex than the ones for a capacitor due to its relatively complex design with many parasitic elements. Inductors are generally made by winding a wire around a magnetically permeable material and it is the performance of the magnetic material, along with the DC-resistance of the wire and the stray capacitance caused by the winding technique that determines the overall performance of the component. A simplified equivalent circuit of the inductor can be seen in Figure 2.4.

*Fig. 2.4:* A simplified equivalent circuit of an inductor.

Several studies of different inductor modeling aspects have been performed, e.g. has the frequency dependent losses been analyzed with a Jiles-Atherton model in [46, 47], the leakage inductance in [48] and the self capacitance of the windings in [49, 50]. From an EMI point of view, the most interesting work is performed in [51, 52] which in combination with a Jiles-Atherton model gives a comprehensive coverage of all aspects of a magnetic component.

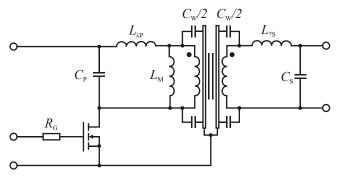

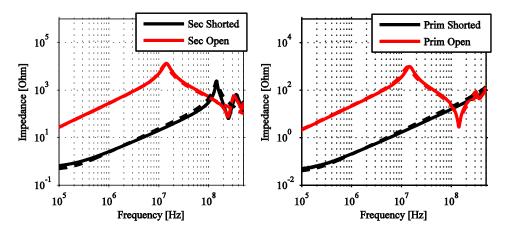

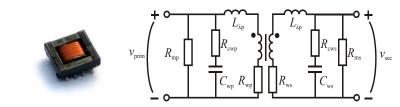

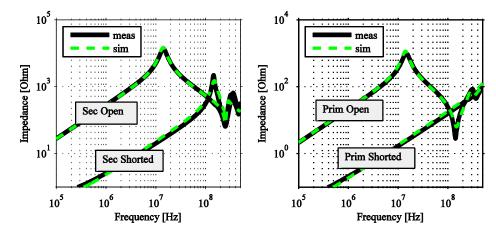

Tihanyi [53] states that for a switched converter with a transformer, one of the primary sources of harmonics in the output are the stray component in a transformer; an equivalent circuit is shown in Figure 2.5. The interwinding capacitance,  $C_W$ , can cause common mode emissions and can be decreased by applying a faraday shield between the windings, see Figure 2.5. The intrawinding capacitances,  $C_P$  and  $C_S$ , are small and can in some cases be neglected. The last

2.1 - Passive Components

parameter that needs to be accounted for is the leakage inductance of the primary and secondary winding,  $L_{\lambda P}$  and  $L_{\lambda S}$ , respectively, which create a magnetic field between the windings. While some of this field is captured by the core, the rest acts as a magnetic dipole radiating out into surrounding space and may induce disturbances on nearby components. Examples of techniques for reducing the leakage inductance is interleaving the windings or by applying a conductive flux strap that provides a path for the eddy currents that result from the leakage inductance.

*Fig. 2.5:* Equivalent circuit of a transformer.

Another parameter that in some cases must be accounted for is ferrite core stray capacitance that for lower frequencies can become a significant part of total stray capacitance. Hence, the winding arrangement may not play a significant part in low frequency common mode current generation but it may rather originate from the ferrite core stray capacitance [54].

In many modern converters, the use of planar transformers becomes more and more common due to three reasons; the possibility of achieving high power density, repeatable parameters from a production point of view and lowered leakage inductances. The leakage inductances are reduced by interleaving the primary and secondary layers so that the stray magnetic flux induced by the eddy currents is canceled [55]. However, a planar transformer has the disadvantage of increased intrawinding parasitic capacitances and increased interwinding capacitance. The increase of these capacitances gives rise to higher differential mode and common mode noise magnitude, respectively, as shown in [56].In addition to this, planar technology gives the possibility of integrating a complete EMI-filter into one component [57].

### 2.1.5 Mutual Coupling between Components

The last part that needs to be taken into account in order to obtain a correct EMIsignature is the electromagnetic coupling between the components in the converter. These effects especially raise influence, when parts of a circuit carry high interference levels while parts close by carry low level signals. In case of

filter circuits this condition is valid and magnetic coupling coefficients between components as low as 0.1% already dominates circuit behavior [22].

The electromagnetic coupling between two electrical circuits can be said to originate from either an inductive or a capacitive coupling between the circuits. The effect of induction fields can be minimized by usage of proper spacing and coupling angle between wires; the degree of magnetic coupling diminishes rapidly with distance and the angle between the conductors approach a right angle. In the same way, the strength of the capacitive coupling depends on the geometry between the victim and the source; it is indirectly proportional to the distance between the source and the victim, the geometry of the objects and to the permeability and permittivity of the material between the circuits.

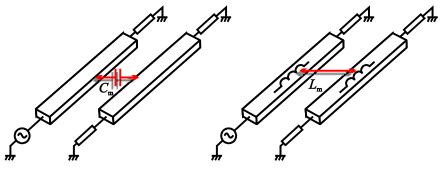

Figure 2.6 illustrates the difference between the two coupling mechanisms applied to two transmission wires, but due to the complex geometries of most real life problems, it is in general hard to determine which coupling mechanism that dominate [33]. However, for some cases it can be obvious which mechanism that dominate, e.g. two large PCB-planes separated by a small distance with a high permittivity dielectric material will give rise to a large parasitic capacitance.

*Fig. 2.6:* Different forms of cross-talk between wires.

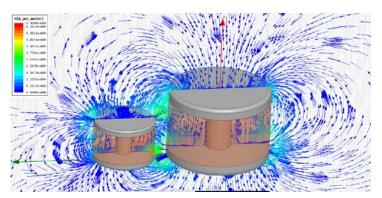

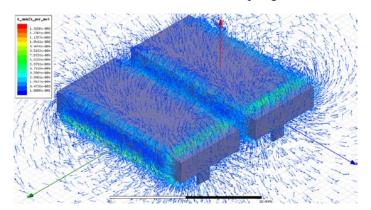

The effect of magnetic and electric field coupling can more accurately be calculated using FEM-calculation software, in this thesis are Maxwell and Q3D from Ansoft used as the primary tools. Figure 2.7 shows an example of a magnetostatic solution of two neighboring DC-excitated coils; due to the closeness of the coils, the *B*-fields will interact with each other. Figure 2.8 shows a similar case but for an electrostatic solution of two DC-excitated capacitors. Note that for practical applications, capacitors and conductors can generally be said to be the same from a mutual coupling point of view. Both components often carry high frequency AC-currents which generate a high magnetic field that couples to surrounding components. The external electric fields that are generated by capacitors are generally relatively low and capacitive coupling due to electric fields are more likely to occur between closely located neighboring structures such as PCB planes or heat sinks.

#### 2.2 - Semiconductors and Materials

*Fig. 2.7:* FEM-visualization of mutual *H*-field coupling between two inductors.

Fig. 2.8: FEM-visualization of mutual E-field coupling between two capacitors.

In order to account for mutual couplings in electric circuit simulation software, it requires on one hand the calculation of the electromagnetic fields within a circuit, and on the other hand circuit simulation based on these values. Since mutual couplings can affect the properties of components, e.g. the inductance of a filter inductor, these effects also needs to be taken into account in the circuit simulation.

## 2.2 Semiconductors and Materials

Most modern semiconductors are at the point of writing this thesis still manufactured by silicon that has a non-negligible deficit when large powers are to be handled; a considerable wafer thickness is needed to achieve sufficient voltage handling capability. Since the thickness of the semiconducting material is the most important factor that contributes to the overall losses in the device, the possibility to use a thin wafer would strongly evolve power semiconductors even further. Recent research has showed that new materials such as silicon carbide (SiC) and gallium nitride (GaN) has substantially improved material properties in relation to silicon. Recent development has recently made silicon carbide Schottky diodes available on the market and prototypes of both bipolar transistors and field effect transistors have been presented. But due to the relatively early

stage in the development of these materials, several problems must still be mastered before other components can be produced in larger volumes [58].

## 2.3 The Diode

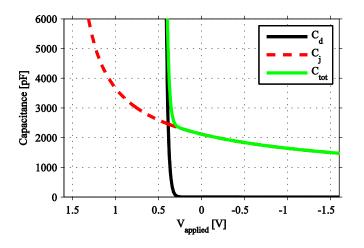

The simplest form of diode is formed when a *p*-doped material and an *n*-doped material is brought together to a *pn*-junction. Since electrons are moved within the crystal lattice both due to the influence of the applied electric field and due to the charge that is stored in the diode when it is forward biased, the diode can also be seen as a capacitor. The total diode capacitance,  $C_D$ , consists of two terms; the depletion capacitance ( $C_j$ ) and the diffusion capacitance ( $C_d$ ). The depletion capacitance originates from the accumulation of charges in the space charge region and its varying width and the diffusion capacitance is the capacitance due to transport of charge carriers through the *pn*-junction when the component is forward biased. [58].

### 2.3.1 The PiN-Diode

A regular pn-diode is often made of a highly p-doped material and an n-type epitaxial substrate. A highly p-doped material needs lower ionization energy before avalanche breakdown occurs which makes  $p^+n$ -junctions more suitable for higher currents since the power losses in the material approximately increases with the square of the device thickness. To overcome the problem with high contact resistance between metallic contacts and lowly doped n-layers, a highly doped  $n^+$ -region is added to the structure. When such a device is forward biased, the middle region  $(n^-)$  is driven into high injection, i.e. the  $n^-$ -region becomes flooded with a quasi-neutral mixture of charged particles, a so called plasma; hence the acronym PiN (where i stands for intrinsic).

For a regular pn-junction diode, the voltage drop is equal to the junction voltage which can be regarded as a constant voltage. However, in high power PiN-diodes, this approximation will seriously underestimate the losses since it does not comprise the power dissipation in the drift region. This power dissipation is minimized by conductivity modulation caused by injection of minority carriers in the drift region that lowers the conduction losses. By making the carrier lifetime large enough, the on-state losses can be reduced. However, a long carrier lifetime reduces the switching speed due to the stored charges in the drift region; the characteristics of a PiN-diode are often an optimization between switching speed and on-state losses.

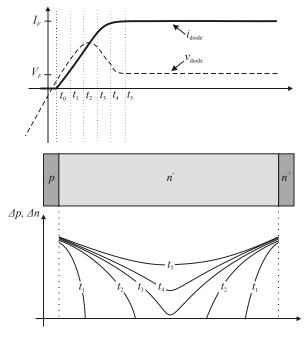

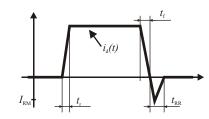

When a PiN -diode is turned on, the forward current starts to increase from zero with a rate of  $di_F/dt$ , see Figure 2.9. The current flow causes excess carriers to be injected into the intrinsic region from the  $n^+n^-$  and  $p^+n^-$  junctions where they

eventually diffuse into the middle. Initially, the ohmic losses in the intrinsic region are rather large due to the lack of injected excess carriers but as the diffusion process continues, the resistivity diminishes and approaches the value for the steady state current. This increased resistance causes an overshoot in the forward diode voltage usually referred to as forward recovery. Note that the maximum overshoot is dependent on the rate of current increase,  $di_F/dt$ ; a higher derivative gives a larger overshoot both due to parasitic inductances in the package and to the resistive drop [59].

*Fig. 2.9:* Turn on-process for a *PiN*-diode.

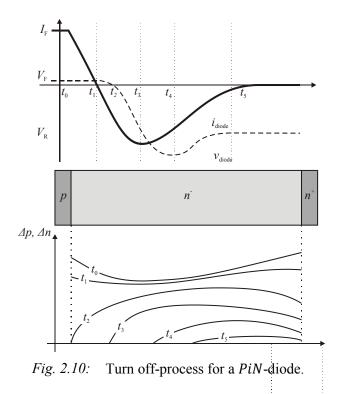

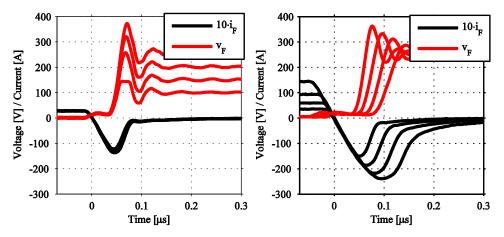

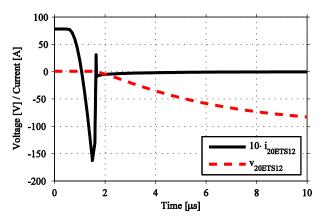

The transient process during turn-off for a *PiN*-diode that is hard switched (i.e. the diode is used as a freewheeling diode where the current momentarily is switched from the load to the diode) is shown in Figure 2.10. At  $t = t_0$ , the voltage over the diode changes polarity from forward to negative bias momentarily. During phase 1 ( $t_0$  to  $t_1$ ) the drop in diode current is very fast which gives that this phase is very short compared with the recombination lifetime. Therefore, as phase 1 is completed and the current crosses zero, the plasma concentration in the intrinsic region is still high.

During phase 2 ( $t_1$  to  $t_2$ ) the excess carrier concentration in the intrinsic region keeps the diode conducting. The diode current derivative remains constant which gives a small voltage drop over the diode. The reverse current in the diode is supported by sweepout of excess carriers from the intrinsic region. Electrons are swept out via the cathode contact and holes exit via the anode contact which gives a rapid decrease in carrier concentration close to the edges in the  $n^-$ -region.

During phase 3 ( $t_2$  to  $t_3$ ) the plasma concentration falls to zero at the  $pn^-$ -junction due to the fact that the initial plasma concentration is much lower at the anode than at the cathode. As the plasma concentration falls to zero, a depletion layer starts to form which also supports a voltage. Af  $t = t_3$ , the voltage across the diode reaches  $V_R$  and the current derivative reaches zero.

During phase 4  $(t_3 \text{ to } t_4)$  the plasma concentration continues to decrease. The excess charge carrier concentration at the edges of the space charge region that supports the entire voltage in the diode must consequently also continue to decrease. As a consequence, the reverse current starts to decrease after  $t = t_3$ . As a reaction to the negative di/dt, the stray inductances in the circuit builds up an electromotive force that results in a voltage overshoot over the diode.

During phase 5 ( $t_4$  to  $t_5$ ) the depleting plasma in the intrinsic region gives a continued current drop towards zero [58].

#### 2.3.2 The Schottky Diode

The Schottky diode is manufactured by joining a metal and a semiconducting material together, see Figure 2.11. This gives rise to a dipole charge on the surface of the junction and the interface will show a similar behavior as a pn-junction. A Schottky diode is a majority-carrier device since only majority-carriers (most commonly electrons) are used when it conducts. This is a major difference

compared with a regular pn-diode since the pn-diode uses both majority and minority carriers for the basic function.

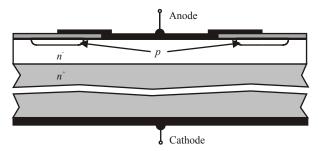

A Schottky diode is commonly made by evaporating a suitable metal onto the surface of an  $nn^+$ -epitaxial structure. Figure 2.11 shows the physical structure of a Schottky diode with a guard ring that increases the blocking voltage capability. The main purpose of the guard ring is to reduce the curvature of the depletion layer from the metal-semiconductor interface and to widen the space charge region at the semiconductor surface.

*Fig. 2.11:* Schematic structure of a Schottky diode with guard ring for higher blocking voltage ability.

The main advantages of power Schottky diode is low forward voltage drop, temperature and good switching characteristics. However, due to material properties of the Schottky structure, the reverse blocking voltage of silicon Schottky diodes are somewhat limited. With proper material selection and field terminations (a *p*-region surrounding the metallic contact) the blocking voltage can reach up to 250V. Also, the reverse leakage current is higher for a silicon Schottky diode compared to a *pn*-diode with the same physical structure [59]. Schottky diodes made of silicon carbide have recently been introduced on the market and several manufacturers now offer SiC Schottky diodes with blocking voltages up to 1200V. The SiC Schottky diode offer good switching characteristics and low thermal influence on its switching characteristics which makes it worth considering in e.g. high temperature applications.

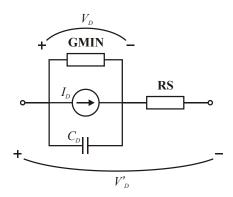

#### 2.3.3 Diode Modeling

The simplest semiconductor modeled in SPICE is the *pn*-junction diode. Originally, it is based on the well known Shockley equation

$$I_{\text{diode}} = I_{\text{S}} \left[ exp\left( \frac{V_{\text{D}}}{N \cdot V_{\text{t}}} \right) - 1 \right]$$

(2.8)

that describes the current through an ideal diode. In (2.8),  $I_S$  is the saturation current,  $V_D$  is the applied voltage over the diode and  $V_t$  is the thermal voltage. For

adaptation to SPICE, an emission coefficient, N, is introduced to model the ideality of the pn-junction; a high value indicates on a higher rate of recombination of carriers in the depletion layer.

In addition to the description of the current characteristics, a series resistance (RS) is often added. The purpose of the resistance is to model the resistance in the connecting wires, the ohmic contact resistances and the ohmic drop in the quasi neutral regions. In order to obtain a better dynamic model, the diode capacitance is added to the model, see Figure 2.12 for a circuit representation.

Fig. 2.12: SPICE Diode large signal model with dynamic effects.

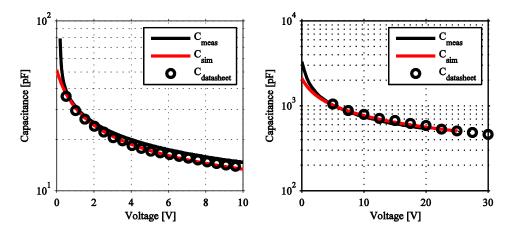

As the physical interpretation of the diode capacitance suggests, the total diode capacitance,  $C_D$ , can be divided in two parts; the diffusion capacitance,  $C_d$ , and the depletion capacitance,  $C_i$ . SPICE interprets the depletion capacitance as

$$C_{\rm j} = \frac{C_{\rm j}(0)}{\sqrt{1 - \frac{v_{\rm applied}}{V_{\rm bi}}}}$$

(2.9)

where  $V_{applied}$  is the applied junction voltage,  $C_j(0)$  is the junction capacitance at zero applied bias and  $V_{bi}$  is the built-in voltage which equals the potential difference between the *p*-material and the *n*-material at zero bias. The diffusion capacitance is according to Massobrio [60] modeled as

$$C_{\rm d} = \frac{dQ_{\rm d}}{dV} = \frac{TT \cdot I_{\rm S} \cdot e^{\frac{v_{\rm applied}}{NV_T}}}{N \cdot V_{\rm T}}$$

(2.10)

where *N* is the diode ideality coefficient found in (2.8) and *TT* is a SPICE parameter that describes the transit time for the carriers. If these two capacitances are plotted for the SPICE model for the diode 32CTQ030, the results in Figure 2.13 is obtained. When the applied voltage becomes positive and approaches the defined value for the diode ( $V_{\rm bi} = 1.5V$ ), the space charge region becomes very

thin which enables a current flow. The applied voltage at which the current starts to flow coincide with the specified forward voltage drop at rated current,  $V_F = 0.4V @ I_F = 15A$  according to the manufacturer datasheet. Consequently, the depletion capacitance will be the dominating part under forward bias.

*Fig. 2.13:* Internal capacitances as a function of applied voltage for 32CTQ030.

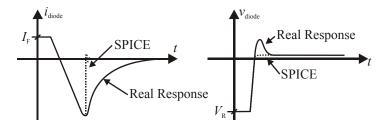

It has been shown in [61] that the excess carrier distribution profile in the vicinity of the *pn*-junction as the diode is being turned-off depends on the rate of change of the stored charge. If a low dQ/dt is present in the diode, the quasi-static charge equation is adequate since the stored charge in the depletion region also becomes approximately zero as the charge in the node at the interface becomes zero. However, if a high dQ/dt is present, a substantial amount of stored charge still remains in the depletion region even though the charge concentration at the interface has decreased to zero. It is this excess charge that causes the behavior of the reverse recovery current.

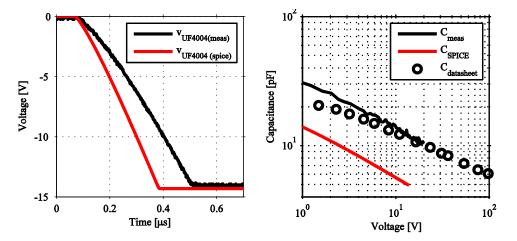

Charge storage in the depletion layer is not modeled by SPICE, hence the sudden increase and snappy behavior of the diode current at the moment when the charge node at the interface becomes depleted, see Figure 2.14 for a comparison between SPICE and real turn off behavior.

To summarize, the basic SPICE model provides a good modeling of the static diode behavior but it has two major deficits; it does not take high level injection into consideration and it does not include dynamic effects such as forward and reverse recovery. Numerous more advanced models that take high injection into consideration have been developed, see e.g. [60, 62, 63].

*Fig. 2.14:* Comparison of typical reverse recovery waveforms from SPICE and a real diode.

Regarding PiN-diode modeling, the SPICE diode model becomes even more inadequate due to the intrinsic region. For this reason, several modeling techniques have been proposed over the years, an extensive summary is presented in [64]. As described by Lauritzen and Ma, a model of the *PiN*-diode can be derived using the lumped charge technique [65-67]. In a *PiN*-diode driven into high injection, reverse recovery is caused by diffusion of charge from the *i*-region which can be modeled by additional charge storage nodes. The main deficits with the lumped charge model presented by Lauritzen are the parameter extraction procedure and the possibility of implementation in a circuit simulator.

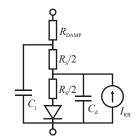

To overcome this, some of the major simulation software manufacturers, e.g. Synopsys and Ansoft, have developed their own models that incorporate more correct switching characteristics. The diode model incorporated in SABER by Synopsys is presented in [68] and referred to as the unified diode model. The detailed implementation is intellectual property of Synopsys Inc. and not free to distribute, but a complete description of the validation procedures can be found in [69] and for the end user the Power Diode Tool® within the software SABER® Sketch is used for graphical parameter extraction. The last diode model investigated in this thesis is the model in Simplorer. The forward characteristics of the diode is modeled by the Shockley equation and in addition to the static behavior, junction and diffusion capacitance are also taken into account together with an additional current source that accounts for the reverse recovery, see Figure 2.15. The shape of the reverse recovery current is determined by several user defined form factor-parameters [70].

Fig. 2.15: Equivalent diode model in Simplorer.

#### 2.3.4 Modeling of the Schottky Diode

The current through a Schottky diode can in a similar way as the regular pn-diode be modeled with (2.8). The main difference is that the saturation current  $I_s$  is not dependent on doping levels and diffusion length as for the pn-diode, but rather on the Schottky barrier voltage. As far as the large-signal model is concerned, the charge storage effects are almost entirely dominated by the depletion capacitance,  $C_j$ , see (2.9). The fact that the forward current is characterized by electron emission from the n-type semiconductor into the metal rather than hole injection into the semiconductor results in negligible minority carrier effects, hence can the diffusion capacitance,  $C_d$ , be neglected [60].

Even though a model for the Schottky diode is not implemented explicitly in SPICE, it can be simulated sufficiently good with the regular *pn*-diode model by adjusting the saturation current, *IS*, and setting TT = 0, see (2.8) and (2.10).

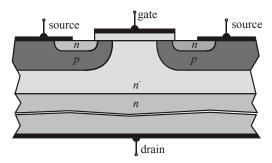

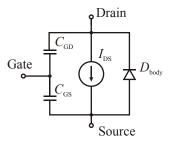

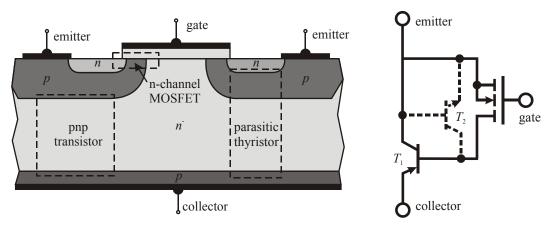

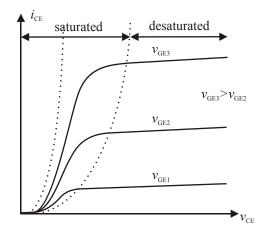

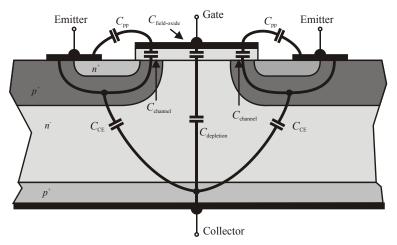

# **2.4 The MOSFET**

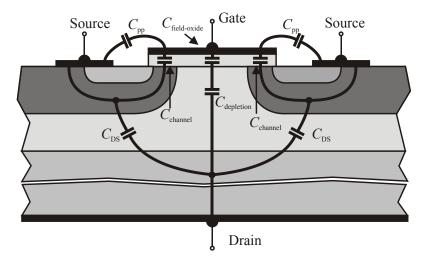

For switching power electronic applications, the vertically diffused double MOSFET (VDMOS) transistor is exclusively used, see Figure 2.16 that show a *n*-channel VDMOS device. The geometry lowers the on-state resistance  $R_{DS(on)}$ , reduces the lateral size of the component and gives the possibility to parallel several elements on the same wafer which lowers the conduction losses even further [58].

Fig. 2.16: Schematic structure of a vertically diffused MOSFET

An unwanted feature of the most common MOSFET structure is the presence of a body diode. To reduce the risk of turning on the parasitic BJT-transistor, the metallic source electrode that covers the  $n^+$ -region is lengthened to also cover the body region in order to obtain a short-circuited base connector on the BJT. The performance of the body diode is relatively slow compared with the MOSFET and if used in a switched converter it can cause high peak currents during diode turn off [71]. Several measures can be taken in order to improve the performance of the diode and to make it more suitable for switched applications [58, 72, 73].

Chapter 2 - Converter Components and Behavioral Models

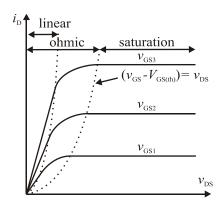

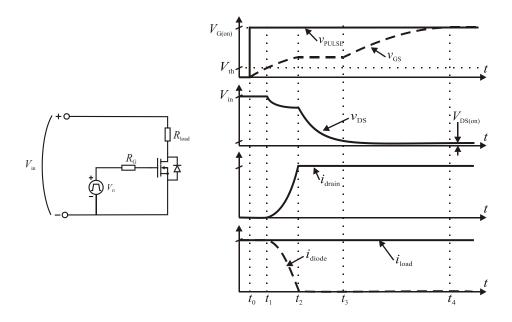

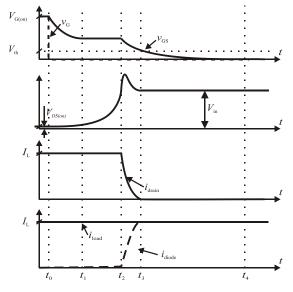

As the gate-source voltage reaches above the threshold voltage, a strong inversion layer starts to form in the *p*-material which gives a free path for the current to flow from drain to source. The created inversion channel acts like a resistor, i.e. the drain current is proportional to the applied drain voltage. The MOSFET is said to be operating in the linear region; i.e. the drain current is proportional to the applied gate-source voltage. Figure 2.17 shows the current voltage characteristics for an ideal VDMOS transistor.

Fig. 2.17: Output Characteristics of a vertically diffused MOSFET

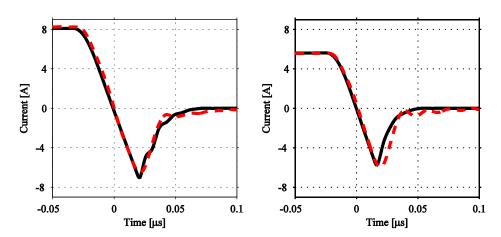

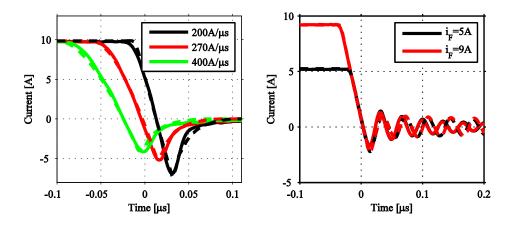

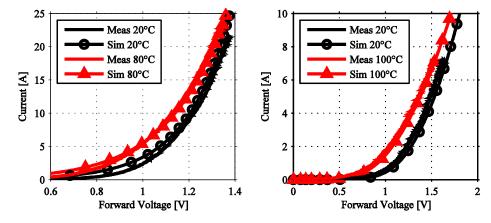

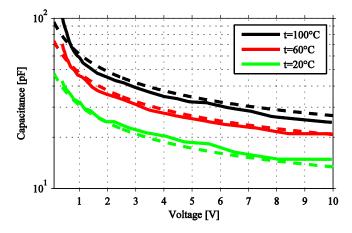

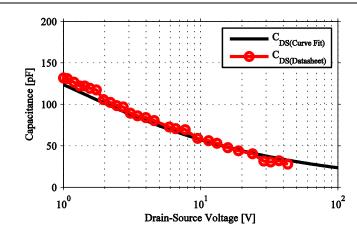

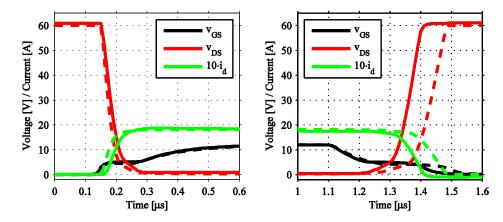

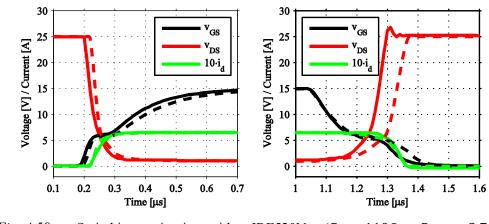

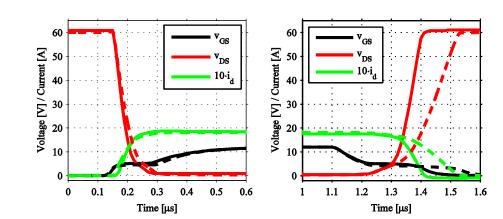

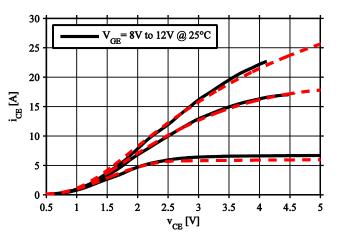

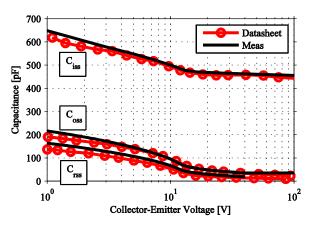

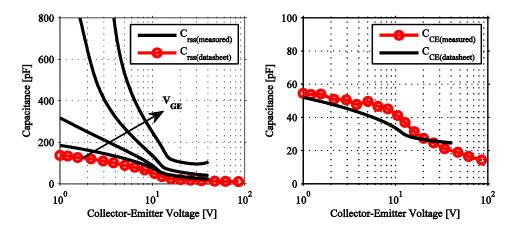

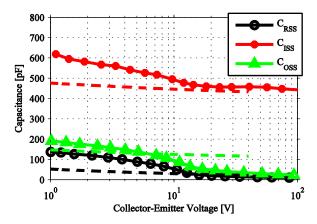

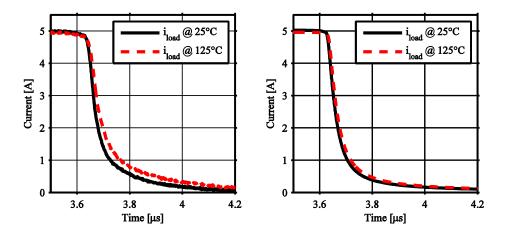

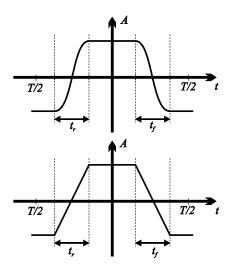

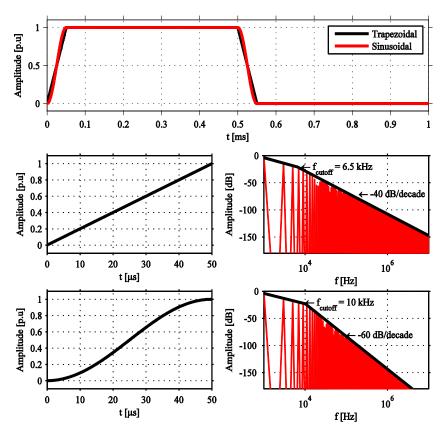

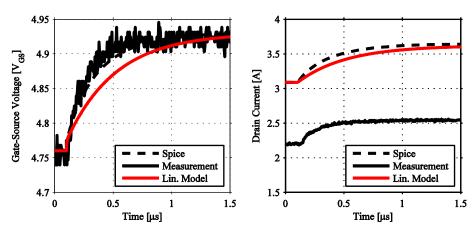

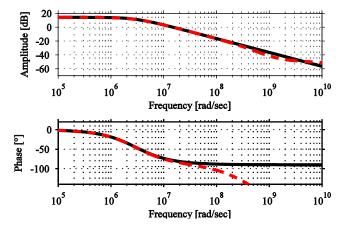

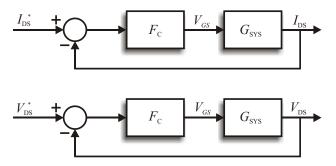

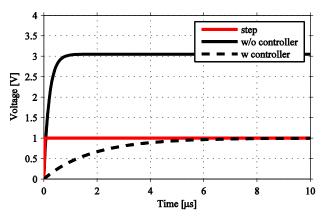

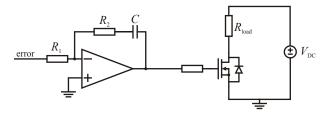

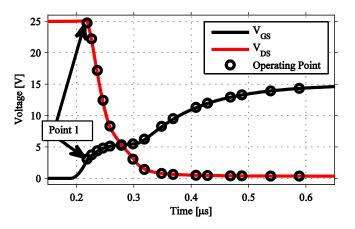

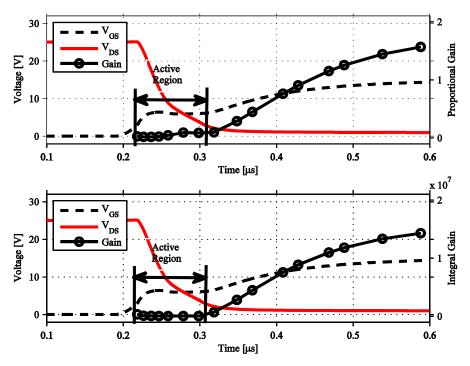

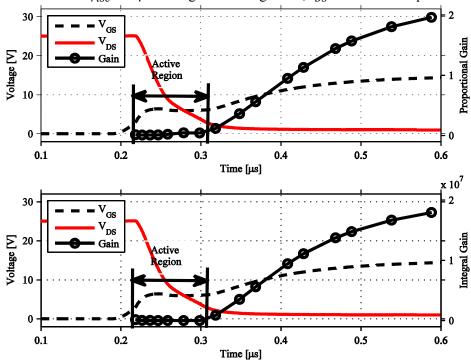

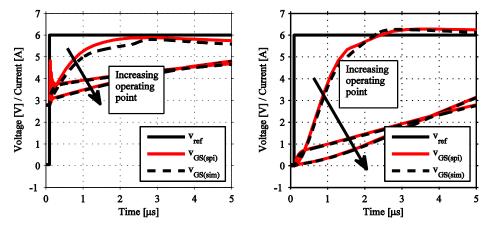

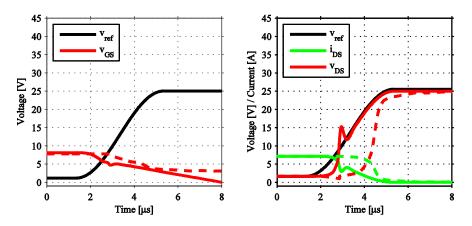

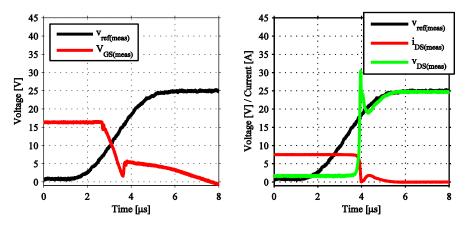

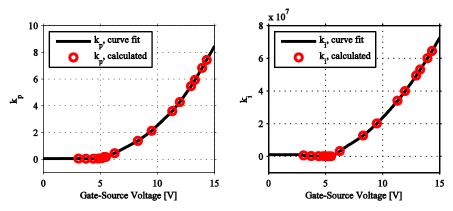

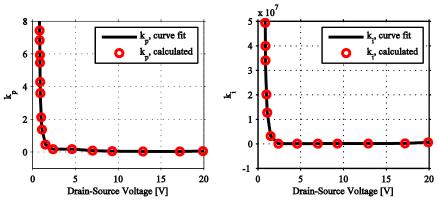

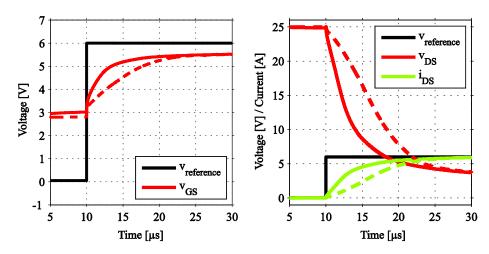

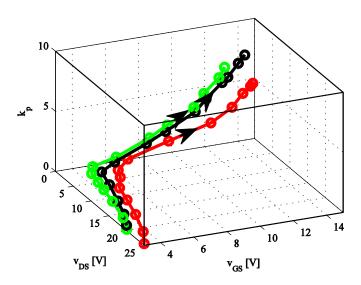

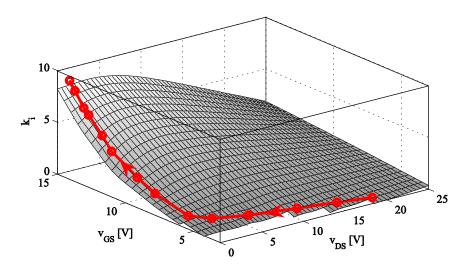

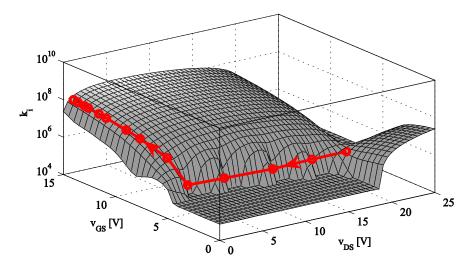

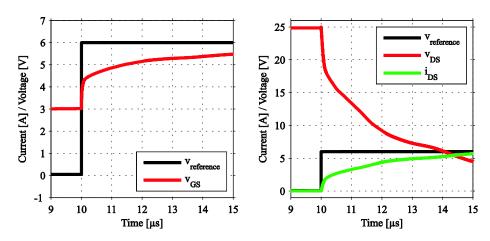

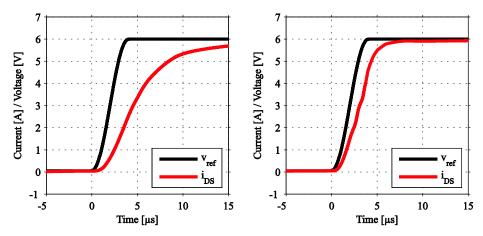

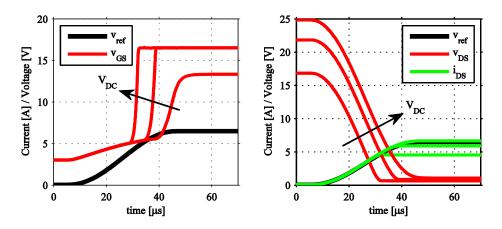

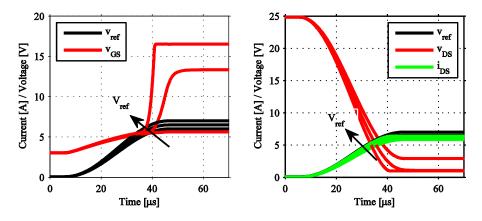

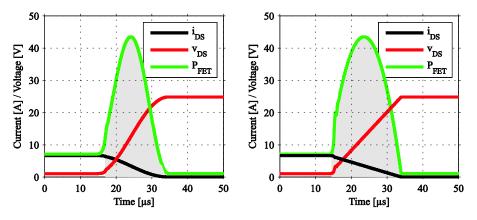

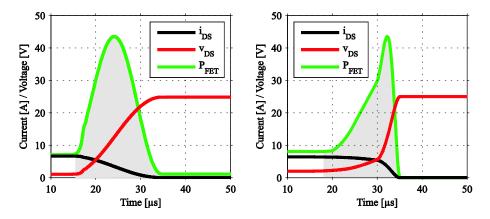

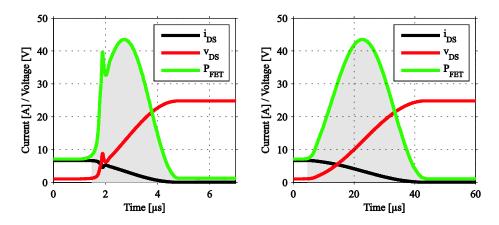

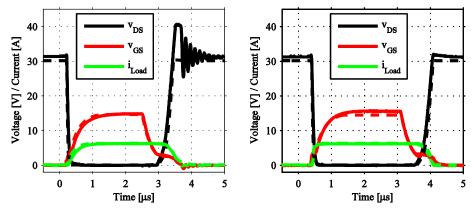

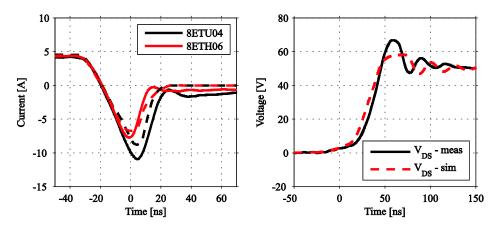

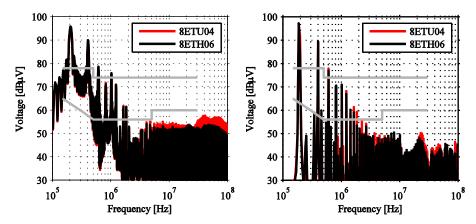

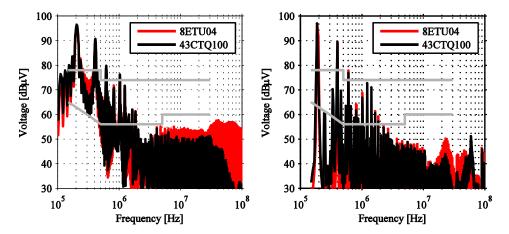

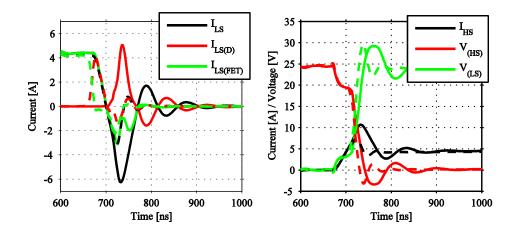

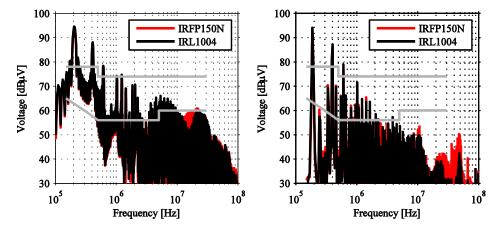

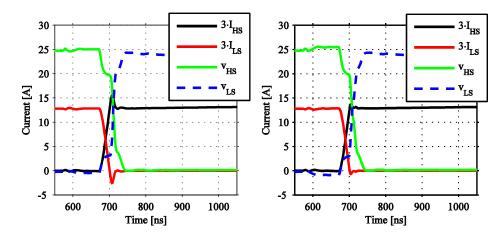

If the drain-source voltage is increased from a low value, the potential at the drain is no longer negligible compared to the gate voltage. Along the formed channel the voltage potential is successively decreasing. The new reduced potential at the drain end of the channel gives a decreased inversion charge and consequently also a reduced channel width. This reduction in channel width produces the concave curvature in the ohmic region in Figure 2.17.