# CHALMERS

Master of Science Thesis in Integrated Electronic System Design

## Vineeth Saseendran Donatas Siaudinis

VLSI Research Group Division of Computer Engineering, Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden, 2010 The Authors grants to Chalmers University of Technology the non-exclusive right to publish the Work electronically and in a non-commercial purpose make it accessible on the Internet. The Authors warrants that he/she is the author to the Work, and warrants that the Work does not contain text, pictures or other material that violates copyright law.

The Authors shall, when transferring the rights of the Work to a third party (for example a publisher or a company), acknowledge the third party about this agreement. If the Authors has signed a copyright agreement with a third party regarding the Work, the Authors warrants hereby that he/she has obtained any necessary permission from this third party to let Chalmers University of Technology store the Work electronically and make it accessible on the Internet.

Power Gating of the FlexCore Processor

Vineeth Saseendran and Donatas Siaudinis

© Vineeth Saseendran and Donatas Siaudinis, June 2010.

Examiner: Per Larsson-Edefors

VLSI Research Group

Department of Computer Science and Engineering

Chalmers University of Technology

SE- 412 96, Göteborg,

Sweden

Supervisor: Tung Thanh Hoang

VLSI Research Group Department of Computer Science and Engineering Chalmers University of Technology SE- 412 96, Göteborg, Sweden

Department of Computer Science and Engineering Göteborg, Sweden,

## Abstract

The aim of this master thesis work is to reduce the leakage power of the FlexCore processor by applying one of the most effective leakage reduction techniques, power gating. The main principle of this technique is inserting transistors named power switches, to cut off voltage supply of the functional units when they are not in use. In the context of this thesis, multiplier unit of the FlexCore processor, a novel architecture for embedded systems, is selected to be power gated. This is because, initial studies show that the multiplier, due to its relatively large size and significant idle time leads to it being a major contributor to the leakage power dissipation. A process of applying power gating onto the FlexCore's multiplier is divided into two parallel branches, software analysis and hardware implementation, and concluded in an integration phase. The software analysis phase, using FlexTools tool-chain, involves profiling of two EEMBC benchmarks and extending of the Native Instruction Set Architecture (N-ISA) to adopt control bits that are enable to activate or deactivate the multiplier unit on demand. The hardware implementation phase focuses on the implementation of the power gating technique by using power specification which is defined in the Common Power Format (CPF) at both RTL level and physical level. In the final phase, the extended N-ISA instruction is applied on the FlexCore processor with power gated multiplier unit to estimate the power reduction at a small area cost. During the physical implementation phase, the optimal power savings were estimated taking in to account the overhead from the switches. For the two examined benchmarks, energy efficiency was shown in range of 4-14%. In real applications, the multiplier is less active than in the benchmarks considered here and thus, it is possible to achieve higher energy reduction.

# **Table of Contents:**

| Abstra   | ct                                                       | 3  |

|----------|----------------------------------------------------------|----|

| Table of | of Contents:                                             | 4  |

| List of  | Figures:                                                 | 5  |

| List of  | Tables:                                                  | 6  |

| List of  | Abbreviations                                            | 9  |

| Tools a  | and Technology                                           | 10 |

| 1. In    | troduction                                               | 11 |

| 1.1      | Motivation                                               | 12 |

| 2. Po    | ower Reduction                                           | 14 |

| 2.1      | Power Dissipation in CMOS Circuit                        | 14 |

| 2.2      | Power Reduction Techniques                               | 16 |

| 3. Flo   | exCore Processor                                         | 19 |

| 3.1      | Background                                               | 19 |

| 3.2      | Baseline Architecture of the FlexCore                    | 19 |

| 4. Po    | ower Gating for the FlexCore Processor                   | 21 |

| 4.1      | Power gating the Multiplier                              | 24 |

| 5. So    | oftware Analysis                                         | 27 |

| 5.1      | FlexSoC Tool-chain                                       | 27 |

| 5.2      | EEMBC Benchmark                                          | 28 |

| 5.3      | Localization of the Multiplier Function                  | 29 |

| 5.4      | Tools Chain                                              | 30 |

| 5.5      | Evaluation of Multiplier Behaviour                       | 31 |

| 5.6      | N-ISA Extension for Power Gating                         | 38 |

| 6. Ha    | ardware Implementation                                   | 40 |

| 6.1      | Common Power Format                                      | 40 |

| 6.2      | RTL Design and Synthesis                                 | 43 |

| 6.3      | Power Control Module                                     | 46 |

| 6.4      | Physical Implementation                                  | 48 |

| 7. Re    | esults and Analysis                                      | 52 |

| 7.1      | Power Reduction Estimation after RTL Synthesis           | 52 |

| 7.2      | Power Reduction Estimation after Physical Implementation | 55 |

| 8. Co    | onclusion & Future Work                                  | 64 |

| 9. Bi    | bliography                                               | 65 |

| Appen    | dix – A: Software Analysis Makefile                      | 66 |

| Appen    | dix – B: FlexCore CPF                                    | 68 |

| Appen    | dix – C: Power Control Module                            | 71 |

|          |                                                          |    |

# **List of Figures:**

| FIGURE 1.1: TREND OF DYNAMIC AND LEAKAGE POWER FOR GENERAL PROCESSORS                   | 11 |

|-----------------------------------------------------------------------------------------|----|

| FIGURE 1.2: EFFECTS OF DIFFERENT POWER REDUCTION TECHNIQUES.                            | 12 |

| FIGURE 3.1: MULTIPLIER-EXTENDED FLEXCORE PROCESSOR                                      | 20 |

| FIGURE 3.2: FLEXCORE N-ISA INSTRUCTION                                                  | 20 |

| FIGURE 4.1: HEADER AND FOOTER SWITCH PLACEMENT FOR POWER GATING A UNIT                  |    |

| FIGURE 4.2: PLACEMENT OF POWER SWITCHES                                                 |    |

| FIGURE 4.3: ISOLATION CELLS INSERTED AT THE OUTPUT OF A POWER-GATED DOMAIN              |    |

| FIGURE 4.4: STATE RETENTION FLIP-FLOP                                                   |    |

| FIGURE 4.5: POWER DOWN SEQUENCE                                                         |    |

| FIGURE 4.6: MULTIPLIER POWER GATED VIEW OF THE FLEXCORE                                 |    |

| FIGURE 4.7: SWITCH CONTROL ARRANGEMENT                                                  |    |

| FIGURE 5.1: METHODOLOGY FLOW OF THE SOFTWARE ANALYSIS                                   |    |

| FIGURE 5.2: MULTIPLICATION LOCALIZATION EXAMPLE IN THE AUTCOR APPLICATION C-CODE        | 30 |

| FIGURE 5.3: AUTCOR 'PROFILE' FILES.                                                     |    |

| FIGURE 5.4: AN EXCERPT FROM THE AUTCOR 'SHOWCODE' FILE                                  | 33 |

| FIGURE 5.5: AN EXCERPT FROM THE AUTCOR 'READABLE' FILE                                  | 33 |

| FIGURE 5.6: MULTIPLIER USAGE IN EEMBC BENCHMARK, AUTCOR.                                | 35 |

| FIGURE 5.7: MULTIPLIER USAGE IN EEMBC BENCHMARK, FFT                                    |    |

| FIGURE 5.8: N-ISA INSTRUCTION MAPPING                                                   | 37 |

| FIGURE 5.9: SEVERAL INSTRUCTIONS OF AUTCOR N-ISA CODE                                   | 37 |

| FIGURE 5.10: APPLYING POWER GATING CONTROL SIGNAL                                       | 38 |

| Figure 5.11: Extended N-ISA                                                             |    |

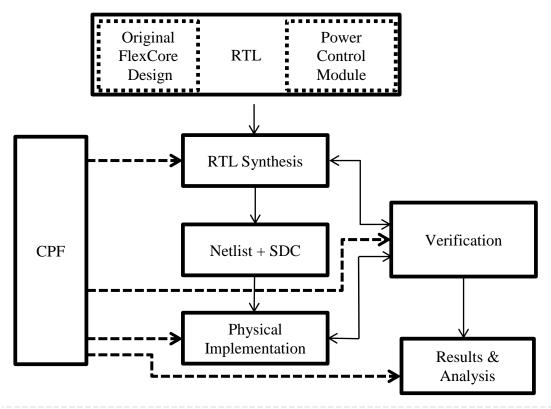

| FIGURE 6.1: HARDWARE IMPLEMENTATION FLOW                                                | 40 |

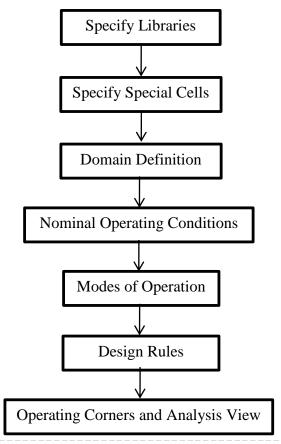

| FIGURE 6.2: CPF SPECIFICATION STRUCTURE                                                 |    |

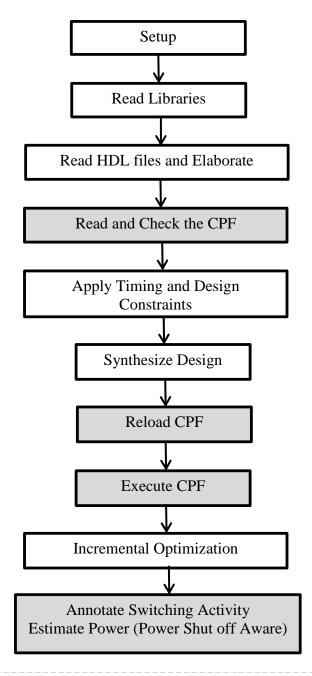

| FIGURE 6.3: RTL SYNTHESIS FLOW                                                          | 44 |

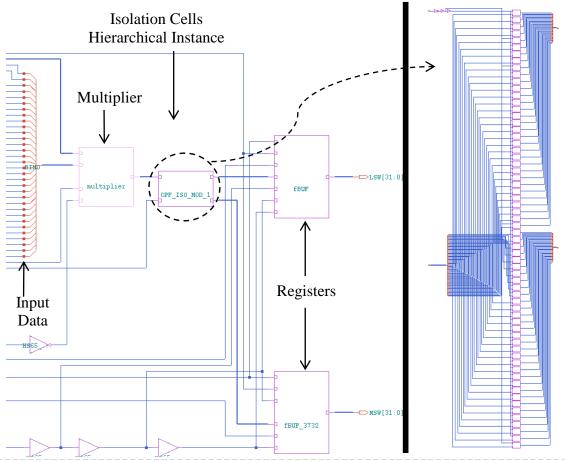

| FIGURE 6.4: SCHEMATIC VIEW OF THE SYNTHESIZED NETLIST SHOWING ISOLATION CELLS HIERARCHY | 45 |

| FIGURE 6.5: SCHEMATIC VIEW OF THE ISOLATION CELLS IN THE HIERARCHICAL GROUP             |    |

| FIGURE 6.6: NISA EXTENDED BITS FOR POWER CONTROL AND THEIR OPERATION                    |    |

| FIGURE 6.7: PHYSICAL IMPLEMENTATION FLOW                                                | 49 |

| FIGURE 6.8: PHYSICAL VIEW OF THE MULTIPLIER DOMAIN, SWITCHES, ISOLATION CELLS AND       |    |

| POWER/GROUND NETS                                                                       |    |

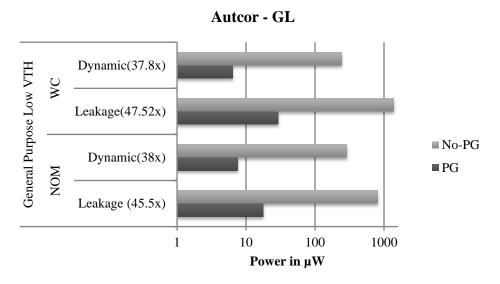

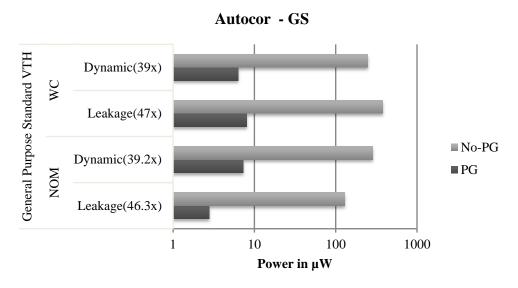

| FIGURE 7.1: POWER COMPARISON FOR THE MULTIPLIER, BENCHMARK: AUTCOR, LIB: GP-LVT         |    |

| FIGURE 7.2: POWER COMPARISON FOR THE MULTIPLIER, BENCHMARK: AUTOCOR, LIB:GP-SVT         |    |

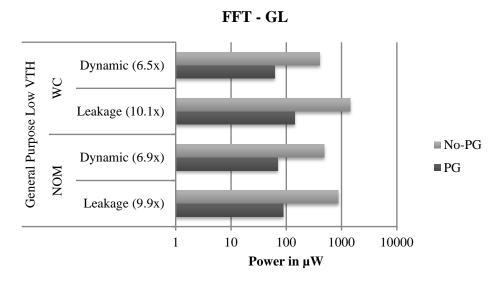

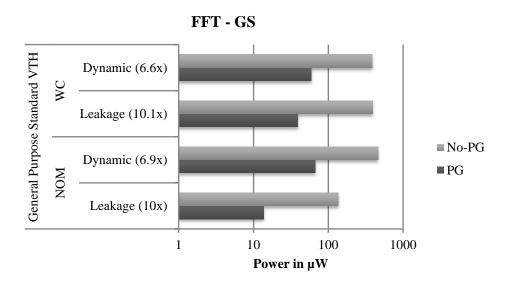

| FIGURE 7.3: POWER COMPARISON FOR THE MULTIPLIER, BENCHMARK: FFT, LIB: GP-LVT            |    |

| FIGURE 7.4: POWER COMPARISON FOR THE MULTIPLIER, BENCHMARK: FFT, LIB: GP-SVT            |    |

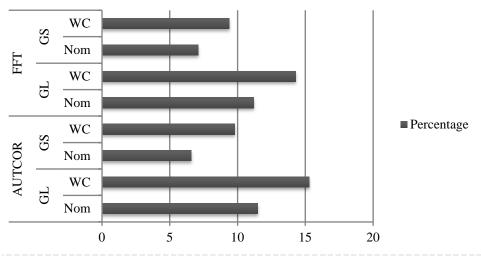

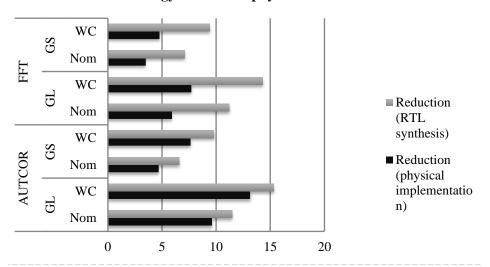

| FIGURE 7.5: OVERALL POWER/ENERGY REDUCTION FROM THE ORIGINAL DESIGN                     | 55 |

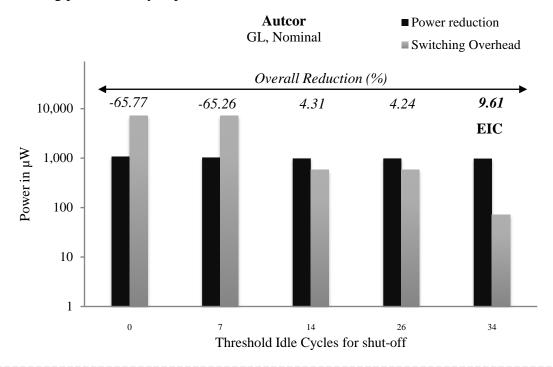

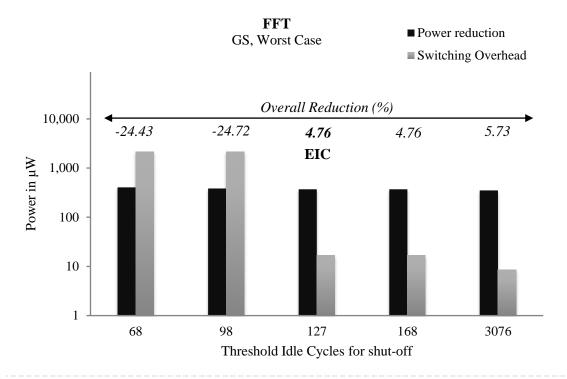

| FIGURE 7.6: POWER COMPARISON OF POWER REDUCTION AND SWITCHING OVERHEAD,                 |    |

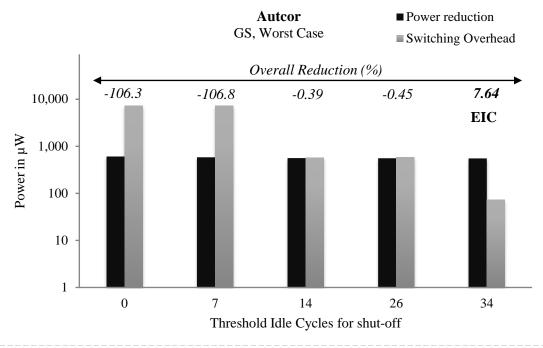

| BENCHMARK: AUTCOR, LIB: GP-LVT, NOMINAL                                                 | 57 |

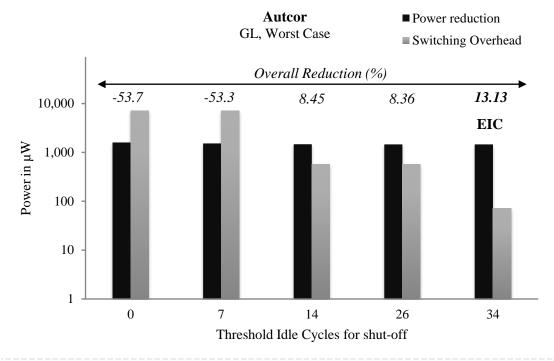

| FIGURE 7.7: POWER COMPARISON OF POWER REDUCTION AND SWITCHING OVERHEAD,                 |    |

| BENCHMARK: AUTCOR, LIB: GP-LVT, WORST CASE                                              | 57 |

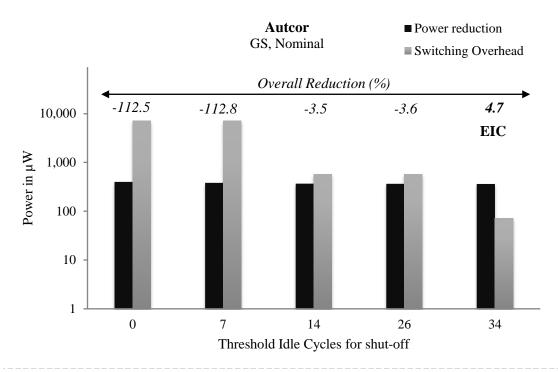

| FIGURE 7.8: POWER COMPARISON OF POWER REDUCTION AND SWITCHING OVERHEAD,                 |    |

| BENCHMARK: AUTCOR, LIB: GP-SVT, NOMINAL                                                 | 58 |

| FIGURE 7.9: POWER COMPARISON OF POWER REDUCTION AND SWITCHING OVERHEAD,                 |    |

| BENCHMARK: AUTCOR, LIB: GP-SVT, WORST CASE                                              |    |

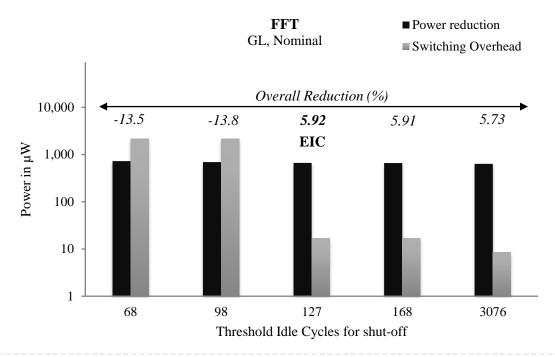

| FIGURE 7.10: POWER COMPARISON OF POWER REDUCTION AND SWITCHING OVERHEAD, BENCHMARK:     |    |

| Lib:GP-LVT, Nominal                                                                     |    |

| FIGURE 7.11: POWER COMPARISON OF POWER REDUCTION AND SWITCHING OVERHEAD, BENCHMARK:     |    |

| LIB:GP-LVT, WORST CASE                                                                  |    |

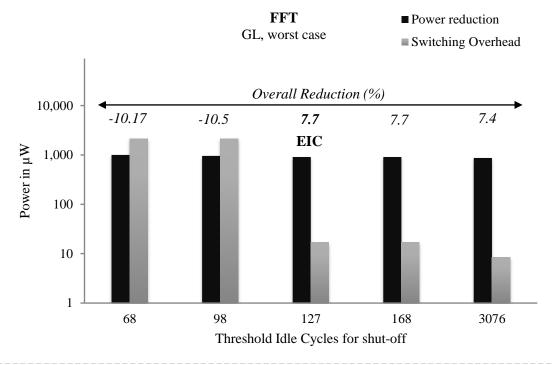

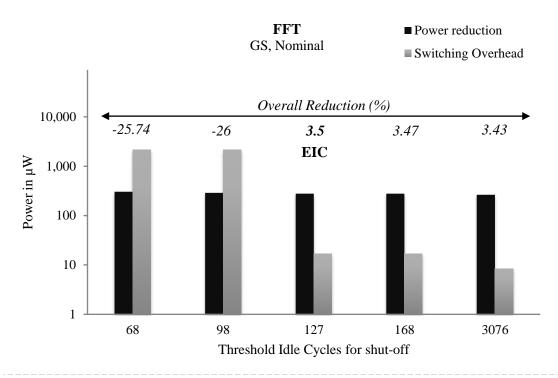

| FIGURE 7.12: POWER COMPARISON OF POWER REDUCTION AND SWITCHING OVERHEAD, BENCHMARK:     |    |

| LIB:GP-SVT, NOMINAL                                                                     |    |

| FIGURE 7.13: POWER COMPARISON OF POWER REDUCTION AND SWITCHING OVERHEAD, BENCHMARK:     |    |

| LIB:GP-SVT, WORST CASE                                                                  |    |

| FIGURE 7.14: POWER/ENERGY REDUCTION FOR OVERALL DESIGN AFTER ESTIMATION AT PHYSICAL LE  |    |

| (ACTUAL)                                                                                | 61 |

## **List of Tables:**

| TABLE 5.1: EEMBC APPLICATION PROFILING STATISTICS                                       | 29 |

|-----------------------------------------------------------------------------------------|----|

| TABLE 5.2: EEMBC APPLICATION PROFILING STATISTICS INCLUDING IIC                         | 34 |

| TABLE 6.1: POWER DOMAINS AND MODES FOR THE POWER GATED FLEXCORE DESIGN                  | 43 |

| TABLE 6.2: POWER AND GROUND NETS FOR THE POWER GATED FLEXCORE DESIGN                    |    |

| TABLE 7.1: OVERALL ENERGY & POWER REDUCTION AFTER RTL SYNTHESIS, BM: AUTCOR & FFT       | 55 |

| TABLE 7.2: ENERGY CONSUMPTION OF ORIGINAL DESIGN AND REDUCTION ESTIMATIONS              | 62 |

| TABLE 7.3: POWER CONSUMPTION OF ORIGINAL DESIGN AND REDUCTION ESTIMATIONS (ACTUAL) AFTI |    |

| PHYSICAL IMPLEMENTATION                                                                 | 62 |

| TABLE 7.4: AREA COMAPRISON OF SPECIAL CELLS AND REST OF THE STANDARD CELLS              | 63 |

## List of Abbreviations

ALU Arithmetic and Logic Unit

Autor Auto-correlation

ASIC Application Specific Integrated Circuit

BC Best Case

CMOS Complementary Metal Oxide Semiconductor

CPF Common Power Format

DIBL Drain Induced Barrier Lowering

EEMBC Embedded Microprocessor Benchmark Consortium

EIC Effective Idle Cycles

FFT Fast Fourier Transform

FPGA Field Programmable Gate Array

GCC GNU Compiler Collection

GIDL Gate Induced Drain Leakage

GP General Purpose

GPP General Purpose Processor

HDL Hardware Description Language

IIC Intermediate Idle CyclesILP Instruction Level ParallelismISA Instruction Set Architecture

LS Load/Store

LVT Low Voltage Threshold

MIPS Microprocessor without Interlocked Pipeline Stages

MMMC Multi Mode Multi Corner

NMOS Negative channel Metal Oxide Semiconductor

Nom Nominal

N-ISA Native Instruction Set Architecture

PC Counter

PLA Programmable Logic Array

PMOS Positive channel Metal Oxide Semiconductor

RF Register file

RTL Register Transfer Level

RTN Register Transfer Notation

SDC Synopsys Design Constraints

SoC System On Chip

SRAM Static Random Access Memory SVT Standard Voltage Threshold

VTH Voltage threshold

WC Worst Case

## **Tools and Technology**

#### **Tools:**

Software Analysis

- GCC MIPS Cross-Compiler v 4.1.1

- FlexSoC Compiler

- FlexSoC Simulator

- FlexSoC HDL Generator

## Hardware Implementation

- Cadence Encounter RTL compiler v 9.1

- Cadence SoC Encounter v 8.1

- Cadence Incisive Design Simulator v 8.2

- Common Power Format v 1.1

#### **Benchmarks:**

EEMBC, Telecom Suite

- 1. Auto-correlation (Autcor)

- 2. Fast Fourier Transform (FFT)

## **Technology:**

STM 65 nm v 5.2.2

- General Purpose Standard threshold

- General Purpose Low threshold

- Operating Conditions:

- o Nominal: 1.0 V, 25 C

- o Worst Case: 0.9 V, 125 C

- o Best Case: 1.1 V, -40 C

- Special Cells

- o Isolation

- o State retention

- Header power switch

#### **Other Specifications:**

Clock Period – 3500 ps (285 MHz)

Typical Supply Voltage – 1.0 V

## 1. Introduction

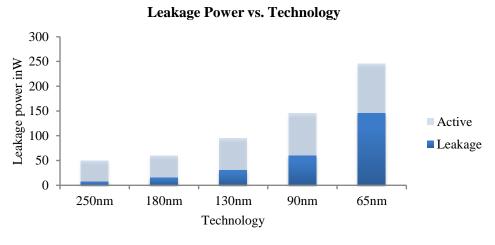

Power consumption is predicted to be increasing with the scaling of the transistor size and is heading to be an important concern in modern design [1] and [2]. One factor contributing to power is the addition of more transistors per chip which contributes to the increasing dynamic power and the other is increase in leakage current or stand-by current due to the technology itself. The dynamic power is efficiently reduced by scaling down supply voltage. But order maintain the circuit speed the threshold voltage has to be reduced at the same time. This adversely affects the leakage power. For example at 65 nm technology the leakage power is already comparable to dynamic power.

Figure 1.1: Trend of dynamic and leakage power for general processors.

Source: Intel: "Power Consumption of Microprocessors".

Another aspect of increasing power dissipation that needs attention is the increasing complexity of embedded applications and the limitation of battery capacity for portable devices. Increased complexity is due to addition of more functionality and thus more units to the processor. This increases both the dynamic and leakage power, while the requirement is to improve the battery life. With deep sub-micron transistor technologies the situation will get worse. Hence there is need for effective power management to reduce both dynamic power and leakage power. Another motivation for power management of embedded processors is that, some major units are idle for most of the operating time and some units when active might not be critical in terms of timing. The first case provides an opportunity to reduce the leakage power and the second case provides an opportunity to reduce the dynamic consumption of non-critical units by voltage scaling.

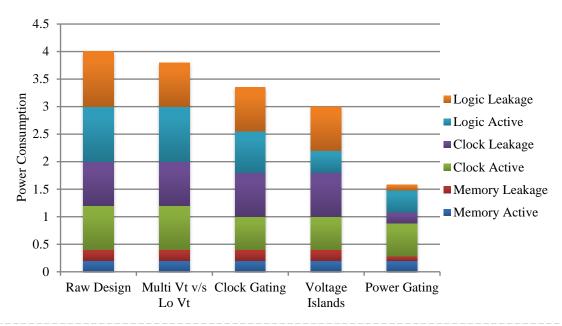

Several power management techniques have been used to reduce dynamic and leakage power dissipation. Scaling down the voltage is the most effective way of reducing dynamic power due to its square dependency. Figure 1.2 shows a set of power reduction techniques applied to a raw design. Clock gating and voltage islands reduce the active power. Multi threshold (Multi  $V_{TH}$ ) and power gating are the most commonly used techniques for leakage power reduction. Power gating is highly effective in leakage

reduction compared to multi threshold transistor technique. Power gating can reduce leakage power up to 50 times. However, multi- $V_{TH}$  transistor placement is automated, so that there is no timing penalty, whereas power gating can have small timing penalty. Area penalty is also higher for power gating. Although power gating has timing and area penalties, if optimally used can have significant leakage reduction compared to multi- $V_{TH}$ . Another technique to reduce leakage is substrate biasing, which is more complex to implement and has less effect when voltage supply is scaled down for technologies below 65 nm. These techniques are discussed in brief in Section 2.2.

#### **Effect of Power Reduction Techniques**

Figure 1.2: Effects of different power reduction techniques.

Source: Chip Design Magazine – "Be Early With Power".

#### 1.1 Motivation

The importance of leakage power reduction and room for leakage reduction in embedded applications mentioned in the previous section are the motivations for this thesis.

The thesis aim is to reduce the leakage power of the FlexCore processor by power gating functional units of the processor. Initial studies show that the multiplier is the most suitable unit on which power gating can be applied since the multiplier is a relatively huge block compared to the rest of the units of the FlexCore and evaluation of several EEMBC benchmarks on the FlexCore shows that it is idle for a large duration. This results in significant leakage power consumption. Power gating is employed to cut down this leakage but this comes with the expense of some area and timing overheads. There could also be power overhead if the technique is not employed appropriately, which is possible only through an exhaustive software analysis on the applications considered.

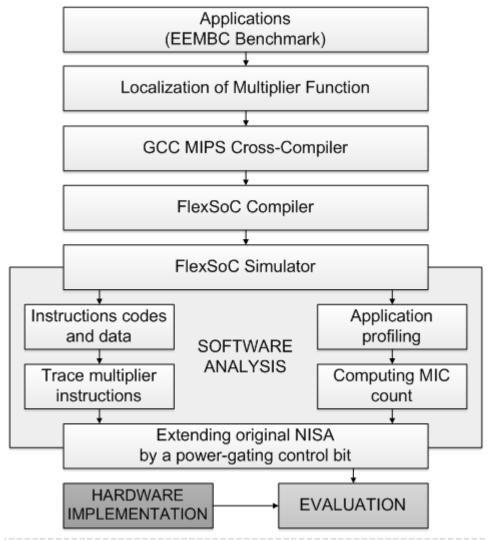

This thesis focuses on applying power gating technique to the multiplier unit of the FlexCore. The thesis work is divided into the *software analysis* and the *hardware implementation*. The software analysis phase involves evaluation and modification of the instruction set to provide power gating control and to identify the best instants to turn ON or OFF the unit. The hardware implementation phase focuses on the implementation of the power gated architecture using the common power format at the RTL level and physical level. The final integration phase will apply the information from the software analysis on the new power-gated FlexCore to show the power and energy reduction at the cost of some area overhead.

## 2. Power Reduction

## 2.1 Power Dissipation in CMOS Circuit

Power dissipation in a CMOS circuit is contributed by dynamic power, short-circuit power and the static power or leakage power. Dynamic power is a result of switching of the gates when the circuit is operating in an active state. Short-circuit power is a result of current flowing from  $V_{DD}$  to ground every time a transistor switches. This occurs for a short duration of the switching time due to finite rise and fall times of the gate signals, which results in both the PMOS and NMOS being ON at the same instant and forming a path from the supply to ground. Static power or leakage is the power consumed by a circuit during stand-by i.e. when the circuit is not in use. The total power consumption of the circuit thus can be written as

$$P_{total} = P_{dvnamic} + P_{short-circuit} + P_{leakage}$$

[1]

The dynamic power of the circuit is a function of the switching activity ( $\alpha$ ), clock frequency ( $f_{clk}$ ), supply voltage ( $V_{DD}$ ) and switching load capacitance ( $C_{load}$ ) as given in Equation 2.

$$P_{dynamic} = \alpha f_{clk} V_{DD}^2 C_{load}$$

[2]

As Equation 2 suggests that dynamic power reduction can be achieved by reducing any of the four factors and reducing the supply has the best efficiency. Techniques such as clock gating, logic restructuring, operand isolation, voltage scaling, dynamic voltage and frequency scaling techniques address one or more of these factors.

#### 2.1.1 Leakage Dissipation

The leakage power is further contributed by four factors, the gate induced drain leakage (GIDL), gate tunnelling leakage, reverse-biased junction leakage and the sub-threshold leakage current [3].

$$P_{leakage} = P_{GIDL} + P_{gate-tunneling} + P_{reverse-junction} + P_{sub-threshold}$$

[3]

Reverse-biased junction leakage current is the same as the reverse saturation current in a diode. The reverse biased diode here is formed between the source or drain and the substrate. The minority carriers near the depletion region and generation of hole-election pairs in the depletion regions form this reverse-biased leakage. Junction reverse-bias leakage components from both the source-drain diodes and the well diodes are generally negligible with respect to the other leakage components.

The gate induced drain leakage (GIDL) is caused by high drain to gate potential and the effect is further increased by high drain to substrate potential. A band-to-band tunnelling occurs in the small overlap region of the gate and the drain. For an NMOS transistor this condition occurs when the transistor is OFF (low gate-voltage) and the drain is at high potential. For a PMOS transistor it occurs when the transistor is OFF (high gate-voltage) and the drain is at a low potential.

The gate leakage flows from the gate through the "leaky" oxide insulation to the

substrate. The magnitude of the gate tunnelling current increases exponentially with the decrease in gate oxide thickness ( $T_{ox}$ ) and increase in the gate supply voltage. Even though the supply voltage is scaled with every technology and that helps reduce the gate tunnelling current, the oxide thickness also has to be scaled for the gate to have effective control over the channel. This again increases the gate leakage current. For an oxide thickness in the range of 2 to 0.5 nm, nearly every 0.3 nm reduction in the thickness for a constant gate voltage results in 10 times increase in the gate leakage current [3]. The gate leakage depends on the gate voltage applied to a transistor. High-k is an effective solution at the technology level.

The sub-threshold leakage is the drain-source current of a transistor operating in the weak inversion region. Unlike the strong inversion region in which the drift current dominates, the sub-threshold conduction is due to the diffusion current of the minority carriers in the channel for a MOS device. The sub threshold current increases exponentially with the linear decrease in the threshold voltage (V<sub>TH</sub>). As described in [3], the sub-threshold leakage can be written as

$$I_{Sub-threshold} = I_S * 10^{\frac{V_{GS} - V_{TH}}{S}} * (1 - 10^{-\frac{nV_{DS}}{S}})$$

[4]

Where n is the slope factor between 1-1.5.

Is is a technology constant current given as

$$I_S = 2n\mu C_{ox} \frac{W}{L} * (\frac{kT}{q})^2$$

[5]

And S is the sub-threshold swing in the range of 60 mV to 100 mV given by

$$S = n \left(\frac{kT}{a}\right) ln(10) \tag{6}$$

Further drain induced barrier lowering (DIBL) also causes  $V_{TH}$  to reduce in short channel devices. This contributes to huge increase in the sub-threshold current. DIBL is the process of reducing the depletion region near the drain at the influence of the drain voltage. Thereby the threshold voltage near the drain end of the channel reduces. Sub threshold leakage also increases with temperature as suggested by Equation 5.

Overall, the sub-threshold leakage and gate-tunnelling leakage are the main components that contribute to the leakage power in today's transistor technologies. The sub-threshold current is the major contributor to the overall leakage in the 65 nm technology considered in this work. Gate tunnelling leakage will be higher with 45 nm and smaller technologies.

The off state leakage current is the sum of all the above except gate-tunnelling leakage. The gate-tunnelling leakage requires the gate - source - bulk potential to be high.

$$I_{off-Leakage} = I_{GIDL} + I_{sub-threshold} + I_{reverse-biased}$$

[7]

## 2.2 Power Reduction Techniques

Section 1 and 2.1 show how and where power goes in a chip and some possible techniques to reduce them. This section will discuss these techniques in brief. Among the three components of power consumption as explained in the previous section, dynamic power has been the largest contributor. But the leakage power has been exponentially increasing which smaller transistor technologies (effect of reduced V<sub>TH</sub>). The quadratic dependence of dynamic power on voltage implies that reduction of voltage will have the highest impact. This has been the largest source of power reduction. The Industry has steadily moved down to lower supply voltage [4]. But reduction in voltage comes as the cost of reduced performance and must also be accompanied with variation of other technology process parameters. Since dynamic power is directly proportional to frequency, a reduction in frequency is suitable for low performance requirements. But the average power consumed per cycle remains the same. In order to reduce the dynamic power the switched capacitance must be addressed. The dynamic power component is reduced either by reduction of the switching activity or by reducing the capacitance or combination of both, like moving a high switching to a node with low capacitance. Leakage power is mainly dependent on the threshold voltage and the drain to source voltage. Higher threshold voltage would decrease the speed of the circuit. One way to address this is to make use of the fact that nearly 80% of a circuit is non-critical with respect to timing [4]. The other technique to eliminate leakage dissipation is to simply disconnect the unit not being used from the supply. This technique is called power gating, which is the technique used in this work to reduce leakage. In the following section few techniques commonly employed for power reducing are discussed.

#### 2.2.1 Dynamic Power Reduction Techniques

- Transistor Sizing: The requirement on performance often leads to up sizing transistors unnecessarily. This is especially true when IC's are custom designed. This over design results in wastage of power. This method of power optimization is concerned with identifying such sources of power wastage and downsizes them. For example transistors on non-critical paths may be up sized for better driving capability but since the overall performance is dependent on the critical path, the up-sized transistors will result in wastage. For synthesized blocks the synthesis tools can automatically identify such sources and downsize them. But for manually designed block it may not be effective and may not be always possible. Tools thus have a great impact. Logic restructuring involves reducing the number of stages wherever possible, so that the total switching activity is reduced. Such techniques are implemented by the modern tools automatically [4].

- Voltage Scaling: Voltage has been the most important parameter for reducing power, although there is some loss of performance. Voltage scaling must be accompanied by reducing the threshold voltage (V<sub>TH</sub>) to maintain the performance since the delay is approximately inversely proportional to V<sub>DD</sub>-V<sub>TH</sub>. If speed is not to suffer excessively V<sub>DD</sub> must be at least four times V<sub>TH</sub>. But the problem with such reduced V<sub>TH</sub> is increase in leakage current. This is more significant in nano-meter technologies. This is a major concern when designing caches, sense-amplifiers, static RAM's and PLA's. Low supply

voltage also means that the effect of noise is more and thus reliability is also less.

Voltage Island or multi-supply voltage is a better implementation of the voltage scaling principle where different  $V_{DD}$  is given to different blocks depending on the performance requirements. The disadvantage of voltage scaling for the entire design is that the maximum voltage scaling is limited by the performance requirement of the most critical unit. Other units (less critical) might be able to perform with a lower  $V_{DD}$ . By voltage islands method, units are separated into islands which operate on different voltage. This technique is more used in SOC designs where there are several functional blocks of varying throughput requirements. Each core has few voltage levels with which it can operate. No islands are needed for blocks operating only at the chip voltage. In voltage island technique level shifters must be added for communication between blocks of different  $V_{DD}$ .

Variable  $V_{DD}$  or dynamic voltage scaling is another variation of voltage scaling where  $V_{DD}$  is dynamically scaled depending on the performance requirements. This is usually employed along with frequency scaling.

• Clock gating and operand isolation are techniques which address the switching activity factor in Equation 2. In clock gating technique clock signal to flip-flops or registers is gated by an enable condition. When these storage elements are not used, the clock is not passed through and unnecessary dynamic activity is reduced. Generally the enable condition is shared with the enable condition for the flip-flops or registers. Similarly operand isolation disables data-path blocks which are not in use by inactivating their inputs through an enable signal. Clock gating and operand isolation are performed by the synthesis tool by enabling certain attributes. The scope for insertion of these is evaluated and inserted during the synthesis step. This step has become an inevitable step in today's design [5]. These techniques help in reducing dynamic power to certain extent. For the FlexCore design the savings from enabling these techniques were small. However as the main focus of this work was on the power gating implementation, the above techniques were not enabled.

#### 2.2.2 Leakage Power Reduction Techniques

- Multiple Threshold Transistors: Multiple threshold transistor design is used to reduce the leakage current which is predominant in the nano-meter technologies. In this technique low V<sub>TH</sub> transistors are used on the critical path so that the performance is not affected and high V<sub>TH</sub> transistors are used on non-critical paths so that the leakage power is reduced. Non-critical path means, the path where there is a positive slack. Typically most designs have only about 20% of the total transistors on the critical path, and therefore leakage power can be reduced. Automatic placement by tools ensure that the timing overhead is almost nil.

- Power gating is the most effective technique to reduce leakage power. In this

technique a unit which is not in use is disconnected from the supply or the

ground so that there is not path for leakage current. It is implemented with the

help of low leakage PMOS or NMOS transistors. The gate of the PMOS or

NMOS transistor decides whether the supply or ground respectively is connected to the unit. This method needs additional units to implement correct functionality and thus leads to some area penalty. There could also be a small timing penalty due to switching transition time. But 5% penalty is acceptable. This technique is best suited for units with large idle times. In this case the overhead is acceptable for the leakage gain that can be achieved. But to achieve optimal leakage reduction, the application profile has to be understood for effective control of the unit. Section 3 will explain about power gating in more detail.

- Other techniques at circuit level include usage of long channel transistors, thereby reducing the effect of drain induced barrier lowering (DIBL) and again this technique is very useful for small channel length transistors. But the increased channel length means more delay but this is compensated by making it wide, which gives high area overhead. This method is especially useful for SRAM's where delay is not important and its power consumption is mainly due to static power. Parking states technique forces gates or block to low leakage logic state when they are not in use. This method requires finding the input vectors that puts the unit to least leakage logic. The technique might be suitable for units that have higher non-idle time.

- Substrate biasing is a similar technique and an improvement over the MTCMOS, where the back bias voltage of the transistor is altered so that V<sub>TH</sub> changes. The substrate bias voltage can be varied dynamically depending on the requirement. The threshold voltage varies on the substrate bias as

$$V_{TH} = V_{TH0} + \gamma (\sqrt{V_{SB} + 2\varphi_F} - \sqrt{2\varphi_F})$$

[8]

Where  $\phi_F$  is the Fermi-potential and  $V_{TH0}$  is threshold at zero bias. As seen from the Equation 8 the threshold is square root function of the substrate source bias voltage. As the technology goes to smaller transistor sizes the voltage is scaled too. Hence the voltage  $V_{SB}$  can only be changed by a limited extent, which leads to only a small change in  $V_{TH}$ . Hence it might not be effective with future technologies. There is also extra routing overhead.

Altera's 40nm Stratix 4 FPGA's use programmable substrate biasing technique to increase  $V_{TH}$  on blocks which are on the non-critical path. In normal FPGA's all paths are optimized for high speed, whereas in Stratix 4 only blocks on critical path are optimized for high speed, and others are either give a back bias or if they are not in use they are isolated from supply by using power gating techniques [6].

## 3. FlexCore Processor

## 3.1 Background

FlexCore embedded processor is the platform on which power gating is applied in order to reduce leakage power [7]. FlexCore was developed as the first exemplar within the FlexSoC project by the VLSI Research Group at the Chalmers University of Technology. The FlexSoC approach moves away from the hard-coded instruction set architecture (ISA) by introducing a reconfigurable interconnect which is governed by a wide control word. In the FlexSoC framework, conventional methods to provide application performance are replaced with fine-grained control. Though FlexCore is based on the traditional five-stage pipeline architecture, it is a unique processor designed to be flexible and eventually extensible depending on the application specifics. Most importantly, the core stands out with its ability to have a reconfigurable datapath depending on the application, within the same architecture and compilation framework [7]. Subsequently, such flexible datapath configuration for each specific application without affecting the baseline processor architecture results in improved performance

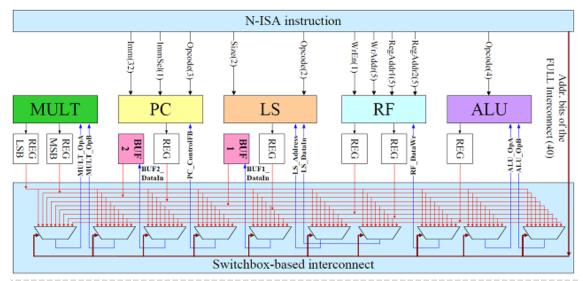

#### 3.2 Baseline Architecture of the FlexCore

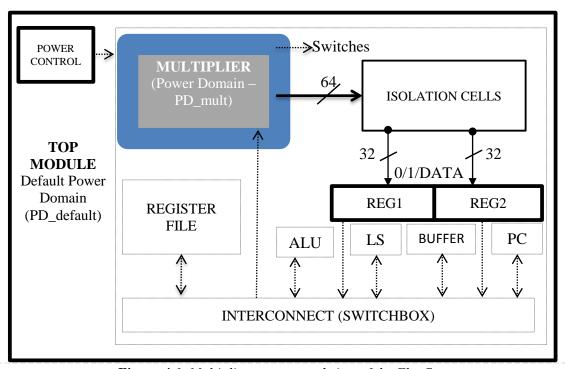

Original design of the processor is based on a simple MIPS R2000 processor's architecture in order to maintain full general-purpose processor (GPP) functionality. Therefore, FlexCore baseline architecture includes functional units to support the full GPP programmability such as Program Counter (PC), Load/Store (LS), Register File (RF), and Arithmetic and Logic Unit (ALU) (Figure 3.1). Two buffers are added which allows data to be directly restored or taken by any functional unit for more efficiency than writing data back to RF or memory. What distinguishes FlexCore processor architecture from the GPP architecture is that instead of using a dedicated interconnect, all functional units communicate through a flexible, fully connected interconnect. Although reconfigurable interconnect incurs power and area overhead, it can be utilized through trimming communication links under application profiling [7].

#### 3.2.1 Multiplier Extension

FlexCore also distinguishes itself with a feature which allows its architecture to be extended by adding more ports to switch-boxes of interconnect and extending the *wide* control word to include control signals for the new units [7].

The core has been extended by adding a multiplier to the baseline architecture in order to increase efficiency of executing multiplication-based embedded applications, such as the Fast Fourier Transform (FFT). This efficiency comes at the expense of two factors. First, the size: the multiplier unit is three times larger than the adder unit. Second, not all applications use multiplier as often as the FFT application. Therefore multiplier being a relatively large unit and used for a small fraction of the time results in considerable amount of leakage power dissipation. Hence, multiplier unit is the focus in this work which it is intended to be power-gated in order to reduce leakage power dissipation of the FlexCore.

**Figure 3.1**: Multiplier-extended FlexCore processor (The enable signals of the datapath units are not shown)

#### 3.2.2 Flexible Interconnect

Switch-box based interconnect with 90 possible links is a key difference of the FlexCore from other application-specific embedded processors. Together with another key component, exposed datapath, this full interconnect provides freedom for data to be routed among any function units of the processor [8].

#### 3.2.3 Native Instruction Set Architecture (N-ISA)

While GPP instructions are hard-coded, datapath and interconnect operations are exposed to the compiler in terms of a *wide control word*, named as Native-ISA (N-ISA). Having this *wide control word* of an exposed datapath, the FlexCore framework allows modelling various architectures and subsequently the N-ISA instruction permits the compiler to have more opportunities to efficiently schedule the instructions [9].

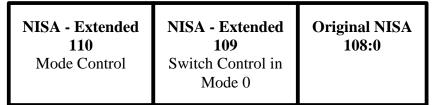

Structure of the N-ISA instruction highly depends on the number of datapath units and interconnect configuration. The N-ISA is mainly divided into two sections: datapath control bits and interconnect addresses bits (Figure 3.2). Starting from the least significant bit at the datapath control, the section consists of 5 bits for ALU, 18 bits for register file, 5 bits for load/store unit, 1 bit each for two data buffers, 37 bit for program counter, and 2 bits for multiplier. Overall, 69-bits are required for the datapath control. N-ISA interconnect has total 40 bits in where 4 bits are required for every switch-box dedicated for each functional unit.

Using long N-ISA comes to the cost of instruction bandwidth and a large memory footprint, but it can be resolved through instruction compression [8].

| NATIVE IN              | STRUCTION      | SET ARCHITECT | URE (109-bit   | ts)                  |               |               |

|------------------------|----------------|---------------|----------------|----------------------|---------------|---------------|

| INTERCONNECT (40-bits) |                | DAT           | TAPATH         | (69-bits             | )             |               |

|                        | MULT<br>2-bits | PC<br>37-bits | BUFF<br>2-bits | 100 CT (TO 100 bill) | RF<br>18-bits | ALU<br>5-bits |

Figure 3.2: FlexCore N-ISA instruction

## 4. Power Gating for the FlexCore Processor

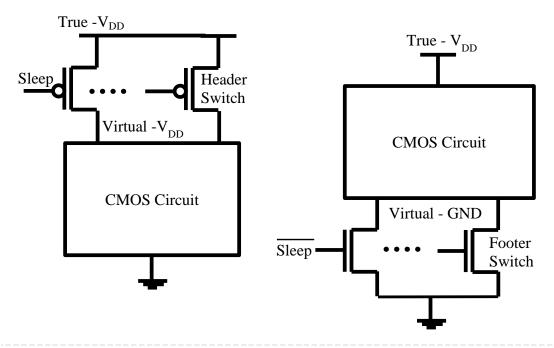

Power gating or power shut-off is a technique to reduce the leakage power of functional units or modules in a design. The unit considered for power gating is shut-off or deactivated when not in use and thereby reducing unnecessary leakage current. Shut-off involves disconnecting the unit or a gate from the supply or the ground using header or footer switches respectively. The gating is implemented with the help of either a header or a footer cell which are low leakage PMOS or NMOS transistors respectively. Figure 4.1 shows the header and footer switch placement. In case of header switch implementation the supply net to the CMOS circuit that connects to the switch is referred to as virtual  $V_{\rm DD}$  or in case of footer cell implementation the internal ground net is referred to as virtual ground.

Figure 4.1: Header and footer switch placement for power gating a unit.

The size of the switch depends on the maximum current consumption of the circuit and the capacitance on the switched supply. In a practical implementation the switch size is fixed and multiple switches are placed in parallel depending on the current requirement. The number of power switches that are required for a design has to be determined considering factors such switch area, leakage reduction and voltage drop. Small size leads to larger voltage drop due to smaller resistance and this will impact the performance [9].

The implementation of these switches can be performed either in a coarse-grained or fine-grained fashion [5]. In a coarse-grained implementation switches controls an entire block, where as in a fine-grained implementation several switches control smaller sections of the unit like cells or gates. In coarse grained implementation although the area overhead is small, switching capacitance is high and there will high rush currents. In the fine grained implementation since several switches address smaller units, the switching capacitance is low but the area overhead is much higher. This could also result in some leakage from the large number of switches. Coarse grained is suitable if all smaller units of the circuit being considered operate simultaneously. Fine grained is

suitable if units have different operating profile. Also the coarse grained technique is easier to place and route.

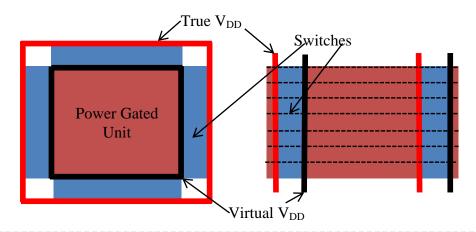

Further the switches can be placed in a ring or column fashion [5]. In a ring fashion as the name suggests switches are placed around the unit being power gated. In a column fashion they switches are placed in columns through the length of the unit. Ring placement is more efficient in terms of routing, but area overhead is slightly higher as compared to the column placement technique. Figure 4.2 shows the placement of these two types.

Figure 4.2: Placement of power switches Ring (left), Column (right)

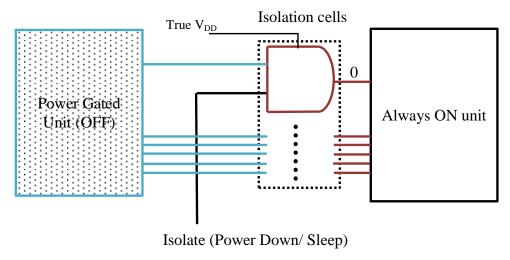

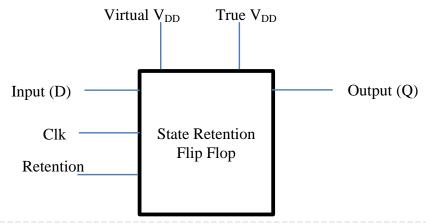

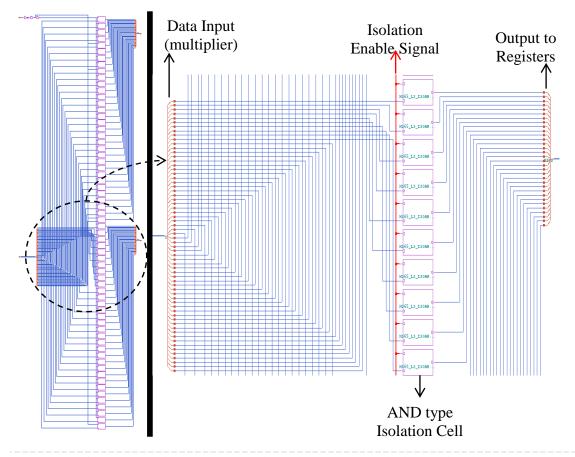

When power gating, another important issue to be considered is the floating states of the outputs of the power-gated unit. Also flip flops if present in the design will lose their state. Hence special cells to eliminate these problems are needed. Isolation cells are used to prevent floating outputs and state retention cells to save flip-flop states [5]. The isolation and state retention cells are showed in Figure 4.3 and Figure 4.4. Isolation cells are simple two input AND/NAND or OR/NOR gates with an isolation enable signal as one input and data as the other input. AND or NAND work with an active low signal for *isolation* and OR or NOR work with the active high signal for *isolation*. AND or NOR gate drives the output to 0 when isolated and the OR or NAND gate drives the output to 1 when isolated. Isolation can also be achieved with D latches in which case the output will be forced to the last output of the power-gated unit prior to shut down. State retentions cells operate on the virtual supply when the power down unit is in normal operation and switches to the global supply when the unit is shut down.

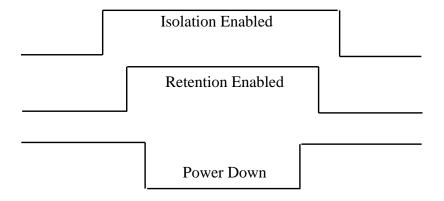

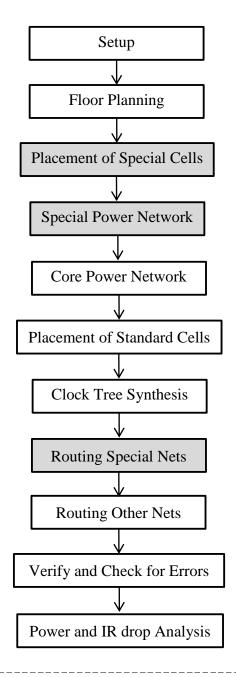

The cells can share the same enable signal. But there must be definite power up and power down sequence for these cells. A power up of the switches has to happen before the isolation and state retentions are disabled. If the power up occurs later then purpose of preventing floating states and preserving states of flip flops is damaged. The sequence followed in power down is isolation, state retention and power down of the switch and the reverse sequence during power up. This either automatically performed by the tool or manually performed by insertions of buffer cells. Figure 4.5 depicts the required power up/down sequence. The isolation, state retention cells are specified during the synthesis and place and route phase respectively. The switches are either automatically or manually placed during physical implementation. The Cadence SoC

Encounter tool used in this design performs the placement of the switches either in ring or column fashion through special commands.

Figure 4.3: Isolation cells inserted at the output of a power-gated domain

Figure 4.4: State retention flip-flop

Figure 4.5: Power down sequence

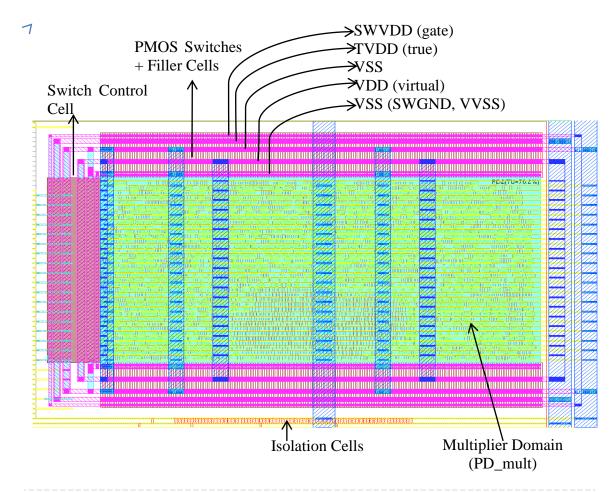

## 4.1 Power gating the Multiplier

Figure 4.6 shows the block diagram of the Flex-Core with the multiplier power-gated. A header switch is used to power gate the multiplier in this work<sup>1</sup>. A coarse grained power gating is implemented. In a coarse grained implementation the switch(s) perform the power shut-off for the entire unit by switching the virtual supply between the true  $V_{DD}$  ( $TV_{DD}$ ) and the off-state voltage. The off-state voltage is not at zero potential and is usually a value close to the threshold of the header switch. The switches are placed in a ring fashion since placement and routing are easier during the physical implementation<sup>2</sup>.

Figure 4.6: Multiplier power gated view of the FlexCore

The multiplier unit which is considered for power gating is defined in a different power domain and the domain is termed as  $PD\_mult$ . A power domain is a region of the design having specific power architecture different from rest of the design region. All units in a specific domain will follow the rules of power architecture specified for that domain. The rest of the FlexCore modules are defined in the in the default power domain  $PD\_default$ . All modules and units unless specified to be in a specific domain will be placed in the default power domain.

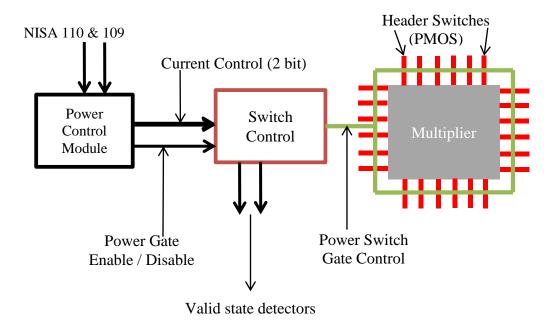

The technology libraries used in this work provides two types of cells for the switch implementation, the switch control cell and the PMOS header switch. The control cell receives the switch enable signal along with signals to control the transition current consumption and signal to enable detection of valid states. The switch ON and OFF of the multiplier is performed by PMOS header switches. The gate signal of these switches called the "switch enable" defines the turn-ON and turn-OFF of the multiplier. The switch control unit drives the switch enable signal of the PMOS switches. The switch

\_

<sup>&</sup>lt;sup>1</sup> The STM65 v5.2.2 library used here is provided with header switch only.

<sup>&</sup>lt;sup>2</sup> The aim of this work is focused more towards estimating the power reduction rather than electrical impact of the switche.

control cell provides more flexibility in terms of switch transition time by controlling the current consumption to transit from the off-state supply to the true global supply, i.e. It provides an option to have a more smoother transition at the expense of wake-up time. The switch control cell also generates signals to indicate the detection or switching to a certain valid state. A signal to indicate transition of the internal  $V_{DD}$  or the virtual  $V_{DD}$  to the true global  $V_{DD}$  is generated always. Other signals are generated only by enabling the 'detection ON' for the switch control. Figure 4.7 shows the switch arrangement for the multiplier.

Figure 4.7: Switch control arrangement

The switch control unit consists of two *internal switches*, two *current controlled sources* and two *detectors*, one each for the virtual VDD and the PMOS gate control signal. There is also *control logic* to generate different control signals based on the input to the unit. The *current control* input signals to the unit controls the current output of the *current controlled source*, which in turn decides the switching transition duration. This unit has a dimension of 99.2  $\mu$ m  $\times$  24  $\mu$ m (2380.8  $\mu$ m<sup>2</sup>).

The off-state multiplier will have outputs in floating state, which can affect the functionality of other units that depends on these outputs. In order prevent the propagation of these floating signals to other units, the multiplier outputs must be isolated from units that depend on it. The only unit connected to the multiplier output is the interconnect unit, through the multiplier registers. The actual multiplier unit in the FlexCore hierarchy consists of the multiplier logic and the registers shown outside the *PD\_mult* domain in the Figure 4.6. By restricting the shut-down domain to the logic and keeping the registers outside will eliminate the need for state retention cells. There will be no gain in power but only a small increase in area if state retention cells were to be used . Another option is to still define the registers inside the power gated domain and include the D-latch isolation cells at the output of the registers. However in this work only isolation cells with AND or NAND gates will be inserted in final design.

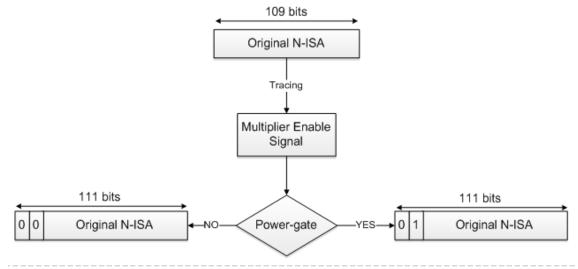

The *switch enable* signal can be either controlled directly by the software via the NISA binary instruction or by a dedicated "*power control module*". The power control module can be either an on chip or off chip controller. In this work an on-chip controller is used. The power control module sends the power control information to the switches either by in-built power-control logic or passing the information from the NISA instruction. The power control module can operate in three modes which are explained in Section 6.3. Power control for the multiplier is best achieved by software via the extended NISA instruction. Hardware control is inefficient for this processor. Hardware control was used only during the initial stages to verify functionality and to estimate power reduction. Under software control the only important function to be performed by hardware is to delay the power down by some cycles till the output is stable, which is difficult to be implemented on the software.

## 5. Software Analysis

## 5.1 FlexSoC Tool-chain

The FlexCore processor, targeting embedded systems, has been developed by VLSI Research group at Chalmers in the context of FlexSoC project. The FlexCore processor combines the advantages of power efficiency and high performance in Application-Specific Integrated Circuits (ASICs) and flexibility and programmability of General Purpose Processors (GPPs). A reconfigurable interconnect allows extensions to the datapath as well as flexible routing of data between datapath units.

In order to support features of the FlexCore processor, a FlexSoC tool-chain (FlexTools) was also developed as follows:

#### 1. Software analysis

- FlexSoC Compiler compiles MIPS-assembly code into Register Transfer Notation (RTN) code of the FlexCore processor.

- FlexSoC Simulator generates instruction and data binary codes from RTN code which are used to verify and estimate power-performance of FlexCore processor.

#### 2. Physical implementation

- FlexSoC HDL Generator generates RTL code for an instance of the FlexCore processor with the specific datapath and *interconnect* configurations.

- EDA tools for synthesis, place and route, and verification.

In addition, a Makefile was created to chain up all tools to evaluate the properties of the FlexCore processor from C-code applications to physical implementation. In this section, the focus is software analysis whose methodology flow is presented in Figure 5.1.

Figure 5.1: Methodology flow of the software analysis

#### **5.2 EEMBC Benchmark**

In order to examine performance of the FlexCore processor for a diverse range of the applications, there are 10 benchmarks available from the Embedded microprocessor benchmark consortium (EEMBC). They are from three suites, *aifirf*, *canrdr*, *bitmnp* of the Automotive suite; *rgbcmy*, *rgbhpg*, *rgbyiq* of the Consumer suite, and *Autcor*, *conven*, *viterb*, *fft*, of the Telecom suite. All these benchmarks are integer and nodivision applications because at the moment the FlexCore processor does not support floating-point computation and hard-divider in its datapath [8].

Out of 10 available EEMBC benchmarks, we selected two benchmarks that are Autcor (Auto-correlation) and FFT (Fast Fourier Transform) from the Telecom suite, for evaluating the impacts of the power gating technique in the scope of our thesis. Autcor and FFT are chosen because they are different in size and use the multiplication operation in different ways. In detail, FFT benchmark is one of the largest among EEMBC applications, with 162,967 cycles in total. Autcor uses 19,553 cycles, a number fairly similar to the other provided EEMBC application.

The multiplication property for two selected benchmarks is traced and reported in Table 5.1 It is clear that there is not a significant diversity in usage of the multiplier in both applications. However, the cycle count of the FFT benchmark is 8.33x higher than Autcor, making the FFT's multiplier utilization one of the largest among the other available EEMBC benchmarks as determined in the initial pre-study.

Table 5.1: EEMBC application profiling statistics

| Benchmark | Total        | MU     | JLT-only   |

|-----------|--------------|--------|------------|

| Dencimark | cycles count | Cycles | % of total |

| AUTCOR    | 19553        | 400    | 2.05       |

| FFT       | 162967       | 10240  | 6.28       |

In this multiplier-only usage (MULT-only) computation, the intermediate cycles between all two consecutive multiplier activations were not included, only the cycles during which multiplier was active.

Intermediate idle cycles (IIC) of the multiplier are significant factor when applying power gating technique. Every benchmark has different values of IIC which changes during its execution period. If the multiplier is power gated without considering IIC, there would be a large number of switch transitions, which would lead to power overhead. On the other hand, considering IIC in a way that makes multiplier to be ON or OFF for a significant period of time would result in no power savings. In order to achieve best power savings, the most optimal IIC (or *effective idle cycles*, Section 7.2) must be determined. Multiplier's IIC computation and results are presented further down the front-end flow in Section 5.5.1.

## **5.3** Localization of the Multiplier Function

After selecting applications to apply power gating technique in the FlexCore processor, it is necessary to take into account the behaviour of the multiplier in the C-code of both, Autcor and FFT benchmarks. Since multiplier unit of the FlexCore processor is chosen to be power-gated, the active-cycle count and the idle-cycle count between two consecutive multiplications are important features which need to be extracted through application profiling by using FlexTools. In order to do so, the multiplication instructions are localized in terms of a separate function with two or more input parameters and this function is called within the main program. As a result, FlexTools now are able to provide essential information which allows to us to estimate how often the multiplier to be used as well as how long the multiplier to be activated or deactivated in terms of a cycle count. An example of localizing multiplication instruction is shown in Figure 5.2.

Multiplication in original C code:

Accumulator += ((e s32) InputData[i] \* (e s32) InputData[i+lag]) >> Scale;

Localize multiplication instruction in the separate function: MultFunc(InputData[i], InputData[i+lag]);

<u>Call multiplication instruction in the main program:</u>

Accumulator += (\*mult\_result >> Scale);

Figure 5.2: Multiplication localization example in the Autcor application C-code. MultFunc is a name of the multiplication function, mult\_result is an output of the MultFunc

Notice that localization of the multiplication instructions must not introduce errors in the functionality of benchmarks. This is performed by verifying the re-organized C-code to guarantee that it is exactly executed as the original benchmark. Afterward, the verified C-codes are ready to be compiled. The goal of re-organizing the original C-codes is to help FlexTools to identify individual multiplication functions and provide application profiling information specifically related to the multiplier unit.

## **5.4** Tools Chain

#### 5.4.1 MIPS Cross-compiler

GCC MIPS Cross-compiler is an open source tool that FlexTools relies upon. Since the datapath of the FlexCore processor share almost the same functional units with the conventional GPP processor (MIPS-lite datapath), GCC MIPS Cross-compiler is used to compile the C-code into the MIPS assemble code which is provided to FlexSoC compiler. Therefore, in the following step of the front-end flow, a re-organized C-code together with the other required library's files are translated into MIPS assembly by a GCC MIPS Cross-Compiler. In this study, the GCC-4.1.1 version was used to assemble the C-code as a stable version. The other newer version of GCC might not be compatible with the FlexSoC compiler, thus, they need to be pre-tested. The execution of the MIPS Cross-compiler is controlled by rules in the Makefile (Appendix-A).

#### **5.4.2** FlexSoC Compiler (FlexComp)

Next, a MIPS-assembled code is compiled by the FlexSoC compiler, named FlexComp, which is a backbone of the FlexTools. As soon as MIPS assembly files are available, FlexSoC compiler can produce RTN code for the FlexCore processor with a specific datapath and interconnect configurations.

During the FlexComp compiling, MIPS assembly instructions are scheduled and expressed in a single, long RTN instruction which makes it possible to achieve high instruction level parallelism (ILP). It is clear that using a reconfigurable interconnect, the datapath operation of the FlexCore processor is exposed to the compiler which is exploited to gain ILP against to the GPP processor.

#### 5.4.3 FlexSoC Simulator (FlexSim)

The main target of this step is to generate all data which are required for application profiling as well as hardware verification. FlexSim, a cycle-accurate simulator, takes RTN code as inputs, simulate and generate data and instruction code in terms of Native Instruction Set Architecture (N-ISA) for back-end phase. Furthermore, application profiling can be performed through using outputs provided by FlexSim. Due to the fact that FlexSim simulator provided an exposed N-ISA code, it is possible to trace of the operation of the individual functional units in a cycle-by-cycle manner. Several necessary options of FlexSim used for applications profiling are listed as follows:

-PROF Application profiling. Cycle-count and frequency for individual

functions used within applications.

-TRACENISAD Tracing and debugging. Mixed binary/RTN instruction format for

debug.

-TNISA Showing program as timed N-ISA instructions in binary format.

-TRINARYTNISA Showing program as timed N-ISA instructions in hexadecimal

format.

-SHOWCODE Showing program after static scheduling.

All output formats can be dumped into files for post-processing. As the FlexSoC simulator generates required information for software analysis and, subsequently, to apply power gating technique, the flow continues to the next stage of understanding content of the output files.

## 5.5 Evaluation of Multiplier Behaviour

#### 5.5.1 Computing IIC Value

The FlexSim is used with an option –PROFF to generate a file, named 'Profile', which provides information related to cycle-count of individual function. Snapshots of profile files for the original and re-organized C-code of the Autcor benchmark are shown in Figure 5.3.

| 1 Profiling information:       |                     |      |       |        | 1 Profiling information: |                     |      |                    |        |  |

|--------------------------------|---------------------|------|-------|--------|--------------------------|---------------------|------|--------------------|--------|--|

| 2 =============                |                     |      |       |        | 2 ======                 |                     |      |                    |        |  |

| 3 ;Function ;Size;Count;Cycles |                     |      |       |        | 3                        | ;Function           |      | ;Size;Count;Cycles |        |  |

| 4 \$L47 (thal.c)               | ;al_printf          | ; 13 | ;533  | ;6929  | 4 \$L47 (thal.c)         | ;al printf          | ; 13 | ;626               | ;8138  |  |

| 5 putChar                      | ;putChar            | ; 4  | ;517  | ; 2068 | 5 putChar                | ;putChar            | ; 4  | ;606               | ;2424  |  |

| 6 \$_20(thal.c)                | ;al_printf          | ; 4  | ;517  | ; 2068 | 6 \$ 20(thal.c)          | ;al printf          | ; 4  | ;606               | ; 2424 |  |

| 7 \$L66(thal.c)                | ;al_printf          | ;3   | ;533  | ; 1599 | 7 \$L66(thal.c)          | ;al printf          | ;3   | ;626               | ; 1878 |  |

| 8 \$_19(thal.c)                | ;al_printf          | ;3   | ;533  | ; 1599 | 8 \$_19(thal.c)          | ;al_printf          | ;3   | ;626               | ; 1878 |  |

| 9 \$L62(thal.c)                | ;al_printf          | ;3   | ;533  | ; 1599 | 9 \$L62(thal.c)          | ;al_printf          | ;3   | ;626               | ; 1878 |  |

| 10 \$L5 (autcor00.c)           | ;fxpAutoCorrelation | ; 8  | ; 100 | ;800   | 10 \$_3(autcor00mod.c)   | ;fxpAutoCorrelation | ; 9  | ; 100              | ; 900  |  |

| 11 \$L3(crc.c)                 | ;Calc_crc8          | ; 6  | ; 128 | ;768   | 11 \$L3(crc.c)           | ;Calc_crc8          | ;6   | ; 128              | ;768   |  |

| 12 \$_1(crc.c)                 | ;Calc_crc8          | ; 8  | ;59   | ; 472  | 12 \$L18(usr.c)          | ;putx               | ;8   | ;88                | ;704   |  |

| 13 \$_1(usr.c)                 | ;putStr             | ;3   | ; 155 | ; 465  | 13 \$L20(usr.c)          | ;putx               | ;5   | ; 110              | ;550   |  |

| 14 \$L7 (usr.c)                | ;putStr             | ;3   | ; 155 | ; 465  | 14 \$L10(autcor00mod.c)  | ;fxpAutoCorrelation | ;5   | ; 100              | ;500   |  |

| 15 \$L5 (usr.c)                | ;putStr             | ;3   | ; 155 | ; 465  | 15 \$_1(crc.c)           | ;Calc_crc8          | ;8   | ;59                | ; 472  |  |

| 16 \$L18(usr.c)                | ;putx               | ; 8  | ;56   | ; 448  | 16 \$_1(usr.c)           | ;putStr             | ;3   | ; 155              | ; 465  |  |

| 17 \$L2(crc.c)                 | ;Calc_crc8          | ; 6  | ; 69  | ; 414  | 17 \$L7 (usr.c)          | ;putStr             | ;3   | ; 155              | ; 465  |  |

| 18 \$L20 (usr.c)               | ;putx               | ; 5  | ;70   | ; 350  | 18 \$L5 (usr.c)          | ;putStr             | ;3   | ; 155              | ; 465  |  |

| 19 \$L19(usr.c)                | ;putx               | ; 4  | ;70   | ; 280  | 19 \$L19(usr.c)          | ;putx               | ; 4  | ; 110              | ; 440  |  |

| 20 al_printf                   | ;al_printf          | ; 15 | ; 18  | ; 270  | 20 \$L2(crc.c)           | ;Calc crc8          | ; 6  | ; 69               | ; 414  |  |

| 21 th_printf                   | ;th_printf          | ; 10 | ; 18  | ; 180  | 21 MultFunc              | ;MultFunc           | ; 4  | ; 100              | ; 400  |  |

Figure 5.3: Autcor 'profile' files.

Based on the original C-code (left-side), based on the C-code with localized multiplier (right-side).

Profile of the benchmark shows information which concerns size, count, and consequently, cycles of each function. In order to retrieve such multiplier related information from the Profile, localization of the multiplier function is required to be accomplished. Through the content of Profile, information of multiplier behaviour can be collected which is the main reason for re-organizing C-code of benchmarks before compilation and simulation. Right-side of Figure 5.3 shows multiplication is localized as the separate function (MultFunc) in C-code benchmark (Line 21).

Furthermore, also from the profile, it is known that multiplier takes 4 cycles to execute its function and is used 100 times in Autcor benchmark. However, it is not clear yet when and how often exactly the multiplier is active in the benchmarks. In order to determine the cycle index when multiplication is executed and finished, we need a mapping step between several output files provided by FlexSim. For the sake of simplicity, we should have a look to understand how the multiplication execution is represented in RTN format.

Option –SHOWCODE in the runmips command statically schedules the benchmarks and writes to a file, called *Showcode* file. This file presents every function of a benchmark, their execution representation in RTN format, and equivalent program counter (PC) value sorted in a numerical order. A short excerpt of the *Showcode* is shown in Figure 5.4.

| 194        | , { -                            | <pre>6 -} CRTN [[CPCJumpSA main,CPCGetPC]]</pre>              |

|------------|----------------------------------|---------------------------------------------------------------|

| 195        | , { -                            | 7 -} CRTN [[CRegWrite R31 PC_ImmPC]]                          |

| 196        | , { -                            | 8 -} CRTN [[]]                                                |

| 197        | , { -                            | 9 -} CRTN [[]]                                                |

| 198        | , { -                            | 10 -} CRTN [[]]                                               |

| 199        | , { -                            | 11 -} CRTN [[CPCJumpSA -1]]                                   |

| 200        | , { -                            | 12 -} CUserNOP ""                                             |

| 201        | , { -                            | -} CLabel "MultFunc"                                          |

| 202        | , { -                            | <pre>13 -} CRTN [[CRegRead2 R4,CRegRead1 R5]]</pre>           |

| 203        | , { -                            | 14 -} CRTN [[CRegRead1 R31,CPCImm mult                        |

| 204        | . { -                            | 15 -} CRTN [[CLSRead LSW 4 PC ImmPC                           |

|            | , ι                              | is jetti [[elsiteda lsii_+ ie_iiiiii e •••                    |

| 205        | , { -                            | 16 -} CRTN [[CRegWrite R2 Ls_Read                             |

|            | , { -<br>, { -                   | ,                                                             |

| 205        | , { -<br>, { -<br>, { -          | 16 -} CRTN [[CRegWrite R2 Ls_Read                             |

| 205<br>206 | , { -<br>, { -<br>, { -<br>, { - | 16 - CRTN [[CRegWrite R2 Ls_Read} CLabel "fxpAutoCorrelation" |

Figure 5.4: An excerpt from the Autcor 'showcode' file

In Figure 5.4, multiplier function is labelled as 'MultFunc' (Line 201). From the Profile file, it is known that multiplier takes 4 cycles to execute multiplication function. Here, it is shown a representation of those 4 cycles in RTN format (Lines 202-205). Each cycle has an equivalent PC values that, in MultFunc case, are 13-16. These numbers are helpful to be known in cycle-accurate analysis, which is done by using FlexSim with an option, -TRACENISAD to generate a file, named Readable, simply because this file includes human-readable debug information. Figure 5.5 depicts a part of the Readable file of the Autcor benchmark where multiplier activity is presented.

```

1319 00000000AE424000000340101880 - 000057 [PCGetPC, PCJumpSA 13, RegRead2 ...

1320 000000F040000000000039003E0 - 000058 [LSWrite LSW 4 Alu Rslt.

1321 000000000000000000000000029000 - 000013 [RegRead1 R5, RegRead2 R4]

1322 0EC000000008000000002000F8000 - 000014 [MultRegWrite, Mult Regbank Out2...

1323 000C00040000C000000005800000 - 000015 [PCJumpDA Regbank Outl, LSRead LSW 4

1324 0000000AA000000000003900040 - 000016 [LSWrite LSW 4 Ls Read Mult LSW...

1326 000000000E40000000080088001 - 000060 [PCImm (Just 2), RegRead1 R17, ALUOpc

1337 00000000AE424000000340101880 - 000057 [PCGetPC,PCJumpSA 13,RegRead2 R6...

1338 000000F040000000000039003E0 - 000058 [LSWrite LSW 4 Alu Rslt.

1339 000000000000000000000029000 - 000013 [RegRead1 R5,RegRead2 R4]

1340 0EC00000000800000002000F8000 - 000014 [MultRegWrite, Mult Regbank_Out2..

1341 000C0004000C0000000005800000 - 000015 [PCJumpDA Regbank_Out1,LSRead LSW_4

1342 0000000AA0000000000003900040 - 000016 [LSWrite LSW 4 Ls Read Mult LSW...

1343 00000000000000000000080004000 - 000059 [PCImm (Just 2), RegRead2 R16]

1344 000000000E40000000080088001 - 000060 [PCImm (Just 2), RegRead1 R17, ALUOpc

```

Figure 5.5: An excerpt from the Autcor 'readable' file

In Figure 5.5, the first 4-integer values on the left represent the cycle number. There are 19,553 cycles in total for Autcor benchmark. Second column consists of N-ISA instructions in hexadecimal format. Then, the third column depicts PC value and the fourth one – equivalent RTN format of each cycle.

As PC values of the multiplier function are 13-16, in Readable file they are traced as 000013-000016 values (Lines 1321-1324 & 1339-1342). As it can be noticed from this figure, here multiplier is active 2 times (out of 100 in Autor application).

Consequently, multiplier IIC cycles are computed by summing all the non-multiplier cycles in between active multiplier cycles. In this example, there are 14 IIC cycles (Lines 1325-1338). However, in other time-domain positions (see, Figure 5.5), Autcor has 35 IIC cycles. Table 5.2 presents application profiling statistics including IIC data.

Table 5.2: EEMBC application profiling statistics including IIC

| Benchmark | Total MU |        | T only     | IIC                    | Total IIC | MULT with IIC |            |  |

|-----------|----------|--------|------------|------------------------|-----------|---------------|------------|--|

| Denchmark | cycles   | Cycles | % of total | пс                     | Total IIC | Cycles        | % of total |  |

| AUTCOR    | 19553    | 400    | 2.05       | 14, 34                 | 1531      | 1931          | 9.88       |  |

| FFT       | 162967   | 10240  | 6.28       | 1, 22, 47,<br>93, 2950 | 72148     | 82388         | 50.55      |  |

Activity of the multiplier including IIC consumes up to 1931 cycles, or 9.88% of total benchmark cycles. It is determined by summing all the cycles from the first multiplier activation to the last one. It also can be computed by adding total IIC of the multiplier to actual multiplier activity cycles. In FFT case, summation of the IIC and multiplier-only usage cycles (82,388) boosts the total multiplier usage up to 50.6% of total application cycles. A diverse usage of a multiplier in Autcor (9.88%) and in FFT (50.6%) benchmarks is one of the main reason of the selection of these applications. However, there is another important factor that differentiates Autcor and FFT – a number of multiplier's IIC which is irregular in both benchmarks.

Table 2 presents a range of IIC values. Instead of having one constant IIC value and, hence, knowing an exact number of idle cycles between each multiplier execution, there is an irregular number of IIC. Such irregularity of IIC complicates automatic application of power gating technique which would require taking into consideration switching power overhead. Without concerning switching power overhead, IIC parameter would not affect power gating complexity. Therefore, further analysis of both benchmarks related to irregular IIC is required in order to apply the most optimal power gating.

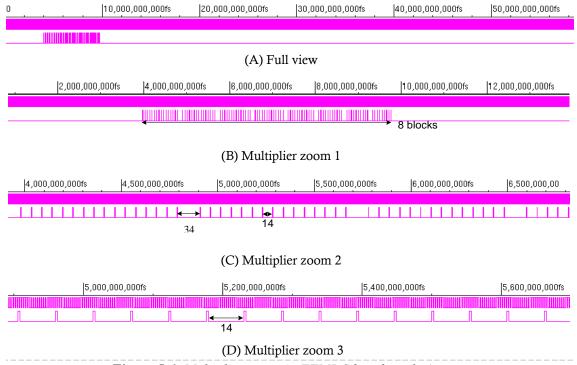

Figure 5.6 presents a graphical view of Autcor benchmark and its multiplier activity. Subfigure A shows the full span of the application with total cycles showed in upper line. The multiplier usage is presented in the lower line. Multiplier activity is illustrated according its enable signal being '1' for one-cycle in the N-ISA instruction while multiplier actually requires 4 cycles to complete its function. In subfigure B, it is shown all the multiplier executions that are 'separated' in 8 blocks, which few of them are zoom in and presented in subfigure C. Lastly, in subfigure D, one of the blocks is zoomed and depicted.

Figure 5.6: Multiplier usage in EEMBC benchmark, Autcor.

Upper line in each subfigure represents cycles and lower – multiplier activity

Notice that there are two IIC in Autcor benchmark (Figure 5.6.C). The larger 'distance' between two multiplier executions is 35 cycles, which is what is meant by 'separating' the multiplier activity in 8 sub-blocks. The smaller distance, which is also shown in Figure 5.6.D, is 14 cycles – the minimum IIC of the benchmark.

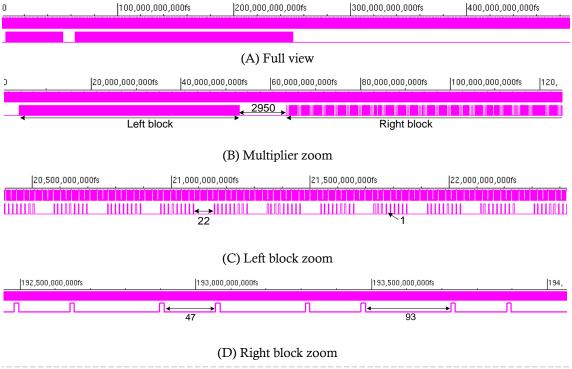

The graphical view of the FFT application is shown in Figure 5.7. The entire multiplier usage in FFT (50.6%) is presented in subfigure A. FFT multiplier activity is 'divided' into two blocks that are closer zoomed in subfigure B to show the difference between them. Each block is presented in further subfigures: the left block in subfigure C and the right one – in D.

Figure 5.7: Multiplier usage in EEMBC benchmark, FFT.

Upper line in each subfigure represents cycles and lower – multiplier activity

Most attention in FFT multiplier usage requires the difference between the left (Figure 5.7.C) and the right (Figure 5.7.D) blocks. Each block has two different IIC which makes FFT benchmark to have 5 different IIC. The fifth one is the largest that separates the blocks and it contains 2950 cycles (Figure 5.7.B). The left block holds IIC of 1 and 22. The right block contains 47 and 93.

#### **5.5.2** Tracing Multiplier Instructions

#### Method 1

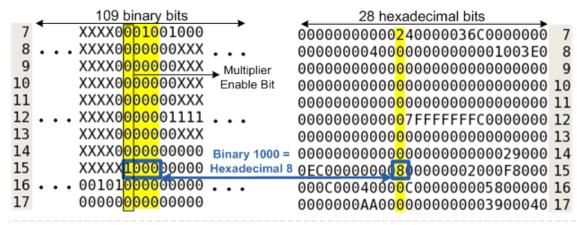

In parallel with computing the IIC count based on *Profile*, *Showcode*, and *Readable* files, a trace of multiplier instructions is performed using N-ISA code file generated by the FlexSoC simulator. Multiplier instructions can be traced only using hexadecimal N-ISA instruction. The original N-ISA consists of 109 bits of control signals for each functional unit in the FlexCore. Figure 5.8 shows the mapping of the N-ISA.

#### N-ISA (108:0) INTERCONNECT (108:69) DATAPATH (68 : 0) INTERCONNECT (108:69) **PCunit** LSunit LSunit BUFF-2 A BUFF-1 A RF W1 **MULTunit MULTunit** ALUunit1 ALUunit1 ControlEB Data in Address A Addr B Addr Addr Addr Addr A Addr B Addr Addr Addr Addr (96:93) (108:105)104:101) (92:89) (80:77)(76:73)(72:69)(100:97) (88:85) (84:81) DATAPATH (68 : 0) PROGRAM CONTROL LOAD-STORE REGISTER FILE ALU BUF-2 BUF-MULTIPLIER (68:67) (66:30)(29)(28)(27:23)(22:5)(4:0)STALL ALUop STALL Rr2 (14:10) STALL MM-SEL PCop IMMED ENABLE STALL LSop LSsize STALL-2 Rr1 Rw1 (68) (9:5)(4) (3:0)

Figure 5.8: N-ISA instruction mapping

As mentioned previously, N-ISA instruction consists of address bits for interconnect and control bits for datapath units. The last 8 LSB are reserved for the multiplier units' addresses (108:101) in the *interconnect*. In the *trinary* N-ISA format, the only instruction, that has other than X value in multiplier address, is on Line 15 where multiplier executes its function (Figure 5.9). Datapath has two bits related to the multiplier functional unit: stall (68) and enable (67). Enable signal is a key point of this multiplier instruction tracing method.

Every time the multiplier is active, enable signal is triggered to '1' in trinary format, otherwise, it is set by '0'. Therefore, according to the enable signal of the multiplier, activation of the multiplier can be traced by only using the N-ISA instruction.

#### Method 2

FlexSim generates N-ISA instructions in two formats: in hexadecimal and in trinary codes. Data files for both formats are identical. Trinary format consists of 109 bits of binary 0 and 1, and X (don't care) values. Hexadecimal code requires less storage space by consisting of 28 bits of hexadecimal values (0-9 and A-F). Examples of both formats of the same N-ISA instruction are presented in Figure 5.9.

Figure 5.9: Several instructions of Autcor N-ISA code Trinary (left) and in hexadecimal formats (right).