## MASTER'S THESIS

# on Software Transactional Memory for Graphics Card

by MUHAMMAD TAYYAB CHAUDHRY

Department of Computing Science and Engineering

CHALMERS UNIVERSITY OF TECHNOLOGY

Göteborg Sweden 2009

### THESIS FOR THE DEGREE OF MASTER OF SCIENCE

# **Software Transactional Memory for Graphics Card**

Muhammad Tayyab Chaudhry mtayyabch@yahoo.com

## **Supervisor:**

Philippas Tsigas tsigas@chalmers.se

#### **CHALMERS**

Department of Computing Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY SE-412 96 Göteborg Sweden June 2009

### **Abstract**

The introduction of CUDA, NVIDIA's system for general purpose computing on their many-core graphics processor system, and the general shift in the industry towards parallelism, has created a demand for ease of parallelization. Software transactional memory (STM) simplifies development of concurrent code by allowing the programmer to mark sections of code to be executed atomically. The STM will then guarantee that other processes will see either none or all of the writes done in in that section. In contrast to using locks, STM:s are easy to compose and does not suffer from deadlocks. An STM can thus be seen as a concurrency control mechanism.

**Keywords:** Parallel processing, STM, Concurrent programming

## **Preface**

The three great essentials to achieve anything worth while are, first, hard work; second, stick-to-itiveness; third, common sense.

-Thomas Edison

I had an experience of a couple of years of web programming but latter turned to Computer Science teaching before I took admission in Masters program for Networks and Distributed Systems in Chalmers University of Technology. Here during studies I took two courses in Distributed Systems one of them was led by Philippas Tsigas. I made up my mind to do my thesis in Distributed Systems a year ago. Philippas welcomed me and gave me a brief introduction to Software Transactional Memory or STM and suggested to do some knowledge building by studying the related research papers. STM was a new field for me. Initial study led me believe that it will be a tough job but I was excited to take the challenge. As I kept on studying the recent research work, I realized that the future of Computer Architecture is Multi-core Systems which will definitely require a concurrency control mechanism for parallel programming. I finalized my thesis topic after consulting Philippas. But as a trial he supervised a 15 credit programming project on STM. After the research work studies, I was introduced with CUDA enabled NVIDIA's graphics card which contains hundreds of many-core processors. And then Philippas plainly told me to make an STM for NVIDIA's graphic card. It made me shiver for a moment because so far whatever I had studied was related to STMs for dual-core or quad-core processors. Whereas in addition to CPU, now I had to control more than a couple of tens of many-core processors on graphics card. It was a relief that CUDA is very similar to C language. I started working in device emulation mode, which at that time was sequentially executing. To my astonishment when I actually ran it in debug mode which runs concurrently, there was no error and no hang-up of system. It increased my confidence. At each and every step in this thesis, I climbed one step forward after each successful run. But this was not always the case. Whenever I was unsuccessful, I just tried to change the logic. I started with simple locking and with guidance of my supervisor, Philippas I could eventually run a test STM that proved to be working on shared memory. This prototype showed that it is possible to create synchronization among concurrent shared memory accesses. It had yet to be polished to add new features as I will explain latter and to provide ease of use to CUDA STM user. The excitement in working with CUDA is that its an unmanaged environment and I based the STM on C language pointer operations. Sometimes I really had to work hard just to find out that a pointer was going outside the desired range. But it did not lower my concentration ever. My project was approved by Philippas and he extended it further to mater's thesis making it over all 45 credit thesis. Much of the time was spent in searching, developing and testing different logics so that CUDA STM could become faster and generalized for maximum usage. I developed and programmed it alone under the supervision of Philippas. Where as other STMs are being developed by teams of professionals. This STM is the first one ever built in CUDA. I think this is one of the main reasons that kept me working hard with dedication throughout this thesis. I am glad that I could finally fulfill the requirements.

## Acknowledgements

I would like to pay my gratitude to a number of people who actively played their roles besides me, during this thesis. In particular, I would like to thank the following people for their support:

- My parents, Mr. & Mrs. Rashad Tanveer Chaudhry, for always encouraging me to acquire higher education and praying for me. Yes, they are proud of me.

- **Philippas Tsigas,** for having faith in me as my mentor for a whole year and agreeing to supervise my thesis. He encouraged me at every step to apply my own mental capabilities to develop logic and keeping me from going astray.

- **Daniel Cederman**, for his technical support that always led me to do more and more experiments polishing my work.

.

# **Contents**

| 1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   | 1.1 Transactional Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|   | 1.1.1 Hardware Transactional Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|   | 1.1.2 Software Transactional Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|   | 1.2 Database Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|   | 1.2.1 Atomicity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|   | 1.2.2 Consistency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|   | 1.2.3 Isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|   | 1.2.4 Durability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 10 |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 2 | Challenges for STM Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|   | 2.1 STM transactional Durability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|   | 2.2 Programming Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|   | 2.3 Semantics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|   | 2.4 Transforming Transactional Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 12 |

|   | 2.5 Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12   |

|   | 2.6 Serial vs. Concurrent Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 12 |

| _ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 3 | Concurrency Control Strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

|   | 3.1 Simple Locking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

|   | 3.2 Multi Version Concurrency Control (MVCC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|   | 3.3 Optimistic Concurrency Control (OCC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 14 |

| , | The second of th | 1.   |

| 4 | Types of STM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 16 |

|   | 4.1 Object based STM in Unmanaged Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17   |

|   | 4.2 McRT STM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|   | 4.2.1 New Language Constructs Introduced in Java for McRT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|   | STM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|   | 4.3 Herlihy et al.'s Dynamic STM (DSTM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 19 |

| _ | CUDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20   |

| 3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

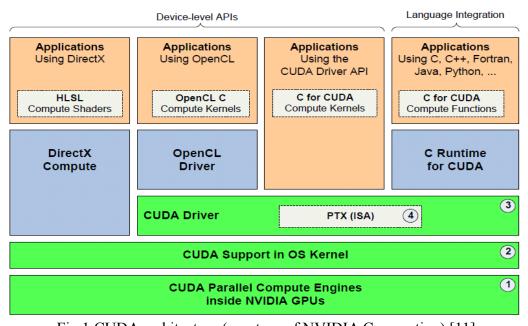

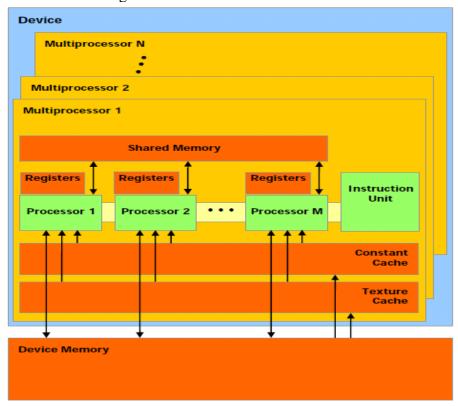

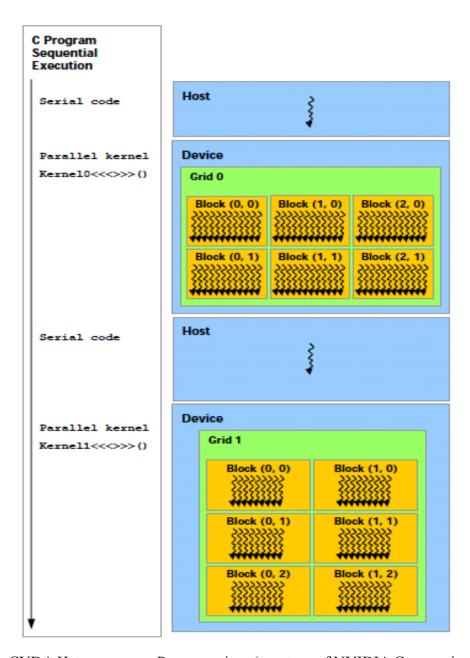

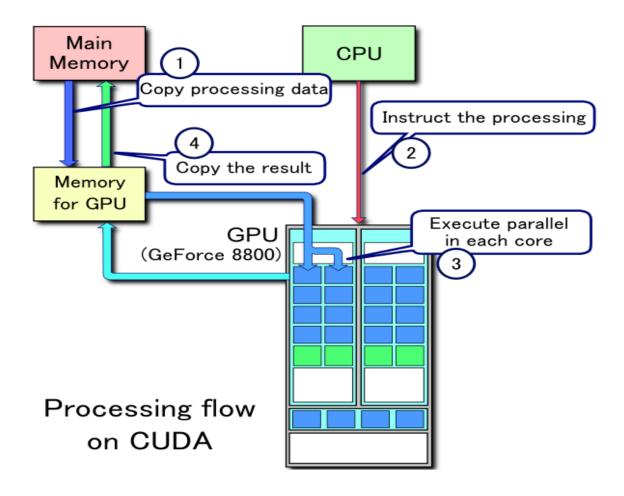

|   | 5.1 CUDA Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

|   | 5.2 CUDA Programming Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 21 |

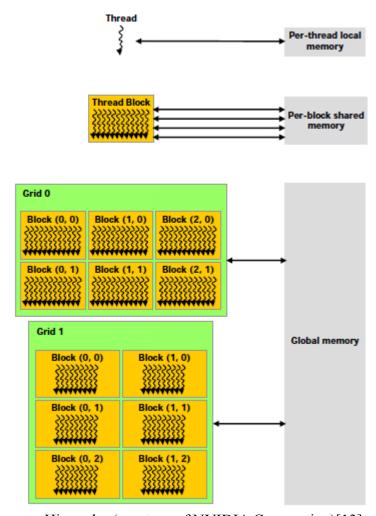

|   | 5.3 CUDA Language Abstractions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 21 |

|   | 5.4 Limitations of CUDA for a STM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25   |