# CONTROL OF STATIC SERIES COMPENSATOR FOR MITIGATION OF POWER QUALITY PROBLEMS

by

# HILMY AWAD

Department of Electric Power Engineering

CHALMERS UNIVERSITY OF TECHNOLOGY

Göteborg, Sweden

2004

# Control of Static Series Compensator for Mitigation of Power Quality Problems

HILMY AWAD ISBN 91-7291-406-8

© HILMY AWAD, 2004 All rights reserved

Doktorsavhandlingar vid Chalmers Tekniska Högskola Ny serie nr 2088 ISSN 1651-498X

School of Electrical Engineering Chalmers University of Technology Technical Report No. 475

CHALMERS UNIVERSITY OF TECHNOLOGY

Department of Electric Power Engineering S-412 96 Gothenburg, Sweden

Telephone: +46 (0)31 772 1632 Fax: +46 (0)31 772 1633 http://www.elteknik.chalmers.se

Chalmers Bibliotek, Reproservice Göteborg, Sweden 2004

#### **ABSTRACT**

Power Electronics and Advanced Control technologies have made it possible to mitigate power quality problems and maintain the operation of sensitive loads. Among power system disturbances, voltage dips, swells, and harmonics are some of the severe problems to the critical industrial loads. The static series compensator (SSC) is best suited to protect such loads against those disturbances. This thesis focuses on the control of the SSC in order to improve the transient and the steady-state responses and increase its injection capability.

To mitigate voltage dips, the thesis proposes a vector-controlled based algorithm to improve the transient and the steady-state responses of the SSC. The developed algorithm incorporates both current and voltage controllers with an inner current loop and outer voltage loop. Thus, it is referred to as the Double Vector Control (DVC) algorithm. To cope with unbalanced dips, a fast technique to detect the positive and the negative sequences is employed. Then the two sequences are controlled separately. Also the influence of the switching frequency on the controller performance is studied.

A Software Phase Locked Loop with a PI controller is proposed in order to obtain the phase and the frequency information of the grid voltage. The tuning of the PI controller is made according to a developed criterion based on the frequency requirements of the loads.

A number of power system events are studied and the behavior of the SSC is tested against each event. These events include short-circuit faults, capacitor-bank energizing, transformer energizing and load switching (linear and non-linear loads). Recommendations regarding the SSC operation for each event are given.

The possibility of employing the SSC to mitigate voltage swells and overvoltages is investigated. An overvoltage protection scheme is proposed, based on a combination of a dc resistor with a chopper and the SSC. The design equations of the dc resistor together with the chopper are provided.

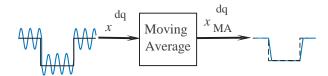

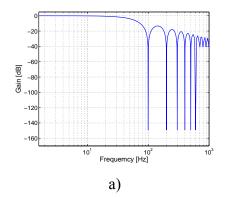

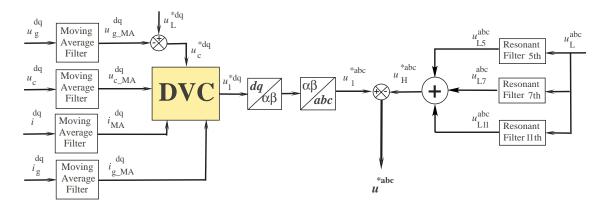

In order to mitigate voltage harmonics, a new controller is developed and implemented. In the proposed controller, a moving average filter is implemented in the synchronous reference frame to extract the fundamental component of the measured voltages and currents. Also, an active filtering capability is added by using the resonant filters for the 5<sup>th</sup> and the 7<sup>th</sup> harmonics. After the extraction of the fundamental component, it is controlled by the DVC. The operation of the SSC under distorted utility conditions and voltage dips is discussed.

The thesis also proposes two control techniques to charge the energy storage capacitor of the SSC. One of the techniques is based on a shunt diode rectifier, which is placed either on the load side or the grid side (both configurations are studied). The other technique exploits the voltage source converter of the SSC in combination with a proper control algorithm to charge the capacitor. A design guide for the energy storage capacitor is given.

To minimize the required active power, this thesis discusses and compares four different compensation strategies: 1) Voltage Difference Compensation; 2) In-Phase Compensation; 3) Phase Advance Compensation; 4) Progressive Phase Advance Compensation. The effect of the load power factor on the different strategies is investigated. A control algorithm based on a combination of the four strategies is proposed taking into account the minimization of the active power and keeping the injected voltage within the ratings of the SSC.

The validity of the developed controllers is verified by simulations and experiments. The simulation models are developed and implemented in the PSCAD/EMTDC package. A 10 kV SCC prototype is exploited to carry out the experiments with various load types.

#### **K**EYWORDS:

Custom Power, Dynamic Voltage Restorer, Energy Storage, Power Electronics, Power Quality, Static Series Compensator, Vector Control, Voltage Dips, Voltage Swells, Voltage Harmonics.

#### **PREFACE**

This work has been done at the Department of Electric Power Engineering, Chalmers University of Technology, Gothenburg, Sweden. The project is funded by ABB Power Systems, Elforsk and Energimyndigheten under the Elektra program. I am obliged to express my gratitude to those without whom my work would have been much more difficult, or even impossible, to accomplish.

I would like to thank professor Jaap Daalder for being my examiner. Thanks to professor Math Bollen and Dr. Jan Svensson for their guidance, support and encouragement. Thanks go to Dr. Ambra Sannino who has helped and supported me also. I have learnt a lot from them.

I would like to thank Prof. Essam Hamdi for being willing to help. My acknowledgements also go to all present members of the department for their help and providing a good working environment.

Thanks go to Per Halvarsson and Dr. Tomas Larsson, the steering committee of the research project, for their beneficial inputs and consideration. Ulf Grape and Bengt-Rune Wallstrom are also members of the steering group, thanks to them.

The experimental work involved in this thesis was carried out at the Institute of Energy Technology, Aalborg University, Denmark. During my work there, many colleagues have contributed to perform the experimental work successfully. Particularly, Professor Frede Blaabjerg has supervised me and provided all the facilities. Mr. Hans Nilsen and Mrs. Birthe Johansson have also helped me. Thanks to them and to all the staff at Aalborg University who have been involved with my work there. Special thanks go to my roommate Lucian Asiminoaei.

I would like to express my apologies to those whom I may have inadvertently failed to mention.

Last, but certainly not least, they are my mother, father, my great wife Hanaa and my sunshine Maryam and Amina who I am highly indebted to. Their endurance, encouragement and continuous support made it possible to finish this thesis.

# LIST OF PUBLICATIONS

#### **PUBLISHED PAPERS**

- [1] H. Awad, F. Blaabjerg, "Transient performance improvement of static series compensator by double vector control," *in Proc. of IEEE Applied Power Electronics Conference, APEC, February, 2004, California, USA.*

- [2] H. Awad, J. Svensson, M.H.J. Bollen, "Phase-locked loop for static series compensator," *in Proc. of European Power Electronics Conference, EPE* 2003, Toulouse, France, Sep. 2003.

- [3] H. Awad, J. Svensson, M.H.J. Bollen, "Static series compensator for voltage dips mitigation," *in Proc. of the IEEE PowerTech Conference*, 2003, Bologna, Italy.

- [4] H. Awad, J. Svensson, M.H.J. Bollen, "Testing static series compensator against capacitor bank energizing," *in Proc. of the IEEE PowerTech Conference*, 2003, Bologna, Italy.

- [5] H. Awad, M.H.J. Bollen, "Power electronics for power quality improvements," *in Proc. of IEEE International Symposium on Industrial Electronics, ISIE* 2003, June 9-12, 2003, vol. 2, pp. 1129-1136.

- [6] H. Awad, J. Svensson, "Compensation of unbalanced voltage dips using vector-controlled static series compensator with LC-filter," *in Proc. of the Industry Applications Conference*, 2002. 37th IAS Annual Meeting, vol. 2, pp. 904-910.

- [7] H. Awad, J. Svensson, "Charging techniques of dc capacitor for static series compensator," in Proc. of the IEEE International Symposium on Industrial Electronics, ISIE 2002, University of L'Aquila, Italy, July 8-11, vol. 3, pp. 930-935.

- [8] H. Awad, J. Svensson, "Self-startup of static series compensator," *in Proc. of the IEEE International Symposium on Industrial Electronics, ISIE* 2002, University of L'Aquila, Italy, July 8-11, vol. 4, pp. 1036-1041.

- [9] H. Awad, J. Svensson, "Double vector control for series connected voltage source converters," *in Proc. of the IEEE Power Engineering Society Winter Meeting* 2002, New York, USA, vol. 2, pp. 707-712.

#### **ACCEPTED PAPERS-AWAITING PUBLICATION**

- [10] H. Awad, J. Svensson, M.H.J. Bollen, "Mitigation of unbalanced voltage dips using static series compensator," *IEEE Trans. on Power Electronics*, accepted.

- [11] H. Awad, J. Svensson, M.H.J. Bollen, "Energy flow control between static series compensator and distribution systems," *Journal of Circuits, Systems, and Computers, Special Jubilee Issue: POWER ELECTRONICS CIRCUITS*, accepted.

- [12] H. Awad, J. Svensson, M.H.J. Bollen, "Tuning software phase-locked loop for static series compensator," *IEEE Trans. on Power Delivery*, accepted.

- [13] H. Awad, M.H.J. Bollen, "Energy optimization control techniques by static series compensator for constant power factor loads," *in Proc. of the IEEE Power Engineering Society General Meeting*, PES GM 2004, accepted.

- [14] H. Awad, F. Blaabjerg, "Mitigation of voltage swells by static series compensator," in Proc. of the IEEE Power Electronics Specialist Conference, PESC 2004, accepted.

- [15] H. Awad, F. Blaaberg, "Operation of static series compensator under distorted utility conditions," *IEEE Trans. on Power Systems*, accepted.

# **CONTENTS**

| 1. II        | NTRODUCTION                                                                                             | 13 |

|--------------|---------------------------------------------------------------------------------------------------------|----|

| 1.1.         | BACKGROUND AND MOTIVATION                                                                               |    |

| 1.2.         | CONTRIBUTIONS                                                                                           |    |

| 1.2.         | 6                                                                                                       |    |

| 1.2.2        | ı                                                                                                       |    |

| 1.2.3        | 3. Mitigation of Unbalanced Dips                                                                        | 15 |

| 1.2.4        | 4. Software Phase Locked Loop                                                                           | 15 |

| 1.2.5        | 5. Control and Optimization of Energy Flow                                                              | 15 |

| St           | tartup of SSC                                                                                           | 15 |

| M            | Inimization of Active Power Requirements                                                                | 15 |

| 1.2.0        | 6. Controller for Mitigation of Voltage Dips and Harmonics                                              | 16 |

| 1.2.7        | 7. Mitigation of Voltage Swells and Overvoltage Protection                                              | 16 |

| 1.2.8        | 8. Influence of Power System Events on SSC Performance                                                  | 16 |

| 1.3.         | THESIS OUTLINE                                                                                          | 16 |

| 2. s         | YSTEM DESCRIPTION AND DEVELOPMENTS                                                                      | 19 |

| 2.1.         | Introduction                                                                                            | 19 |

| 2.2.         | VOLTAGE DIPS                                                                                            |    |

| 2.3.         | STATIC SERIES COMPENSATOR                                                                               |    |

| 2.3.1        | 1. Operational principle of Static Series Compensator                                                   | 21 |

| 2.3.2        | 2. Layout and Design of SSC                                                                             | 22 |

| 2.3.3        | 3. Converter Topologies for SSC                                                                         | 22 |

| Н            | alf Bridge Topology                                                                                     | 23 |

|              | ull Bridge Topology                                                                                     |    |

|              | Iultilevel VSC                                                                                          |    |

| 2.4.         | CONTROL OF STATIC SERIES COMPENSATOR                                                                    |    |

| 2.5.<br>2.5. | DOUBLE VECTOR CONTROL FOR MITIGATION OF BALANCED DIPS AND SW  1. Derivation of Double Vector Controller |    |

|              |                                                                                                         |    |

| 2.5.2        |                                                                                                         |    |

| 2.5.3        | 3. Frequency Response of DVC                                                                            | 30 |

| 2.5.4        | 4. Step Response of DVC                                                                                 | 31 |

| 2.6.         | MODIFIED DOUBLE VECTOR CONTROLLER FOR MITIGATION OF UNBALAN                                             |    |

| AND SV       | WELLS                                                                                                   | 31 |

| 2.6.1.            | Separation of Positive and Negative Sequence Components                                       | 32 |

|-------------------|-----------------------------------------------------------------------------------------------|----|

| 2.6.2.            | Control of Positive and Negative Sequences                                                    | 33 |

| 2.6.3.            | Higher Switching Frequencies                                                                  | 33 |

| 2.7. PH.          | ASE LOCKED LOOP FOR STATIC SERIES COMPENSATOR                                                 | 34 |

| 2.7.1.            | Hardware PLL                                                                                  | 34 |

| 2.7.2.            | Software PLL                                                                                  | 34 |

| 2.7.3.            | SPLL Operational Principle                                                                    | 35 |

| 2.7.4.            | SPLL Modeling                                                                                 | 36 |

| 2.7.5.            | SPLL Linearized Model                                                                         | 37 |

| 2.7.6.            | Stability of SPLL                                                                             | 38 |

| 2.8. Tu           | NING SPLL                                                                                     | 38 |

| 2.8.1.            | Tuning First-order SPLL                                                                       | 38 |

| 2.8.2.            | Tuning Second Order SPLL                                                                      | 40 |

| 2.9. Co           | NTROL AND OPTIMIZATION OF ENERGY FLOW BETWEEN STATIC SERIES                                   |    |

| COMPENSA          | TOR AND GRID                                                                                  | 40 |

| 2.9.1.            | Control of active and reactive powers                                                         | 40 |

| 2.9.2.            | Charging Control of Energy Storage                                                            | 41 |

| _                 | tion Modes of SSC                                                                             |    |

| Self-c            | charging Technique                                                                            | 42 |

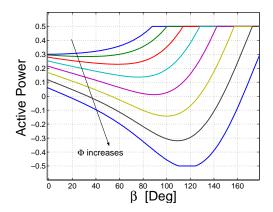

| 2.9.3.            | Compensation Strategies                                                                       | 44 |

|                   | ge Difference Compensation                                                                    |    |

|                   | ase Compensation                                                                              |    |

|                   | Advance Compensation                                                                          |    |

|                   | essive Phase Advance Compensation                                                             |    |

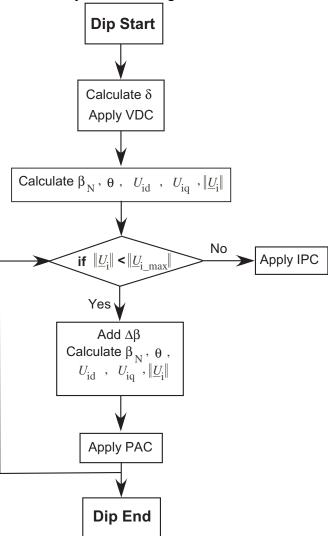

| -                 | sed Control Algorithm to Optimize SSC Performance ATIC SERIES COMPENSATOR AS AN ACTIVE FILTER |    |

| 2.10. 317         | Voltage Harmonics                                                                             |    |

| 2.10.2.           | Moving Average Filter                                                                         |    |

| 2.10.3.           | Resonant Filter                                                                               |    |

|                   |                                                                                               |    |

| 2.10.4.<br>Harmon | Block Diagram of Proposed Controller for Mitigation of Voltage Dips                           |    |

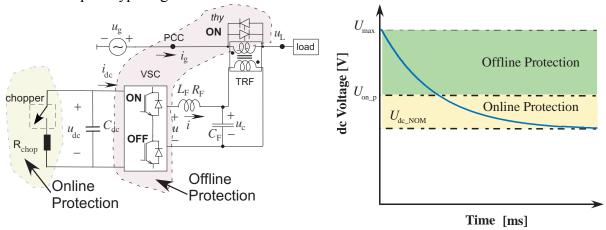

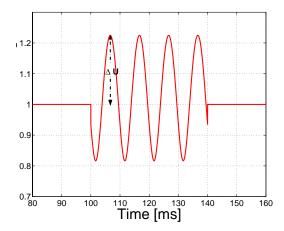

|                   | TIGATION OF VOLTAGE SWELLS AND OVERVOLTAGE PROTECTION                                         |    |

| 2.11.1.           | Voltage Swells                                                                                |    |

| 2.11.2.           | Overvoltage Protection Scheme                                                                 |    |

| Onlin             | e protection                                                                                  |    |

|      | Offlir        | ne protection                               | 55    |

|------|---------------|---------------------------------------------|-------|

| 2.   | .11.3.        | Design of dc resistor                       | 55    |

| 2.12 | 2. Su         | MMARY OF CHAPTER 2                          | 56    |

| 3.   | RES           | ULTS AND ANALYSIS                           | 57    |

| 3.1. | INT           | TRODUCTION                                  | 57    |

| 3.2. | SIN           | MULATION MODEL                              | 57    |

| 3.3. |               | PERIMENTAL SETUP                            |       |

| 3.4. | GE            | NERATION AND MITIGATION OF VOLTAGE DIPS     | 59    |

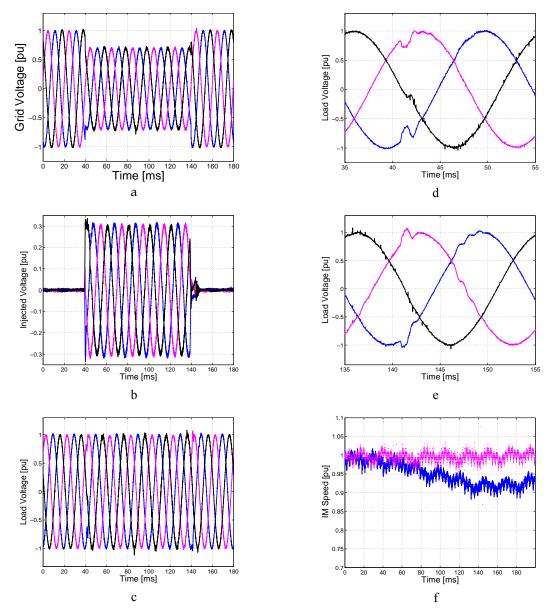

| 3.   | .4.1.         | Generation of Voltage Dips.                 | 59    |

| 3.   | .4.2.         | Mitigation of Balanced Voltage Dips         | 59    |

| 3.   | .4.3.         | Mitigation of Unbalanced Voltage Dips       | 61    |

| 3.5. | PEI           | RFORMANCE OF SOFTWARE PHASE LOCKED LOOP     | 62    |

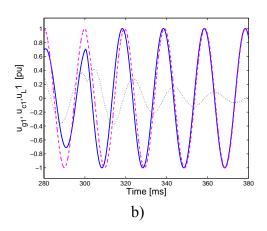

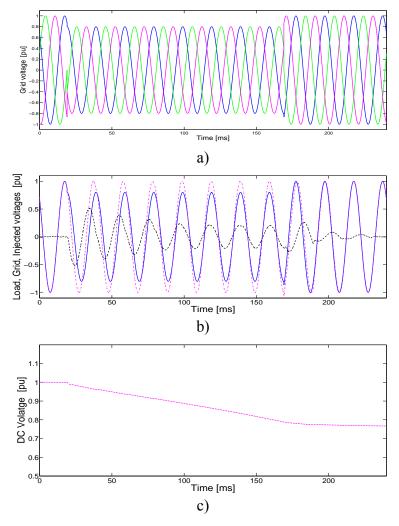

| 3.6. | CA            | PABILITY OF SSC TO MITIGATE VOLTAGE SWELLS  | 63    |

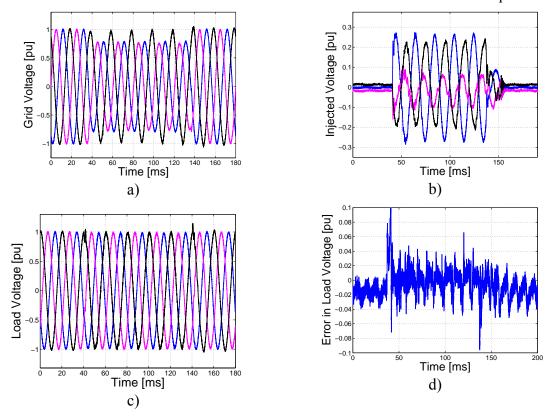

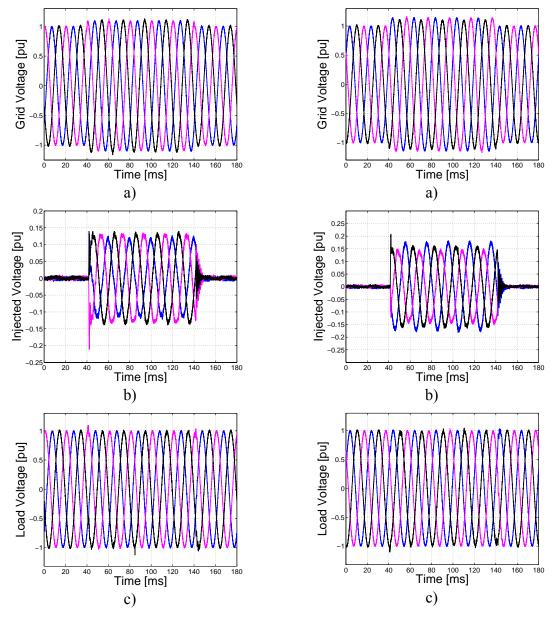

| 3.7. | Mi            | TIGATION OF HARMONICS                       | 65    |

| 3.8. | Co            | NTROL OF ENERGY FLOW                        | 67    |

| 3.   | .8.1.         | Startup                                     | 67    |

| 3.   | .8.2.         | Minimization of Active Power                | 67    |

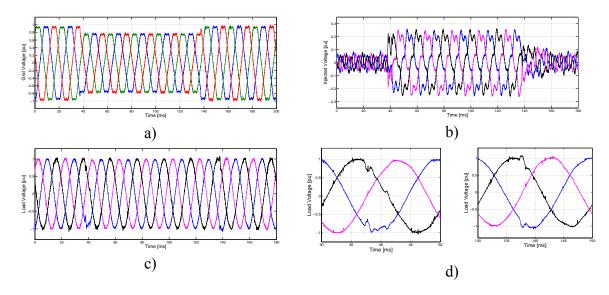

| 3.9. | PEI           | RFORMANCE OF SSC DUE TO POWER SYSTEM EVENTS | 68    |

| 3.10 | ). <b>S</b> U | MMARY OF CHAPTER 3                          | 70    |

| 4.   | CON           | ICLUSIONS AND RECOMMENDATIONS               | 71    |

| 4.1. | Int           | TRODUCTION                                  | 71    |

| 4.2. | Co            | NCLUSIONS                                   | 71    |

| 4.3. | RE            | COMMENDATIONS                               | 75    |

| REFE | EREN          | CES                                         | 77    |

| PAPE | ER A          |                                             |       |

| POW  | ER E          | LECTRONICS FOR POWER QUALITY IMPROVEMENT    | ΓSA.1 |

| PAPE | ER B          |                                             |       |

| СТАТ | TIC SI        | ERIES COMPENSATOR FOR MITIGATION OF VOLTAGE | CF    |

|      |               | ERIES COMPENSATOR FOR MITIGATION OF VOLTAGE |       |

| PAPE |               |                                             |       |

|      |               | NT PERFORMANCE IMPROVEMENTS OF STATIC SER   | IES   |

|      |               | SATOR BY DOUBLE VECTOR CONTROL              |       |

|      |               |                                             |       |

| PAPER D                                                                                             |

|-----------------------------------------------------------------------------------------------------|

| MITIGATION OF UNBALANCED VOLTAGE DIPS USING STATIC SERIES COMPENSATORD.1                            |

| PAPER E                                                                                             |

| TUNING SOFTWARE PHASE-LOCKED LOOP FOR STATIC SERIES COMPENSATORE.1                                  |

| PAPER F                                                                                             |

| TESTING STATIC SERIES COMPENSATOR AGAINST CAPACITOR BANK ENERGIZINGF.1                              |

| PAPER G1                                                                                            |

| ENERGY FLOW CONTROL BETWEEN STATIC SERIES COMPENSATOR AND DISTRIBUTION SYSTEMSG1                    |

| PAPER G2                                                                                            |

| ENERGY OPTIMIZATION CONTROL TECHNIQUES BY STATIC SERIES COMPENSATOR FOR CONSTANT POWER FACTOR LOADS |

| PAPER H                                                                                             |

| OPERATION OF STATIC SERIES COMPENSATOR UNDER DISTORTED UTILITY CONDITIONS                           |

| PAPER I                                                                                             |

| OPERATION OF STATIC SERIES COMPENSATOR UNDER DISTORTED UTILITY CONDITIONSI.1                        |

#### **CHAPTER**

# 1. INTRODUCTION

#### 1.1. BACKGROUND AND MOTIVATION

Modern industrial processes are based on a large amount of electronic devices such as programmable logic controllers and adjustable speed drives. Unfortunately, electronic devices are sensitive to disturbances, and thus, industrial loads become less tolerant to power quality problems such as voltage dips, voltage swells, and harmonics.

Voltage dips are considered the most severe disturbances to the industrial equipment [1,2]. A paper machine can be affected by disturbances of only 10 % voltage drop lasting for 100 ms [3]. A voltage dip of 75 % (of the nominal voltage) with duration shorter than 100 ms can result in material loss in the range of thousands of US dollars for the semiconductors industry [4].

Swells and overvoltages can cause overheating, tripping or even destruction of industrial equipment such as motor drives, surge arrestors and control relays. From the reference [5], the following statement is quoted: " There are about 100 million US Dollars direct losses of damaged electronic devices caused by lightning overvoltage in Shanghai, China, 1999. So, adopting effective measurements and devices to protect these electronic systems from being damaged by electromagnetic impulse and overvoltage is very urgent."

Harmonic contamination has become a problem to sensitive loads. The effect of harmonic distortion on equipment and power system operation is documented in many textbooks such as [6] and [7], and in research publications, for instance [8] and [9]. The electronic equipment is a very sensitive load against harmonics because their control depends on either the peak value, or the zero crossing of the supplied voltage, which are all influenced by the harmonic distortion.

To overcome the mentioned problems, the concept of custom power has been introduced recently [2,10]. Custom power is a strategy, which is designed primarily to meet the requirements of industrial and commercial customers. The concept of custom power is to use power electronics or static controllers in the medium voltage distribution system aiming to supply reliable and high-quality power to sensitive users.

Power electronic valves are the basis of those custom power devices such as the static transfer switch, active filters and converter-based devices. Converter-based power electronics devices can be divided into two main groups: shunt-connected and series-connected devices. Both shunt- and series-connected devices have been proposed in literature for the medium-voltage applications. The shunt-connected device is known as the Distribution Static Compensator (DSTATCOM) [11,12] and the series device is known as the Static Series Compensator (SSC), commercially known as the dynamic voltage restorer [3, 13, 14, 15]. It has also been reported in literature that both the SSC and DSTATCOM have been used to mitigate the majority of the power system disturbances such as voltage dips, swells, flicker, unbalance and harmonics [11-15]. The SSC is best suited to mitigate voltage dips and unbalanced grid voltages, where it can inject a voltage in series with the supply voltage to keep the voltage constant at the load. The dynamic performance of the SSC is important since the load should not be exposed to voltage dips at all in order to maintain a reliable operation.

The thesis focuses on the control of the SSC in order to improve the transient and the steady-state responses and the injection capability. The injecting capability of the SSC is not only influenced by the control algorithm but also limited by the size of the energy storage device employed. Thus, a study of the energy storage is carried out when using a capacitor bank as the energy storage device. Three power quality issues are mainly investigated in the thesis: 1) voltage dips; 2) voltage swells; 3) voltage harmonics. For each problem, a control algorithm is developed and implemented in order to ensure the successful operation of the SSC.

#### 1.2. CONTRIBUTIONS

# 1.2.1. Modeling and Simulation of SSC

A simulation model incorporating the SSC, the grid and different load types is developed and implemented in PSCAD/EMTDC. The model combines both the existed component models and the user-defined models. User-defined models are designed using the FORTRAN language and they are mainly built in the controller of the SSC.

# 1.2.2. Double Vector Controller for Balanced Dips

A control algorithm is developed and implemented in order to mitigate the balanced voltage dips. It is based on the vector control approach and consists of two control loops. Thus, the developed control algorithm is referred to as the Double Vector Control (DVC) algorithm.

The DVC incorporates both voltage and current controllers and it has improved the transient performance of the SSC. The response time of the DVC is considerably fast. Thus, the load voltage is restored within this response time (less than 4 ms) in case of balanced voltage dips.

#### 1.2.3. Mitigation of Unbalanced Dips

Two control strategies have been proposed and implemented in order to mitigate unbalanced voltage dips by the SSC. The first strategy uses a fast technique for separating positive and negative sequence components of the supply voltage, which are then controlled separately. Thus, two controllers are implemented for the two sequences, each based on the vector control. The second strategy is based on using only a positive sequence controller and increasing the switching frequency.

#### 1.2.4. Software Phase Locked Loop

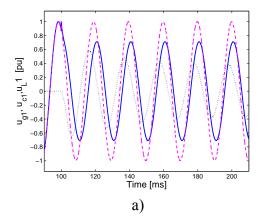

A software phase-locked loop (SPLL) with a PI controller has been proposed for the SSC applications. A criterion to tune the SPLL is developed and the gains of the PI controller are determined to obtain the desired transient performance and moreover filter out the harmonics of the grid voltage. The proposed SPLL plays an important role to control the flow of the electrical energy between the SSC and the grid. The proper gains of the PI controller are selected in order to obtain the correct phase information of the grid voltage for the different compensation strategies.

# 1.2.5. Control and Optimization of Energy Flow

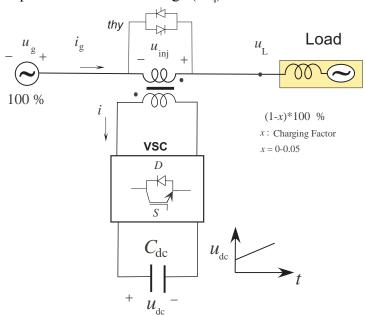

#### Startup of SSC

During startup of the SSC, the voltage source converter (VSC) of the SSC is used to charge its energy-storage capacitor. Thus, the proposed charging procedure is called the self-charging technique. Two options have been proposed: 1) the phase angle of the load voltage is constant; 2) the magnitude of the load voltage is constant. A charging control algorithm has been proposed and implemented in each case. The factors affecting the design of the energy storage-capacitor have been investigated and a design guide for the energy-storage capacitor is given.

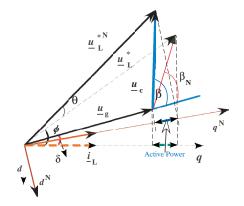

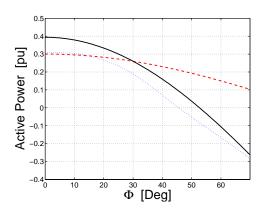

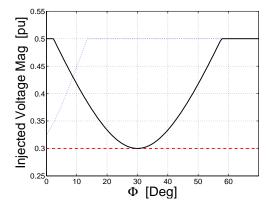

# Minimization of Active Power Requirements

Minimization of the injected active power is realized by injecting a voltage with the proper phase shift with respect to the load current. This idea has been proposed in literature and referred to as the Phase Advance Compensation (PAC). However, in some cases, the PAC may fail to minimize the active power because of the power factor of the load. Thus, four different compensation strategies have been studied in order to ensure the minimization of the active power: 1) Voltage Difference Compensation; 2) In-Phase Compensation; 3) Phase Advance Compensation; 4) Progressive Phase Advance Compensation. The effect of the load power factor on the compensation techniques has been investigated. A control algorithm based on a combination of the four strategies is proposed taking into account the

issues: 1) minimization of the active power; 2) keeping the injected voltage within the ratings of the SSC; 3) smoothing the load voltage waveform.

#### 1.2.6. Controller for Mitigation of Voltage Dips and Harmonics

A control algorithm to mitigate the voltage dips and harmonics has been developed and implemented experimentally. A moving average filter is employed to extract the fundamental components of the measured voltages and currents. Those are needed to control the performance of the SSC. Also, an active filtering capability is added by using the resonant filters for the 5<sup>th</sup> and the 7<sup>th</sup> harmonics. With this algorithm both the fundamental component and harmonics are accurately detected and controlled.

#### 1.2.7. Mitigation of Voltage Swells and Overvoltage Protection

The possibility of employing the SSC to mitigate voltage swells/overvoltages has been investigated theoretically and experimentally. An overvoltage protection scheme has been proposed to protect the SSC online and offline. The online overvoltage protection is based on using a dc chopper with a resistor. The design of the dc resistor has been discussed.

#### 1.2.8. Influence of Power System Events on SSC Performance

A number of power system events have been described and simulated. The simulated events are: short-circuit faults; capacitor-bank energizing; transformer energizing; load switching (induction motor start, diode rectifier start). The performance of the SSC with the DVC algorithm has been examined for each event. Moreover, the case of capacitor bank energizing was studied in more details because the capacitor bank switching results in a sustained overvoltage and a voltage transient.

#### 1.3. THESIS OUTLINE

The thesis is composed of this introductory chapter, three chapters, and ten papers (publications) arranged as follows:

Chapter 2 presents the system description and the developments of the research work. General description of the SSC is given and different converter topologies are explored. All the developed controllers are explained and the investigated topics are discussed.

The results of the simulations and experiments are analyzed in Chapter 3.

Chapter 4 introduces the conclusions of the research work and proposes further research topics based on the achievements of this work.

Paper A presents an overview of the power electronics controllers used for power quality improvements. The definitions and examples of the power quality problems are given. The focus was given on the voltage dips, as they are the most severe problem to industrial loads.

Some solutions to mitigate the power quality problems by using the power electronics apparatus are explored.

The operational principle, configuration, design criteria, and rated power estimation of the SSC are explained in Paper B. The used control techniques are discussed aiming to compromise among them based on their suitability with the SSC requirements.

In Paper C, the principle and verification of the DVC algorithm are presented. The loop gains are determined according to the system stability analysis, carried out on the closed loop system. Experiential results on a 10 kV SSC setup are shown with different load types: static linear; dynamic linear and nonlinear loads.

Mitigation of unbalanced voltage dips is investigated in Paper D. Two control strategies to improve the dynamic performance of the SSC are presented. The first strategy uses a fast technique for separating positive and negative sequence components of the supply voltage, which are then controlled separately. The second strategy is based on using only a positive sequence controller and increasing the switching frequency.

Paper E proposes a software phase-locked loop (SPLL) with a PI controller for the SSC applications. A tuning criterion for the SPPL is developed to satisfy the frequency requirement of most of the loads. It is also discussed that by using proper selection of the gains, the SPPL behaves as a low pass filter. Thus, the harmonics in the grid voltage may not affect the steady-state performance of the SPLL.

In Paper F, the performance of the SSC due to upstream capacitor bank energizing is studied. Upstream capacitor-bank energizing leads to a transient at the terminals of the SSC followed by a sustained overvoltage. Simulation results of a PSCAD/EMTDC system model with upstream capacitor bank energizing are presented.

The control and optimization of the power flow between the SSC and the grid is described in Paper G1 and Paper G2. This part consists of two main parts: 1) startup of the SSC; 2) minimization of the active power requirements. The first part considers the charging of the energy storage by either a shunt diode rectifier or by the voltage source converter of the SSC itself. The second part proposes a control algorithm based on different compensation strategies in order to minimize the required active power and also keeps the injected voltage by the SSC within its ratings.

Paper H discusses the capability of the SSC to mitigate voltage swells. The consequences of the voltage swells on the SSC are identified. Simulations and experiments are carried out to show the ability of the SSC to mitigate voltage swells. Also an overvoltage protection scheme is proposed and designed. The overvoltage protection of the SSC is realized either online to mitigate voltage swells or offline to bypass the SSC.

In Paper I, the functionality of the SSC is extended to work as a series active filter. A control algorithm is developed and implemented to mitigate voltage dips and harmonics. The developed controller consists of three main parts: 1) extraction of the fundamental component by a moving average filter; 2) control of fundamental component by the DVC; 3) extraction and control of the voltage harmonics by the resonant filters. The operation of the SSC under distorted utility conditions is discussed and some recommendations are given.

#### **CHAPTER**

# 2. SYSTEM DESCRIPTION AND DEVELOPMENTS

#### 2.1. Introduction

Power quality problems encompass a wide range of disturbances that can disrupt the operation of sensitive industrial loads and cause a loss of production. The following power quality problems have been identified in a number of standards such as [16,17] and textbooks such as [18, 19]:

- short interruptions;

- voltage dips;

- voltage swells/overvoltages;

- voltage and current transients;

- voltage and current harmonic distortion;

- voltage flicker;

- unbalance;

- power frequency variations.

A description of most of the mentioned power quality problems is given in Paper A. To many consumers of electrical energy, especially industrial consumers, voltage dips are the most important power quality disturbance in the power systems [2, 3]. The outage costs associated with poor power quality are documented and serve as an argument to study the possibility of using power conditioning equipment [4]. The effects of voltage dips, swells and flickers on end-users have been formulated in the literature such as [1-6]. Dips, depending on the severity and duration, can cause computer resets, memory loss, tripping of adjustable speed drives, loss of motor loads, and this in turn leads to serious disruption of the production process.

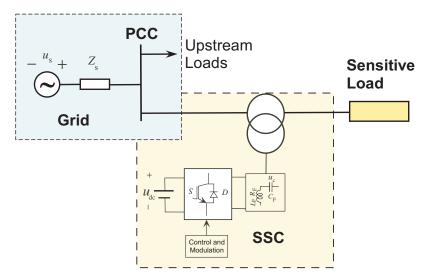

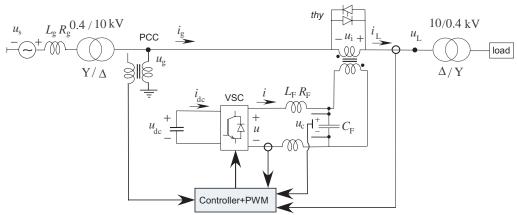

The fast development and continuous innovation of valves and controllers for power electronics have made it possible to solve the power quality problems by using grid-connected voltage source converters (VSCs). The VSC, connected in series with the grid as a static series compensator (SSC), also known (commercially) as the dynamic voltage

restorer (DVR), is best suited to protect the sensitive loads against the voltage dips. In principle, the SSC injects by means of three single-phase transformers three voltages in the grid, synchronized in such a way that the load voltage magnitude and phase are constant at any instant to guarantee continued operation for the load. On August 26, 1996, the world's first SSC was installed on the Duke Power distribution system to protect a sensitive textile customer from voltage dips [13].

As mentioned in Chapter 1, the control of the SSC is the main issue of the thesis. This Chapter introduces the motivation and presents the developments of the research work. A brief description of the SSC is given. The controllers to mitigate three power quality problems (dips, swells and harmonics) are derived. Also other related subjects such as the software phase-locked loop and energy flow are discussed.

#### 2.2. VOLTAGE DIPS

A voltage dip is a decrease in the RMS voltage from 0.1 to 0.9 pu at the power frequency for duration from 0.5 cycles to 1 minute [17].

A synonym for the voltage dip is the voltage sag, which is widely used in the United States [19]. The voltage dips have the potential to disrupt the operation of the sensitive loads and cause a loss of production. It is worth to mention that the voltage dips are the main topic of the textbook [18]. The mean causes of voltage dips are the short-circuit faults in the transmission and distribution systems [19]. Also the large induction motors when starting and the transformers when being energized result in voltage dips. In some networks, switching on large loads may cause voltage dips. The voltage dips due to short-circuit faults are characterized by a dip magnitude, a dip duration, and a phase-angle jump.

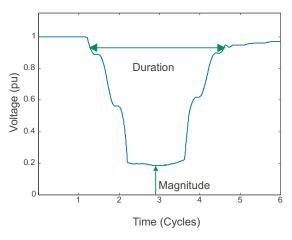

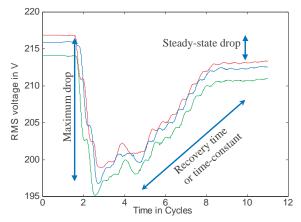

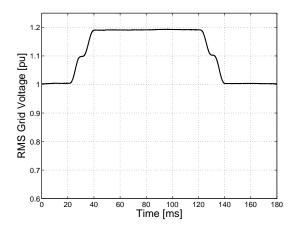

The voltage dip magnitude is the retained voltage after the initiation of the dip. It can be determined by either the RMS voltage or the peak voltage over half a cycle or one cycle of the fundamental frequency. An example of a voltage dip due to short circuit fault is shown in Fig.2.1 and an example due to motor start is shown in Fig.2.2. In the case of voltage dips due to motor start, the characterization needs to be slightly different: other terms are involved such as recovery time and steady state drop (as illustrated Fig.2.2). The duration of the dip is the time at which the system voltage remains under a threshold value, for instance 90% of the pre-dip voltage.

If the dip is due to a short-circuit fault, the dip duration is mainly determined by the fault clearing time, which is affected by the speed of the protection and the speed of the circuit breakers. The phase-angle jump is a shift in the zero crossing of the instantaneous voltage. Because the system voltage is a complex quantity consisting of a magnitude and phase angle, an event like a short-circuit fault may not only affect the voltage magnitude but also its phase angle. Normally, voltage dips originated because of short-circuit faults are associated with a phase-angle jump.

Fig.2.1. Example of voltage dip due to short-circuit fault.

Fig.2.2. Example of voltage dip due to motor start.

# 2.3. STATIC SERIES COMPENSATOR

#### 2.3.1. Operational principle of Static Series Compensator

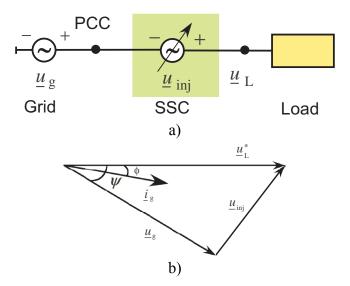

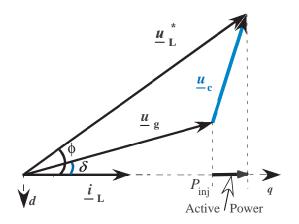

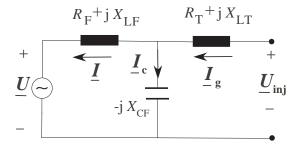

The SSC is a power-quality device that protects highly sensitive loads, mainly industrial loads, against the common disturbances of the power system such as voltage dips and swells. Normally, the SSC is connected in series with the distribution feeder at the medium voltage levels [3]. In principle, the SSC can be installed at any voltage level, but for the low voltage applications, the SSC may be cost-ineffective compared to the uninterruptible power supply. To be able to mitigate voltage dips/swells, the SSC should be capable of generating and absorbing active and reactive power to or from the grid. Basically, the SSC is designed to dynamically inject a voltage  $\underline{u}_{inj}$  into the power system as shown in Fig.2.3. Fig.2.3a shows a simplified single-phase equivalent circuit of a distribution feeder with an SSC where the supply voltage  $\underline{u}_{inj}$ , the injected voltage  $\underline{u}_{inj}$  and the load voltage  $\underline{u}_{L}$  are in series. So, the SSC is considered to be an external voltage source where the amplitude, the frequency and the phase of  $\underline{u}_{inj}$  can be controlled.

The purpose is to maintain the amplitude of the load voltage fixed and prevent phase jumps. A phasor diagram of a voltage dip with a phase jump is shown in Fig.2.3b. From Fig.2.3, the load voltage is deduced:  $\underline{u}_L = \underline{u}_g + \underline{u}_{inj}$ . If the supply voltage  $\underline{u}_g$  has dropped due to a voltage dip or increased due to a voltage swell, the injected voltage by the SSC ( $\underline{u}_{inj}$ ) should be controlled so that the load voltage  $\underline{u}_L$  remains the same as during no-disturbance conditions. In Fig.2.3a, the SSC is modeled as an ideal voltage source while it is composed of many components in practice. The layout of the SSC is presented in Subsection 2.3.2 and the description of its individual components is given in Paper B.

Fig.2.3. Illustrative diagram of operational principle of Static Series Compensator: a) grid, Static Series Compensator and load are in series, b) phasor diagram of voltage dip with phase angle jump.

#### 2.3.2. Layout and Design of SSC

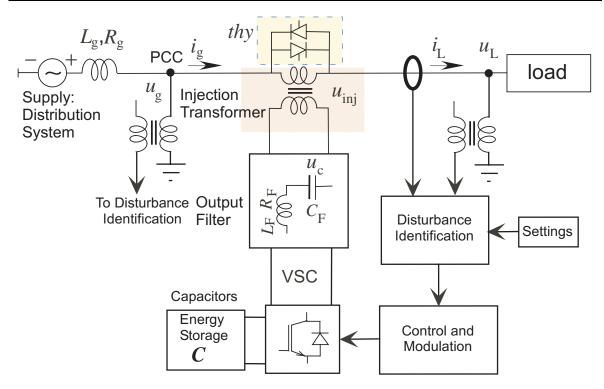

The SSC components (shown in Fig.2.4) are the VSC, the modulation unit, the control unit, the output filter, the injection transformer, the energy storage and the bypass switch. The measured voltages and currents are the inputs to the disturbance identification, which gives signals to the control unit to function when the measured quantities differ from the settings of the controller. The disturbance identification module triggers the start of the compensation when the supply voltage comes outside of a pre-defined range. Then the control unit generates the voltage references. The voltage references are the inputs to the modulation unit to generate the modulating signals for the valves of the VSC. The energy storage provides or absorbs the required active power to compensate the identified voltage dip/swell. Installing an output filter between the VSC and the injection transformer reduces the dv/dt effect on the windings of the injection transformer. Thus the filter converts the pulse-modulated voltage of the VSC into a sinusoidal voltage. The filtered voltage is injected into the distribution system by the series-injecting transformer. The bypass switch is normally closed to short-circuit the SSC. When the disturbance identification unit detects a voltage dip/swell, the bypass switch is opened and the SSC starts the compensation process. Because the VSC is the basic component of the SSC, it is treated in this Chapter while a detailed description of the SSC is presented in Paper B.

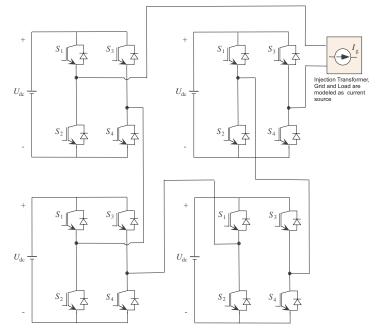

# 2.3.3. Converter Topologies for SSC

The VSC is the core element of the SSC design since the main function (generating the injected voltage) is performed through it. Different topologies of the VSC have been proposed in literature with the SSC applications. Among those are: 1) the half-bridge topology; 2) the full bridge topology; 3) the multi-level VSC.

Fig.2.4. Single-line diagram of Static Series Compensator including details of VSC, LC-filter and measured signals for control.

#### Half Bridge Topology

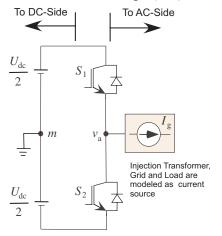

The half bridge topology is the basic configuration of the VSC, which is known as the six-pulse forced-commutated converter. For simplicity, a single-phase half-bridge circuit is displayed in Fig.2.5. Each phase of the ac side, which is connected to one of the three legs of the converter, is modeled as a current source ( $I_g$ ) since the SSC is connected in series with the grid. The circuit contains six valves; each valve may consist of a number of semiconductor devices in series or in parallel. For instance, the semiconductor device used in Fig.2.5 is the insulated gate bipolar transistor (IGBT), with an anti-parallel diode. The restriction is that three valves are conducting at the same time, but only one valve in each bridge-leg. Hence the phase potentials  $v_a$ ,  $v_b$ , and  $v_c$  at each phase leg, referred to the midpoint of the dc-voltage supply m, are determined by the conducting states of the valves. Each phase potential is either  $U_{dc}/2$  or  $-U_{dc}/2$ .

#### Full Bridge Topology

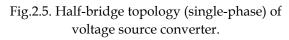

In the Full-bridge topology of the VSC, the converter has six legs (12 valves) and each phase of the ac side is connected to two of these legs. For instance, the circuit of the phase a is shown in Fig.2.6. The voltage of the phase a is the difference between the potentials  $v_{a1}$  and  $v_{a2}$ . This topology has the advantages: 1) the injected voltage is double of the injected voltage by the half-bridge topology; 2) it enables the control of the zero sequence voltage (if the injection transformer is not delta-connected). The disadvantage is that the number of valves is the double compared to the half-bridge circuit.

#### Multilevel VSC

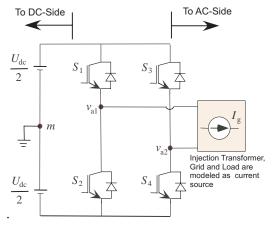

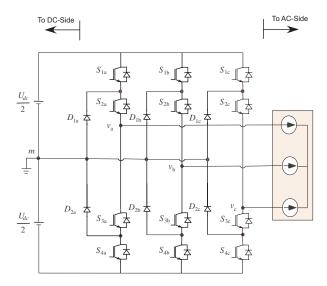

The multi-level VSC has been proposed to reduce the harmonic content [20], even with a square wave modulation, because it provides the possibility to have different voltage levels. A multi-level VSC can be realized either by the neutral point clamping (as shown in Fig.2.7) or by using a multi-bridge VSC as illustrated in Fig.2.8 [21]. In the case of a three-level, VSC, neutral point clamped (NPC), the output voltage of the VSC can have one of the three values  $+U_{\rm dc}/2$ , 0, and  $-U_{\rm dc}/2$ . A scheme of the NPC VSC is shown in Fig.2.7. The NPC VSC converter (shown in Fig.2.7) is an alternative to the two-level converter in high power applications. Each phase can be connected to the positive dc terminal by firing  $S_{\rm 1n}$  and  $S_{\rm 2n}$  simultaneously while  $S_{\rm 3n}$  and  $S_{\rm 4n}$  are off. Firing  $S_{\rm 3n}$  and  $S_{\rm 4n}$  while  $S_{\rm 1n}$  and  $S_{\rm 2n}$  are off connects the negative dc terminal to the phase n (n = a, b, and c). If  $S_{\rm 2n}$  and  $S_{\rm 3n}$  are on and  $S_{\rm 1n}$  and  $S_{\rm 4n}$  are off, the phase n is connected to the midpoint of the dc side, zero potential. The three-level converter requires six extra diodes if it is compared to the two-level converter to clamp the phases to the zero potential.

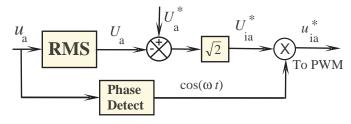

#### 2.4. CONTROL OF STATIC SERIES COMPENSATOR

The reported control techniques that have been implemented to control the injected voltage by the SSC may be classified into two main categories: 1) the scalar; 2) the vector control. By the scalar control, it is meant that only the voltage magnitude is controlled by applying the concept of phasors as in [22,23]. Techniques based on the synchronous reference frame [24-31] are referred to as vector control where the magnitude and the phase of the injected voltage are controlled. The scalar control involves the RMS calculation of the fundamental voltage [22,23], which requires at least one half period of the fundamental frequency. A block diagram (single-phase) of the scalar control is shown at Fig.2.9, where the input to the controller is the instantaneous phase voltage of the grid  $(u_a)$ . Then the RMS calculations are made online to determine the RMS grid voltage  $(U_a)$ , which is then subtracted from the reference of the load voltage  $(U_a)$ .

Fig.2.6. Full-bridge topology (single-phase) of voltage source converter.

Fig. 2.7. Three-level Neutral Point Clamped Voltage Source Converter.

Fig.2.8. Multi-bridge Voltage Source Converter.

The amplitude reference of the injected voltage is obtained by multiplying this difference by  $\sqrt{2}$  to obtain the magnitude of the injected voltage. It should be stated that the phase of the voltage reference is obtained by a phase detector, which is synchronized to the grid voltage. The scalar control works fine in the steady state, but it slows the dynamic performance of the SSC and only the fundamental voltage can be controlled unless an FFT algorithm is included and harmonic components are detected.

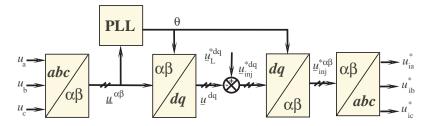

To improve the transient response of the SSC and control the injected active and reactive powers separately, the vector control has been implemented in a way similar to the control of variable speed drives. Both the feedforward/open-loop [24] and feedback/closed loop [25-31] techniques have been reported. A block diagram of the basic feedforward control of

the SSC is depicted at Fig.2.10. The grid voltages  $(u_a, u_b, u_c)$  are measured and transformed to the stationary reference frame  $(\underline{u}^{\alpha\beta})$ . A phase locked loop (PLL) is exploited to calculate the transformation angle  $(\theta)$ , which is required to transform the grid voltage from the stationary reference frame to the synchronous reference frame  $(\underline{u}^{dq})$ . Then the grid voltage is subtracted from the reference of the load voltage  $(\underline{u}_{L}^{*dq})$  to calculate the reference of the injected voltage  $(\underline{u}_{inj}^{*dq})$ . A backward transformation from the synchronous reference frame to the three-phase is performed in order to obtain the reference of the injected voltage  $(u_{ia}^{*}, u_{ib}^{*})$  that should be generated by the VSC. The feedforward control is fast but does not guarantee the system stability and may exhibit a steady-state error.

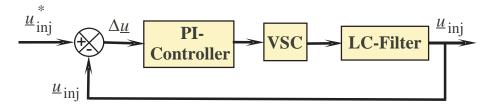

Feedback control of the SSC has been proposed in [25] where the injected voltage by the SSC is measured and used in a single-loop [25,31] or a multi-loop [29,30] control system. A block diagram of a single-loop feedback control system is displayed in Fig.2.11. In feedback control systems (applied to the SSC), an error signal ( $\Delta \underline{u}$ ) is generated by subtracting the actual injected voltage ( $\underline{u}_{inj}$ ) from the reference of the injected voltage ( $\underline{u}_{inj}^*$ ). This error signal is fed to a PI controller to obtain the reference of the voltage that should be generated by the VSC.

When designing a control algorithm for the SSC, the LC-filter, mounted at the output of the VSC as shown in Fig.2.4, is important to consider since it affects the dynamic performance of the SSC. Moreover, the LC-filter causes a voltage drop on the choke branch, which reduces the injection capability of the SSC and introduces a phase shift in the injected voltage. Such effect has been considered in [26,27,28,29]. In [26,27], a simple back calculation of the filter input voltage is applied. The algorithm proposed in [27] compensates for the steady state voltage drop due to the LC-filter but it gives poor transient performance and it is sensitive to variations of the LC-filter parameters.

Fig.2.9. Scalar control of Static Series Compensator.

Fig.2.10. Feedforward vector control of Static Series Compensator.

Fig.2.11. Feedback vector control of Static Series Compensator.

To overcome this problem of voltage drop across the LC-filter and improve the performance of SSC, the voltage and current controllers are incorporated as in [29] and [30]. In [29], the current control loop is formed by measuring the capacitor current and feeding it back to the controller. While in [30] the current loop is formed by the inductor current. As the inductor current should be measured for the overcurrent protection and it may help in actively damping the resonance between the LC-filter inductor and capacitor, then the inductor current is used in the current loop feedback as discussed in [30].

# 2.5. DOUBLE VECTOR CONTROL FOR MITIGATION OF BALANCED DIPS AND SWELLS

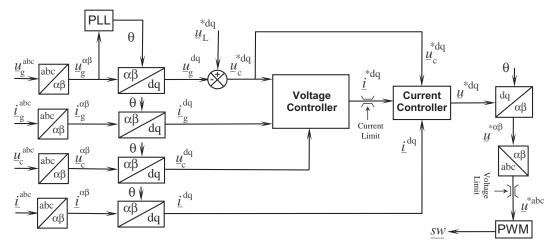

#### 2.5.1. Derivation of Double Vector Controller

The dynamic performance of the SSC may be improved by controlling both the inductor current and the capacitor voltage of the LC-filter. Thus, a two-loop control algorithm is proposed in this thesis and it is referred to as Double Vector Control (DVC). To reduce the complexity of the system while deriving the DVC equations, the injecting transformer (Fig.2.4) is assumed ideal i.e., having zero magnetizing current and zero leakage inductance, with turns ratio of 1:1. Also the transformer, the grid and the load are replaced by an equivalent current source. Consequently, the injected voltage by the SSC,  $\underline{u}_{inj}$  is the same as the voltage across the LC-filter capacitor  $\underline{u}_c$ . Hence, the capacitor voltage  $\underline{u}_c$  is controlled to regulate the load voltage. The current through the LC-filter inductor is controlled by an inner control loop. To derive the controllers, the LC-filter is modeled in the stationary  $\alpha\beta$ -frame and transformed into the synchronous reference frame as in (2.1).

$$\frac{d}{dt}\mathbf{x}(t) = \mathbf{A}_{LC}\mathbf{x}(t) + \mathbf{B}_{LC}\mathbf{u}(t), \qquad \mathbf{y}(t) = \mathbf{C}_{LC}\mathbf{x}(t)$$

(2.1)

where  $\mathbf{x}(t) = \begin{pmatrix} i_{\rm d} & i_{\rm q} & u_{\rm cd} & u_{\rm cq} \end{pmatrix}^{\rm T}$ ,  $\mathbf{u}(t) = \begin{pmatrix} u_{\rm d} & u_{\rm q} & i_{\rm gd} & u_{\rm gq} \end{pmatrix}^{\rm T}$ ,

$i_d$ ,  $i_q$  are the d- and q-components of the inductor current,

$u_{\rm cd}$ ,  $u_{\rm cq}$  are the d- and q-components of the injected voltage,

$u_d$ ,  $u_q$  are the d- and q-components of the VSC voltage,

$i_{\mathrm{gd}},\,i_{\mathrm{gq}}$  are the d- and q-components of the grid current .

The aim of the controller is to keep the load voltage constant. Thus, the SSC should inject the voltage  $u_c^{*dq}$  such that

$$\underline{u}_{c}^{*dq} = \underline{u}_{L}^{*dq} - \underline{u}_{g}^{dq} \tag{2.2}$$

where  $\underline{u}_{L}^{*dq}$  is the reference voltage demanded by the load and  $\underline{u}_{g}^{dq}$  is the grid voltage in the dq-frame. The missing voltage  $\underline{u}_{c}^{*dq}$  is injected through the injecting transformer. The inputs to the controller are the grid voltages, the grid currents, the inductor currents and the capacitor voltages of the LC-filter. The proposed controller is a discrete controller and uses a sampling time of  $T_{s}$ . Hence the sampling frequency  $f_{s}$  equals to  $1/T_{s}$ . The switching frequency  $f_{sw}$  is the same as the sampling frequency. The state-space equation of the LC-filter, (2.1) is discretized using the forward Euler method [32] and is then integrated from  $kT_{s}$  to  $(k+1)T_{s}$  (one sample period), as given in (2.3).

$$\mathbf{x}(k+1) = \mathbf{A}_{LCD}\mathbf{x}(k) + \mathbf{B}_{LCD}\mathbf{u}(k), \qquad \mathbf{y}(k) = \mathbf{C}_{LCD}\mathbf{x}(k)$$

(2.3)

The following assumptions are made to derive the controller:

- The grid current is constant independently of the variations in the currents and voltages of the LC-filter;

- The capacitor voltage and the inductor current change linearly during one sample;

- The controller uses a dead-beat gain; the output vector  $\mathbf{y}(k)$  changes linearly and is equal to the reference output vector  $\mathbf{y}^*(k)$  after one sample;

- The average values of the capacitor voltage and the inductor current over the sample period  $kT_s$  to  $(k+1)T_s$  are each equal to half of the summation of the real value and the reference value at the sample k.

The controlled variables are the inductor current  $\underline{i}^{dq}$  and the capacitor voltage  $\underline{u}_{c}^{dq}$ . Based on the above assumptions and after algebraic manipulation of (2.3), the equations of the controller are obtained as:

$$\underline{i}^{*dq} = \underline{i}_{g}^{dq} \pm \underline{j} \frac{\omega C_{F}}{2} \left\{ \underline{u}_{c}^{*dq} + \underline{u}_{c}^{dq} \right\} + K_{u} \left\{ \underline{u}_{c}^{*dq} - \underline{u}_{c}^{dq} \right\}$$

(2.4)

$$u^{*dq} = \underline{u}_{c}^{*dq} + R_{F}\underline{i}^{dq} \pm j\frac{\omega L_{F}}{2} \left\{ \underline{i}^{*dq} + \underline{i}^{dq} \right\} + K_{p} \left\{ \underline{i}^{*dq} - \underline{i}^{dq} \right\}$$

(2.5)

where  $\underline{i}^{*dq}$  and  $\underline{u}^{*dq}$  are the required reference currents and voltages to track the reference of the injected voltage. The gains  $K_u$  and  $K_p$  are the dead-beat gains and they are calculated in terms of the LC-filter parameters ( $R_F$ ,  $L_F$ , and  $C_F$ ) and the sampling time;  $K_u = C_F/T_s$ ,  $K_p = L_F/T_s + R_F/2$ . In (2.4) and (2.5), j means a 90° phase shift which implies the cross coupling between the d- and the q-components. A block diagram of the DVC is depicted in Fig.2.12. In Fig.2.12, voltage and current limits are set in the controller in order to avoid overmodulation and limit the inductor current. To stabilize the system, the gains  $K_u$  and  $K_p$  are altered from the dead-beat gains by the factors  $K_{us}$  and  $K_{ps}$ , respectively. In other words, the gains of the two loops are given by:  $K_u = K_{us} C_F/T_s$  and  $K_p = K_{ps} (L_F/T_s + R_F/2)$  Thus, selecting the values of the two factors  $K_{us}$  and  $K_{ps}$  determines the system stability.

Fig.2.12. Block diagram of double vector control.

#### 2.5.2. Stability Analysis

To perform a stability analysis for the system, the closed-loop model of the system with the proposed controller is derived. The closed loop system implies the relation between the system inputs and the controlled variables. In this case, the system inputs are the reference of the capacitor voltage  $\underline{u}_c^{*dq}$  and the grid current  $\underline{i}_g^{dq}$ , which is considered as a disturbance.

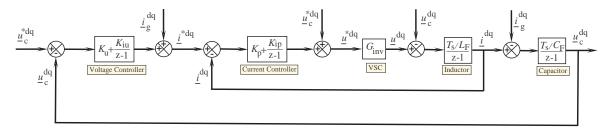

While the controlled variables are  $\underline{u}_{c}^{dq}$  and  $\underline{i}^{dq}$ . A block diagram of the derived closed loop system is displayed at Fig.2.13, where  $G_{inv}$  is the transfer function of the VSC. In the derived model,  $G_{inv}$  is a linear function with a unity slop ( $\underline{u}^{dq} = \underline{u}^{*dq}$ ) and saturates if the reference voltage is outside the range  $\pm$  1 pu (1 pu = rated dc voltage of the VSC, for a full-bridge topology of VSC). The closed-loop model is written in a state-space form as:

$$\mathbf{x}(k+1) = \mathbf{\Phi}_{LC}\mathbf{x}(k) + \mathbf{\Gamma}_{LC}\mathbf{u}(k)$$

(2.6)

Where:  $\mathbf{x}(k) = (i_{\rm d} \quad i_{\rm q} \quad u_{\rm cd} \quad u_{\rm cq})^{\rm T}$  and  $\mathbf{u}(k) = (u_{\rm cd}^* \quad u_{\rm cq}^* \quad i_{\rm gd} \quad i_{\rm gq})^{\rm T}$ . The matrices  $\mathbf{\Phi}_{\rm LC}$  and  $\mathbf{\Gamma}_{\rm LC}$  are calculated after discretizing the filter model (2.1) and combined with the controller (2.4) and (2.5). The stability of Linear Time Invariant (LTI) systems is determined by the location of the eigenvalues of the matrix  $\mathbf{\Phi}_{\rm LC}$  with respect to the unit-radius disk [32]. The LTI system is asymptotically stable if all the eigenvalues of the matrix  $\mathbf{\Phi}_{\rm LC}$  are located inside the unit disk. If  $\lambda_i$  is an eigenvalue of the matrix  $\mathbf{\Phi}_{\rm LC}$ , then the system is asymptotically stable if and only if:  $|\lambda_i| < 1 \ \forall i = 1 \ to \ 4$ . The study of the system stability is equivalent to variation of the factors  $K_{\rm us}$  and  $K_{\rm ps}$  such that the inequality  $|\lambda_i| < 1 \ \forall i = 1 \ to \ 4$  is satisfied. To calculate the eigenvalues of the matrix  $\mathbf{\Phi}_{\rm LC}$ , the determinant of the matrix  $(\lambda \mathbf{I} - \mathbf{\Phi}_{\rm LC})$  is set to zero. This yields a fourth-order equation in  $\lambda$ . So the complex vector function  $\lambda(K_{\rm us}, K_{\rm ps})$  is calculated. The stability margin is obtained by solving the equation:  $|\lambda(K_{\rm us}, K_{\rm ps})| = 1$ . Solving this gives the values of  $K_{\rm us}$  and  $K_{\rm ps}$ , which make the system marginally stable.

Fig.2.13. Closed-loop model of double vector controller.

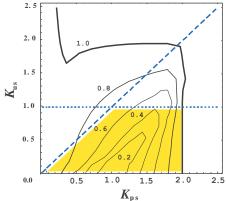

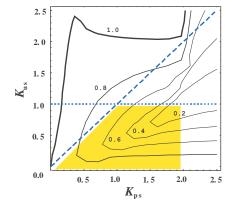

Fig.2.14 shows the absolute-value contours of the eigenvalues 1 and 2, when the stabilization factors vary from 0.0 to 2.5. The plotted contours in Fig.2.14 are 0.2-most thin, 0.4, 0.6,0.8,1.0-most thick. The inclined dashed line represents the inequality  $K_{\rm us} < K_{\rm ps}$  while the horizontal dashed line represents the inequality  $K_{\rm us} < 1$ . The system is marginally stable when  $K_{\rm ps} = 2$ , which means that the inner-loop gain can be increased up to twice the deadbeat gain.  $K_{\rm us}$  can vary from 0.0 to 1.0 and the system is stable provided that inequality  $K_{\rm us} < K_{\rm ps}$  is satisfied. Fig.2.15 shows the absolute-value contours of the eigenvalues 1 and 2, when the stabilization factors vary from 0.0 to 2.5. The plotted contours are 0.2-most thin, 0.4, 0.6,0.8,1.0-most thick. The eigenvalues 3 and 4 are high for low gains and decreases as the gains increase (in the plot range). The conclusion is that the system is stable when  $K_{\rm ps} < 2$ , which means that the inner-loop gain can be increased up to twice the dead-beat gain and  $K_{\rm us}$  can vary from 0 to less than 1.0.

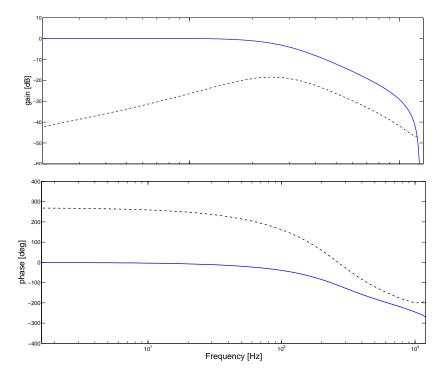

# 2.5.3. Frequency Response of DVC

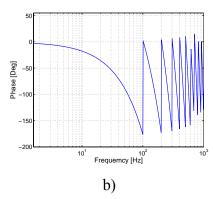

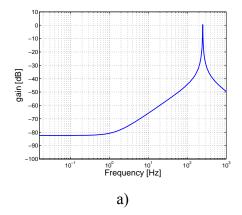

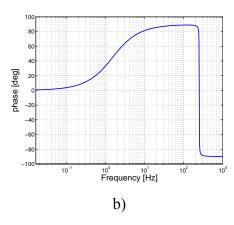

After the derivation of the closed-loop (2.6), the system-frequency response can be investigated. The system parameters are given in Paper C. In Fig.2.16, the frequency response from the reference d-voltage of the capacitor  $u_{\rm cd}^*$  to the d- and q-voltages of the capacitor,  $u_{\rm cd}$  and  $u_{\rm cq}$ , is presented. As seen from Fig.2.16, the cross coupling between  $u_{\rm cd}^*$  and  $u_{\rm cq}$  is very low for low frequencies and increases for high frequencies.

Fig.2.15. Absolute-value contours of eigenvalues 3 and 4, stability margin (most-outer, thick).

Fig.2.16. Frequency response from *d*-voltage reference to *d*- (solid) and *q*- voltage (dashed) of LC-filter capacitor.

The gain from  $u_{cd}^*$  to  $u_{cd}$  is equal to 0 dB, unity in the linear scale, up to 370 Hz, which implies that  $u_{cd}$  tracks  $u_{cd}^*$  accurately up to 370 Hz. For higher frequencies, the gain decreases and the phase shift increases. Thus, the system behaves as a low-pass filter. More details regarding the frequency response are given in [30].

# 2.5.4. Step Response of DVC

The step response of the SSC with the DVC is investigated by applying voltage dips and swells at the grid voltage. Voltage dips and voltage swells imply that the injected voltage by the SSC is stepped up or down to keep the load voltage constant. The results of the step response are analyzed in Chapter 3.

# 2.6. MODIFIED DOUBLE VECTOR CONTROLLER FOR MITIGATION OF UNBALANCED DIPS AND SWELLS

If the three-phase voltage of the grid is balanced, a transformation into the synchronous reference (dq) frame results in dc quantities. Hence, the SSC can use a conventional PI controller to control the injected voltage. However, if the grid or the load voltages are unbalanced, a ripple of twice the grid frequency occurs in the dq-frame. The positive sequence components appear as dc quantities in the dq-frame, which rotates positively with the grid angular frequency  $\omega$ , while the negative sequence components appear as  $2\omega$  rad/s components in the dq-frame. Consequently, the DVC algorithm should be modified to

handle the unbalances in order to obtain a high performance controller. The proposed modifications of the DVC are:

- 1) detection of positive and negative sequence components of the unbalanced quantities;

- 2) use of two controllers: one for the positive sequence and one for the negative sequence component.

The detected positive sequence components are transformed and controlled in the dqp-frame, i.e. a coordinate system that rotates positively with the grid angular frequency  $\omega$ , where they appear as dc quantities. While the detected negative sequence components are transformed and controlled in the dqn-frame, i.e. a coordinate system rotating in the negative (clockwise) direction. In the latter frame, negative sequence components appear as dc components.

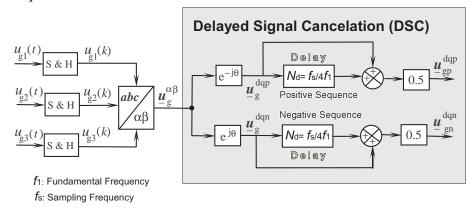

# 2.6.1. Separation of Positive and Negative Sequence Components

In Fig.2.17, the algorithm used to extract the sequence components is shown. This detection algorithm is called the delayed signal cancellation (DSC) algorithm and has been proposed in [33]. The positive sequence of the vector  $\underline{u}_{g}$ ,  $\underline{u}_{gp}$  in the positively rotating dqp-frame is calculated as

$$\underline{u}_{gp}^{dqp}(k) = \left(\underline{u}_{g}^{dqp}(k) + \underline{u}_{g}^{dqp}(k - N_{d})\right)/2$$

(2.7)

where  $N_{\rm d}$  is equal to  $f_{\rm s}/(4f_{\rm l})$  and  $f_{\rm l}$  is the grid frequency of the fundamental component. The negative sequence of the vector  $\underline{u}_{\rm g}$ ,  $\underline{u}_{\rm gn}$  in the negatively rotating dqn-frame is calculated as:

$$\underline{u}_{gn}^{dqn}(k) = \left(\underline{u}_{g}^{dqn}(k) + \underline{u}_{g}^{dqn}(k - N_{d})\right)/2$$

(2.8)

Thus, the positive sequence of the vector  $\underline{u}_g$  is obtained by adding the vector  $\underline{u}_g$  at the sample k to the vector  $\underline{u}_g$  at the sample k- $N_d$ , which is delayed by one fourth of the fundamental period.

Fig.2.17. Delayed signal cancellation method to separate positive and negative sequence components.

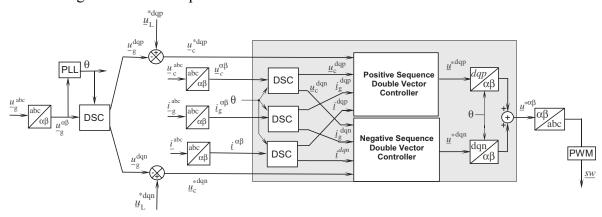

# 2.6.2. Control of Positive and Negative Sequences

The equations of the positive sequence controller of the DVC are given in (2.9), where the subscript p denotes the positive sequence. Because the negative sequence rotates in opposite direction to the positive sequence, the cross-coupling terms between the d- and the q- components have opposite signs in the negative sequence controller. Hence, the equation of the negative sequence controller are given in (2.10), where the subscript n denotes the negative sequence.

Positive Sequence Controller

$$i_{dp}^{*} = i_{gdp} - (\omega C_{F}/2) (u_{cqp}^{*} + u_{cqp}) + K_{u} (u_{cdp}^{*} - u_{cdp})$$

$$i_{qp}^{*} = i_{gqp} + (\omega C_{F}/2) (u_{cdp}^{*} + u_{cdp}) + K_{u} (u_{cqp}^{*} - u_{cqp})$$

$$u_{dp}^{*} = u_{cdp}^{*} + R_{F} i_{dp} - (\omega L_{F}/2) (i_{qp}^{*} + i_{qp}) + K_{p} (i_{dp}^{*} - i_{dp})$$

$$u_{qp}^{*} = u_{cqp}^{*} + R_{F} i_{qp} + (\omega L_{F}/2) (i_{dp}^{*} + i_{dp}) + K_{p} (i_{qp}^{*} - i_{qp})$$

$$(2.9)$$

Negative Sequence Controller

$$i_{dn}^{*} = i_{gdn} + (\omega C_{F}/2) (u_{cqn}^{*} + u_{cqn}) + K_{u} (u_{cdn}^{*} - u_{cdn})$$

$$i_{qn}^{*} = i_{gqn} - (\omega C_{F}/2) (u_{cdn}^{*} + u_{cdn}) + K_{u} (u_{cqn}^{*} - u_{cqn})$$

$$u_{dn}^{*} = u_{cdn}^{*} + R_{F} i_{dn} + (\omega L_{F}/2) (i_{qn}^{*} + i_{qn}) + K_{p} (i_{dn}^{*} - i_{dn})$$

$$u_{dn}^{*} = u_{cdn}^{*} + R_{F} i_{dn} - (\omega L_{F}/2) (i_{dn}^{*} + i_{dn}) + K_{p} (i_{gn}^{*} - i_{gn})$$

$$(2.10)$$

After calculating the reference voltage of the VSC, the dq-negative and the dq-positive sequences are transformed to the  $\alpha\beta$ -frame. Then they are added, transformed into the three-phase frame and compared with the triangular wave to obtain the PWM pattern. A schematic diagram for the modified double vector controller is presented in Fig.2.18.

# 2.6.3. Higher Switching Frequencies

It has been shown in the previous section that adding a negative sequence controller may improve the performance of the SSC in the case of unbalanced dips. However, this has the disadvantage of a more complex controller.

Fig.2.18. Schematic diagram of modified double vector controller.

If the switching and the sampling frequencies increase, only a positive sequence controller is needed. By increasing these frequencies, a faster controller is obtained and the current ripples are reduced. Apparently, the negative sequence components are seen (by the controller) as variations in the positive sequence and with higher switching/sampling frequency, the controller is able to track these variations. But the switching losses increase with the increase of the switching frequency. Therefore, such strategy may be suitable for low-power loads.

#### 2.7. Phase Locked Loop for Static Series Compensator

The accurate phase information is crucial for most of the modern power electronics apparatus such as the SSC. Normally obtaining the phase information has been realized by the Phase-Locked Loop (PLL).

#### 2.7.1. Hardware PLL

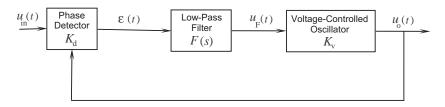

The hardware PLL was first described in 1923 and 1932 [34]. In 1970 it become widespread because of the development of integrated circuits. The classical configuration of the PLL is shown in Fig.2.19. Three main blocks constitute the basic PLL hardware: phase detector, low-pass filter and voltage-controlled oscillator. Normally, the phase detector is of the multiplier type whose output consists of a dc term that has the phase information of the input signal and an ac term that should be filtered by the low-pass filter. The low-pass filter can be realized either by a passive filter or an operational amplifier. The output of low pass filter is a dc signal that corresponds to the phase error between the input and output voltages. This dc signal is the input to the voltage-controlled oscillator.

#### 2.7.2. Software PLL

With the advanced technology of microcontrollers and digital signal processors, all the functions of the classical PLL have been implemented by software. Hence the software PLL (SPLL) has become a competitive alternative to the hardware PLL. The SPLL design offers the most degrees of freedom available in any PLL design [35], because the SPLL can be tailored to perform any function, without modifying the hardware as the case of the classical PLL. Moreover, the classical PLL adds some cost to the total cost of the system. The flexibility added by the SPLL arises from the fact that the design parameters can be easily changed by modifying a few lines in the software code [36]. In single-phase systems, the zero-crossing detection has been used to estimate the phase angle of the grid voltage [37]. Despite the ease to write a zero-crossing detection algorithm, the dynamic performance of the loop is slow and a fast tracking performance is impossible. This is due to that the response can never be faster than ½ cycle of the fundamental voltage. In addition, the accuracy of zero-crossing detection is influenced by disturbances in the input signal such as harmonics. Fast tracking has been obtained by using the delayed grid voltage by one fourth of a period of the fundamental frequency together with the grid voltage itself to construct a stationery reference frame and then a synchronous reference frame [38].

Fig.2.19. Scheme of classical hardware phase locked loop.

In three-phase systems, the SPLL has been proposed for the SSC by transforming the three-phase voltage of the grid into the synchronous reference frame [39, 40] and the performance of the SPLL is controlled by either a lead/lag filter or a PI controller. In [39] and [40], it is stated that the bandwidth of the SPLL should be low for SSC applications but it is not clear how slow the performance should be and how to tune the SPLL. Tuning the SPLL to get a desired transient performance is strongly related to the applications where the SPLL is used. In this thesis, a criterion to tune the SPLL for the SSC is discussed and the gains of the PI controller are determined to obtain the desired performance.

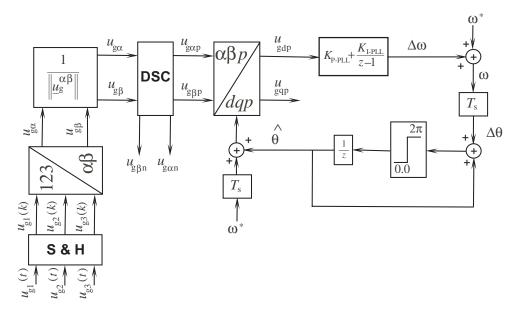

#### 2.7.3. SPLL Operational Principle

A block diagram of the proposed SPLL is depicted in Fig.2.20. The operational principle of the SPLL is explained through the following steps:

- measure and sample the grid voltage  $u_{g1}(t)$ ,  $u_{g2}(t)$ ,  $u_{g3}(t)$  to get  $u_{g1}(k)$ ,  $u_{g2}(k)$ ,  $u_{g3}(k)$ ;

- transform the sampled grid voltage to the  $\alpha\beta$ -frame, obtaining  $u_{g\alpha}(k)$  and  $u_{g\beta}(k)$ ;

- normalize to the magnitude of the  $\alpha\beta$ -vector of the grid voltage,  $\left\|\underline{u}_g^{\alpha\beta}\right\| = \sqrt{u_{g\alpha}^2 + u_{g\beta}^2}$ ;

- separate the positive and the negative sequence by using the delayed signal cancellation technique (DSC) to obtain the positive sequence of the grid voltage in the positive  $\alpha\beta$ -frame,  $\alpha\beta p$ -frame. The DSC was briefly explained in Section 2.6;

- transform from  $\alpha\beta p$ -frame to positive dq-frame, dqp-frame to get the positive sequence components of the grid voltage,  $u_{\rm gdp}$  and  $u_{\rm gqp}$ ;

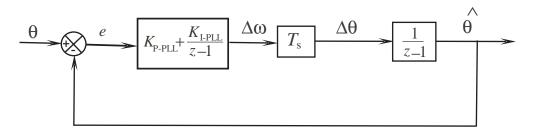

- the d-component  $u_{\rm gdp}$  is the input to the PI controller of the SPLL to calculate the change in the angular frequency of the grid voltage,  $\Delta\omega$ ;

$$\Delta \omega = (K_{\text{P-PLL}} + K_{\text{I-PLL}}/(z-1))u_{\text{gdp}}$$

(2.11)

where  $K_{\text{P-PLL}}$  and  $K_{\text{I-PLL}}$  are the proportional and the integral gains of the PI controller. Here it is worth to state that an integration part is necessary especially in the case of low-inertia grids where the grid frequency can deviate around the nominal frequency.

• add the reference angular frequency,  $\omega^* = 2\pi f^*$ , where  $f^*$  is the reference frequency of the grid, 50 or 60 Hz.

$$\omega = \Delta \omega + \omega^* \tag{2.12}$$

• multiply  $\omega$  by the sampling time  $T_s$  to obtain the increment of the phase angle  $\Delta\theta(k)$ ;

$$\Delta \theta = T_s \omega \tag{2.13}$$

Fig.2.20. Block diagram of proposed software phase locked loop.

• by integrating the increment  $\Delta\theta$ , the estimated phase angle of the grid voltage  $\hat{\theta}$  is obtained;

$$\hat{\theta} = z\Delta\theta/(z-1) \tag{2.14}$$

• the estimated angle  $\hat{\theta}$  is used to calculate the new *d*-component  $u_{\rm gdp}$  until  $u_{\rm gdp}$  becomes zero and  $u_{\rm gqp}$  becomes constant and the difference between the actual phase angle of the grid voltage and the estimated angle becomes zero.

# 2.7.4. SPLL Modeling

A model of the SPLL is obtained to be able to tune it. The grid voltage, after sampling is assumed as:

$$u_{1} = \sqrt{2}U\cos(\theta)$$

$$u_{2} = \sqrt{2}U\cos(\theta - \frac{2\pi}{3})$$

$$u_{3} = \sqrt{2}U\cos(\theta + \frac{2\pi}{3})$$

(2.15)

where U is the RMS of the grid voltage (phase to ground). The  $\alpha\beta$ -components of the grid voltage are calculated as

$$\begin{pmatrix} u_{g\alpha} \\ u_{g\beta} \end{pmatrix} = \frac{2}{3} \begin{pmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{pmatrix} \begin{pmatrix} u_{g1} \\ u_{g2} \\ u_{g3} \end{pmatrix}$$

(2.16)

After normalization to  $\|\underline{u_g^{\alpha\beta}}\|$  and algebraic manipulation of (2.16), the  $\alpha\beta$ - components of the grid voltage become:

$$\begin{pmatrix} u_{g\alpha} \\ u_{g\beta} \end{pmatrix} = \begin{pmatrix} \cos(\theta) \\ \sin(\theta) \end{pmatrix}$$

(2.17)

Then the positive sequence is extracted to obtain  $u_{g\alpha p}$  and  $u_{g\beta p}$ . The dqp- components of the grid voltage are calculated as:

$$\begin{pmatrix} u_{\text{gdp}} \\ u_{\text{gqp}} \end{pmatrix} = \begin{pmatrix} \cos(\hat{\theta}) & \sin(\hat{\theta}) \\ -\sin(\hat{\theta}) & \cos(\hat{\theta}) \end{pmatrix} \begin{pmatrix} u_{\text{gop}} \\ u_{\text{gfp}} \end{pmatrix}$$

(2.18)

where  $\hat{\theta}$  is the estimated angle by the SPLL. It is worth to mention that as the synchronization is made with respect to a virtual flux vector,  $-\pi/2$  is added to the estimated angle. After algebraic manipulation, the dqp- components of the grid voltage are obtained:

$$\begin{pmatrix} u_{\text{gdp}} \\ u_{\text{gqp}} \end{pmatrix} = \begin{pmatrix} -\sin(\theta - \hat{\theta}) \\ \cos(\theta - \hat{\theta}) \end{pmatrix}$$

(2.19)

When the difference  $\theta - \hat{\theta}$  approaches zero the dqp-components become

$$u_{\text{gdp}} \cong 0, \qquad u_{\text{gqp}} \cong 1$$

(2.20)

Equation (2.19) represents a nonlinear relation where the d-component of the grid voltage  $u_{\rm gdp}$  is a function of the sine of the difference between the actual and the estimated angles. To simplify the analysis, a linearized model is obtained.

#### 2.7.5. SPLL Linearized Model

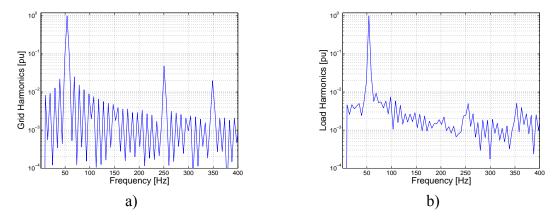

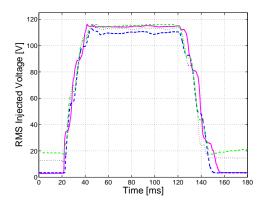

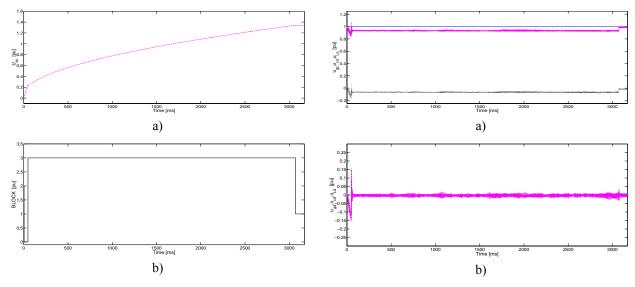

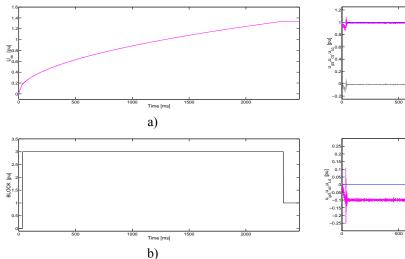

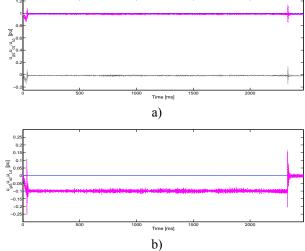

A linearized model of the SPLL can be obtained if the difference between the actual and the estimated phase angles is considered small. This assumption implies that