# Tool-Supported Timing Analysis of Automotive Embedded Systems

Master of Science Thesis in Intelligent System Design

MADHUMITA BEHERA

Department of Applied Information Technology CHALMERS UNIVERSITY OF TECHNOLOGY Gothenburg, Sweden, 2009 Report No. 2009:065

### REPORT NO. 2009:065

# Tool-Supported Timing Analysis of Automotive Embedded Systems

MADHUMITA BEHERA

Department of Applied Information Technology Chalmers University of Technology SE-41296, Gothenburg, Sweden 2009

# **Tool-Supported Timing Analysis of Automotive Embedded Systems**

MADHUMITA BEHERA

© MADHUMITA BEHERA, 2009 Report no: 2009:065 ISSN: 1651-4769

Address:

Department of Applied Information Technology Chalmers University of Technology SE-41296 Gothenburg, Sweden

Telephone:

Head of Dept: +46 (0)31-786 2763, Information officer: +46 (0)31-786 5548, Student counsellor: +46 (0)31-772 4893

Chalmers Reproservice Göteborg, Sweden 2009

#### **SUMMARY:**

TIMMO Project aimed to develop a Domain specific Modeling language for handling timing information while developing automotive distributed embedded systems. Hence timing analysis becomes an obvious step in the validation phase of TIMMO results i.e. TADL, the modelling language and TIMMO methodology, guidelines for using this language. To facilitate timing analysis process, a tool survey was conducted followed by tool inventory in order to have a selection of most suitable tools that are currently available for timing analysis. A validator system, basically an automotive embedded system was developed to validate the TIMMO results at Volvo Technology. This validator system was modeled with the timing properties using one of these selected tools. The timing models thus created defined the validator system with timing information associated with it and were analysed to study the behaviour of its timing properties.

A set of structured steps were defined in the form of heuristics to be followed while modeling such automotive embedded systems along with their timing information. These steps were applied to two different abstraction levels of timing model of the validator system.

A timing information flow analysis was also conducted for the different tools involved in defining the validator system in order to find out the possibility of transferring the timing information from one tool to another. By developing a parser in java, it was studied that the timing information defined for modeling an automotive system in one tool can be extracted and can be restructured to model it in another tool.

# **Keywords:**

Automotive, Embedded, Timing Analysis, TIMMO, TADL, Methodology, Validator, Heuristics, Parser

# **Acknowledgement:**

Foremost, I would like to express my sincere gratitude to my supervisors Andréas Johansson and Claes Strannegård for their motivation, enthusiasm, and guidance through out the process of my thesis work. Their support and encouragement has immensely helped me towards the completion of this thesis.

I am grateful to whole TIMMO project team at Volvo Technology whose suggestions and advice has improved my work to a great deal. Finally I would like to thank Mechatronics and Software Department at Volvo Technology for providing me the necessary facilities and technical support during this project.

Madhumita Behera, 2009

# **Contents:**

| 1. | Introdu          | iction                                                 | 7          |

|----|------------------|--------------------------------------------------------|------------|

|    | 1.1.             | Automotive Embedded System                             | 7          |

|    | 1.2.             | Timing Problems Associated with Automotive Systems     |            |

|    | 1.3.             | What is a Modeling Language?                           |            |

|    | 1.4.             | TIMMO Project                                          |            |

|    | 1.5.             | Contributions                                          |            |

|    | 1.6.             | Thesis Structure                                       |            |

| 2. |                  | ound                                                   |            |

|    | 2.1.             | Modeling Automotive Embedded System                    |            |

|    | 2.1.1.           | UML                                                    |            |

|    | 2.1.1.           | AUTOSAR                                                |            |

|    | 2.1.2.           | EAST-ADL2/ATESST (ETAS)                                |            |

|    | 2.1.3.<br>2.1.4. | SysML                                                  |            |

|    |                  | MARTE                                                  |            |

|    | 2.1.5.           |                                                        |            |

|    | 2.1.6.           | MATLAB/Simulink                                        |            |

|    | 2.1.7.           | AADL (Architecture Analysis & Design Language)         |            |

|    | 2.1.8.           | Timing Definition Language                             |            |

|    | 2.1.9.           | Timed Petri Nets                                       |            |

|    | 2.1.10.          | SystemVerilog                                          |            |

|    | 2.2.             | Results from TIMMO Project                             |            |

|    | 2.2.1.           | TADL                                                   |            |

|    | 2.2.2.           | TIMMO Methodology                                      |            |

|    | 2.3.             | Validation of TIMMO Results                            |            |

|    | 2.3.1.           | Validation Process in TIMMO                            |            |

|    | 2.3.2.           | Techniques Used for Timing Analysis                    |            |

| 3. |                  | urvey and Inventory                                    | 23         |

|    | 3.1.             | Tool Survey for Timing Analysis In TIMMO               |            |

|    | 3.1.1.           | List of Surveyed Timing Analysis Tools                 |            |

|    | 3.1.2.           | Required Tool Properties for Timing Analysis           |            |

|    | 3.1.3.           | Tool Evaluation with TIMMO Requirements                |            |

|    | 3.1.4.           | Tool Selection                                         | 31         |

|    | 3.2.             | Tool Inventory                                         | 31         |

|    | 3.2.1.           | Tool Inventory of Task                                 | 32         |

| 4. | Informa          | ation Flow Analysis                                    | 37         |

|    | 4.1.             | Tools Used in TIMMO                                    | 37         |

|    | 4.1.1.           | Volcano VSA:                                           | 37         |

|    | 4.1.2.           | Vector Tools                                           | 38         |

|    | 4.1.3.           | Simulink                                               |            |

|    | 4.1.4.           | SymTA/S                                                | 40         |

|    | 4.2.             | Information Flow among Tools                           | 40         |

|    | 4.2.1.           | A Parser Development for Information Flow Analysis     | 41         |

|    | 4.2.2.           | Information flow analysis from VSA to SymTA/S          |            |

|    | 4.2.3.           | Information flow analysis from Vector Tools to SymTA/S | 43         |

| 5. | _                | Modeling And Analysis                                  | 45         |

| _  | 5.1.             | Timing Models using Timing Analysis Tool               |            |

|    | 5.1.1.           | Timing Models                                          |            |

|    | 5.1.2.           | Schedulability Analysis                                |            |

|    | 5.2.             | Example System                                         |            |

|    | 5.2.<br>5.3.     | Results                                                |            |

|    | 5.3.1.           | Resulted Timing Models                                 |            |

|    | 5.3.1.<br>5.3.2. | Results from Timing Analysis                           |            |

|    | 5.3.∠.<br>5.4.   | Comparative study                                      |            |

| 6. |                  |                                                        |            |

| n  | neuris           | tics For Timing Modeling                               | <b>5</b> 5 |

|     | 6.1.1.          | Heuristics for Design Level Modeling         | 55   |

|-----|-----------------|----------------------------------------------|------|

|     | 6.1.2.          | Heuristics for Implementation Level Modeling | 59   |

|     | 613             | Results from Using Heuristics                | 62   |

| 7.  | <b>Analysis</b> | Of Results                                   | . 63 |

| 8.  | Conclusion      | on                                           | . 64 |

| 9.  | <b>Future W</b> | ork                                          | . 65 |

| 10. | Reference       | es                                           | . 66 |

| 11. | Glossary        |                                              | . 69 |

# 1. INTRODUCTION

Behaviour of today's automotive products is greatly controlled by the embedded electronic systems present in it. These embedded systems are task specific computing or controlling units. These systems are growing in number and complexity with addition of new functionality and features to modern automobiles. Designing and developing such automotive embedded systems requires a structured approach and well defined set of guidelines facilitating this process. Model based approaches have been widely used in automotive industries for managing modeling complexities. Modeling languages are the key to implement such modeling concepts by supporting the process with increased performance and quality. However timing issues has always been a big concern while modeling. Timing is important in almost all real-time embedded systems especially in automotive embedded systems where results of neglecting timing could range from loss of comfort to life threatening situations. Therefore handling timing issues is the most desired feature in a modeling language. Some of the modeling languages that have been successful in modeling engineering systems still face the challenge of handling timing requirements. Hence with existing complexity and need of adding new innovative features in modern automobiles a modeling language should facilitate detecting and handling timing problems early in the process.

# 1.1. Automotive Embedded System

An embedded system is a computing system which is completely dedicated to perform one or a few more tasks or operations. Such a system is always found embedded inside a complete system. The use of embedded system is growing day by day in many diverse fields. Major application areas are aerospace, automotive, military and medical devices, home appliances etc. The number of fields in which such systems can be used is still growing with new trials and experiments for their use. In future, such systems are expected to be part a major computing and controlling systems because of their flexibility of designing with desired size, cost, safety, reliability features and performance measures. Examples of such system can range from a simple MP3 player to a larger system like nuclear power plant controlling system.

Embedded systems are mostly associated with timing constraints. A very simple example of such timing constraints faced by an embedded system is a dead-line i.e. a desired time span in which the necessary task of the system has to be completed. Section 1.2 in this chapter brings out some of the timing problems that are faced by these systems. Many such timing problems can arise while carrying out the task or even getting associated with other tasks. Due to the close association with time, these systems are known as real-time embedded systems. For a real-time embedded system not only the correctness of system performance matters but also the timely completion of the task matters. These real-time systems can be categorized mainly into two major categories on the basis of importance of timely completion of the task. These categories are Hard real-time systems and Soft real-time systems. For a Hard real-time system time is the most important factor as the results of missing the dead line could be losing money or even life. Whereas in case of Soft real-time systems missing the dead line of the task may not be hard compared to Hard Real time System. A Flight control system is an example of Hard real-time System, as a single flight error might cause loss of life on the other hand an Airline Reservation System can be cited as an example of a Soft real-time System, since to miss an airline booking is rarely catastrophic.

Embedded Systems have found a great importance in automotive applications as well. A modern automobile has a number of small and large embedded systems distributed inside it. Anti-lock breaking system (ABS), Navigation System, Emission Control, Climate Control System, Door Control systems are some of the examples of such automotive embedded systems. Most of the automotive embedded systems are hard real- time embedded systems.

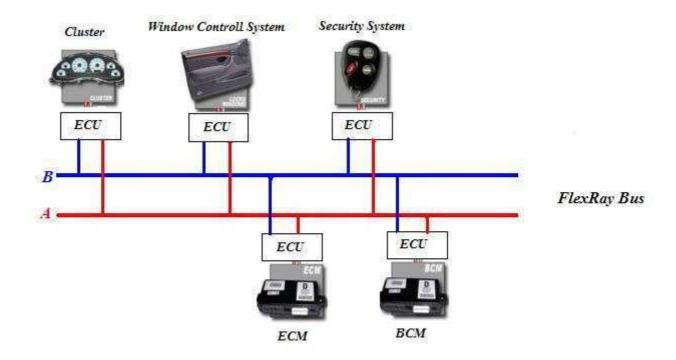

Figure 1: automotive embedded systems attached to a FlexRay Bus

A close look at these systems will reveal that each of these systems is a combination of sensors, actuators and Electronic Control Unit (ECU). Sensors collect the required electric or mechanical signals and sent to the respective ECUs. ECU processes these signals and sent necessary signals to actuator for required actions. The ECU to ECU communication is supported by communication networks like CAN, LIN, FlexRay or MOST etc.

The automotive embedded systems are truly distributed and diverse in terms of their functionality, development and construction. Some of these systems work independently or depend largely on other small or large systems. Each of these systems is dedicated to different functionalities. For example a door control system is for controlling door functioning, an Engine Control Module (ECM) is for controlling the internal combustion engine and so on. These systems are distributedly present inside an automobile. The reason behind such a distribution is mainly to get localized to reason of impact. This can be better explained with the example of a door control system where the embedded system to control the door movement should be located very much close to the door. Similarly the systems are also needed to be very much near the functioning areas as well. The development process of these systems also brings the fact that these systems get distributed during the development as it can take place at different location by different development teams. These systems are also very diverse in terms of the components used for developing them.

Figure 1 is an example of the presence of such systems inside an automobile. The complete system may look like a combination of a number ECUs connected with different communication network CAN, LIN, FlexRay or MOST. Every country has its own laws and regulations to define their vehicles. The manufactures thus have to consider laws and regulation while manufacturing these automotive systems. For example if a country has a policy of the emission of vehicles then the automobile manufactures should design the emission control system of the automobiles to meet the desired emission limit. These automotive systems are thus known as distributed embedded real-time systems.

Timing becomes the most important factor while considering these distributed automotive embedded real-time systems. Handling real-time constraints to add more functionality to a vehicle and to avoid the complexity of distribution is required while modelling these systems. Though many modelling approaches are currently into practice, handling timing constraints is still an area to be improved with. Section 2.1 in chapter 2 brings out some of these modelling approaches currently followed in automotive industry and also how they have proceeded with the timing problems.

# 1.2. Timing Problems Associated with Automotive Systems

Some of the main timing constraints faced by an embedded real-time systems are deadline, Worst Case Execution Time, Periodicity, Precedence Constraints, Exclusion Constraint, time offset, jitter and many more. In this section we shall discuss some of these problems

- Deadline: This is the desired time limit for a task execution. In hard real-time system, a task is not at all allowed to exceed a defined time limit or its deadline where as in soft real-time system exceeding execution time limit is not as critical as in a hard real-time system.

- Worst Case Execution Time (WCET): It is the maximum execution time of a task. WCET is one of the timing properties that should be studied in order to have a feasibility study of a system.

- Periodicity: The frequency of task execution within a time span is known as periodicity. Knowledge of periodicity of tasks along with individual execution time helps to find out the total time execution time of a system.

- Precedence Constraints [27]: A task may need to run after another task in order to get the resulted value from it, which is known as a precedence constraint. Precedence constraints are very useful for many types of real-time system: typically we want to implement a `pipeline', where input data is read in to one task, which passes computed results down a pipeline of other tasks and the last task in the chain sending the results to output ports [43].

- Exclusion Constraint: In some cases a task may need to share data or a resource with another task or a number of tasks. So a task has to execute by giving exclusion to other tasks to use the shared resources to another task. This required the control flow to get switched between different tasks. For example let two tasks A and B have access to some shared data structure (such as a linked list). The algorithm that builds the scheduling table must make sure that we never switch to B unless A has completed all its execution, and vice versa these restrictions on how task switch should occur is often called exclusion constraints [43].

Any embedded system or an automotive embedded system to be specific, should satisfy these timing constraints in order to create a reliable system in terms of safety and performance.

# 1.3. What is a Modeling Language?

A modeling language is used to express information or knowledge related to a system in a structured way and is defined with a set of rules. It can be graphical or textual. A graphical modeling language uses diagrams and symbols to represent concepts and lines to represent relations whereas a textual modeling language uses standardized keywords and parameters to interpret expressions.

In computer science many modeling languages have emerged. UML (Unified Modeling Language) [18] could be considered as an example of such languages which has been used for modeling in many diverse fields of expertise and hence is considered as a general purpose modeling language. A generalized modeling language fails to describe a system with its technicalities. To Model an engineering system, a modeling language should be capable of representing various facets of an engineering system. Hence there have been many attempts to develop a modeling language that can be more specific to the desired domain. This resulted into development of some modeling approaches and languages that aimed to completely get adapted to engineering domain requirements.

A considerable amount of effort has been put to develop automotive domain specific modeling approaches as well. The existing approaches and current achievements for development of automotive embedded system are UML, AUTOSAR (AUTomotive Open System ARchitecture) [3], AADL [1] and EAST-ADL[12] where as languages for real-time and hardware system are Timed Petri-Nets, Timed Automata, TDL[38], SystemC, SystemVerilog [26], PSL and CTL etc. Such languages tend to support specification, analysis, design, verification and validation of a broad range of systems and systems-of-systems. Along with modeling languages one more modeling approach that is getting very prominent is Meta-Model. For

modeling a predefined class of problems, Meta-models have been used in analysis, construction and development of the frames, rules, constraints, models and theories. One of the most active branches of model driven engineering is model-driven architecture proposed by OMG [37] (Object Management Group), which is based on the utilization of a modeling language to write metamodels. This is known as MOF (Meta Object Facility) [25]. Metamodels proposed by OMG are UML, SysML (Systems Modeling Language) [24], SPEM (Software Process Engineering Metamodel) [33] or CWM (Common Warehouse Metamodel) [11].

A special category that has been emerged is Domain-Specific Language which is very specific to the problems in particular to a domain and does not consider any problem outside it. Domain-specific modeling (DSM) language is engineering system specific language. It can be a considered as a methodology for designing and developing engineering systems. It involves systematic use of a graphical DSL to represent the various facets of a system and supports higher-level abstractions. Hence less effort and fewer low-level details are required to specify a given system. Some these domain specific languages are explained in Section 2.1.

# 1.4. TIMMO Project

TIMMO (Timing Model) [39] is an ITEA2 Project that started with the joint effort of sixteen partners from Austria, Germany, France, The Netherland and Sweden in April 2007. TIMMO targets a breakthrough by using a standardized approach for handling such timing related problems. TIMMO aims to develop a modeling language, Timing-Augmented Description Language (TADL) and Methodology for describing the steps to use this language for handling timing problems that may arise in all phases of development of modern automotive systems. Timing-Augmented Description Language as a domain specific modeling language aims to enhance the design models created with any appropriate modeling language by extracting the timing behaviour of the parts of the systems explained by these models.

This thesis project was carried out within the scope of TIMMO aiming at evaluating the suitability of state-of-the-art of the timing analysis tools for automotive embedded systems.

The goals of this project is

- To have an early analysis of a system in order to meet the desired timing requirements.

- To trace the timing constraints at all abstraction levels.

- To get improved and predictable development cycle.

This project desires for three concrete development results:

- *Modeling language:* For Timing that enables to model timing aspects where the definition of the language is formalized as a meta-model.

- *Methodology:* To describe the steps to be followed in different development stages and on the different levels of abstraction with respect to specification, analysis and verification of timing aspect.

- Validation: to verify the applicability of methodology and language by prototype development.

### 1.5. Contributions

This thesis work contributed mainly to the validation of the TIMMO results. The contributions of this thesis work can be summarized as follows

• A tool survey, as described in Chapter 3 gives a list of academic and commercial tools that can be employed for timing analysis of embedded systems. This list can be useful for any automotive projects that seek information on available tools for timing analysis. The timing behaviour, timing modeling and system feasibility studies are possible using such tools.

- Tool inventory, in Chapter 3 gives a list of suitable tools for timing analysis as per TIMMO validator requirements. The methods and analysis processes involved during the selection process, gives an example on how such a selection can be made.

- Timing models developed in timing analysis tools shows how timing analysis can be made at various abstraction levels of an automotive system and how it relates to a generalized development Methodology i.e. TIMMO Methodology. It also helps to analyze the feasibility of a system.

- This thesis presents a heuristics, described in chapter 6 for analysing the timing properties at an early stage while demonstrating it with a real world example i.e. TIMMO Validator developed at Volvo Technology. It shows the feasibility and usefulness of common exchange format across different tools while preventing the re-engineering of models for different purposes. As Heuristics have been applied to two different abstraction level, it helps to give a comparative study of system model. The heuristics from timing model though developed in context of TIMMO validator, can also be applied to other automotive systems.

- An Investigation on the exchange of timing-related information across all tools, used in TIMMO validation process was carried out. A proposed workflow & exchange format to minimize redundant work & speed up interaction was developed. A parser developed for this purpose suggests that exchange of timing information from one tool to another is possible and necessary efforts can be employed to develop a tool to fasten the process of extracting timing information in one tool and then redefining it in another tool. This also application to automotive embedded systems.

#### 1.6. Thesis Structure

This Thesis Report elaborates the validation process of TIMMO methodology and TADL by timing analysis of prototype systems using timing analysis tools. The structure of thesis in short is as followed

- Chapter 2: In this chapter TIMMO results are explained with examples along with validation requirement and validation process:. These results mainly include the TADL, the modeling language and Methodology, steps to use this languages. The employed techniques for timing analysis of TIMMO validators are also described.

- Chapter 3: This chapter mainly contains tool survey for timing analysis. Hence, it contains a list of tools surveyed for timing analysis of automotive embedded systems with their features and limitations. An analysis of the TIMMO validation requirement is made and the surveyed tools are analysed taking the requirements into account. A selection of the tools is made in order to have a selection of most appropriate tools for the timing analysis. As few prototype systems were developed to verify the TIMMO results and the timing analysis of these systems were needed, an analysis of the system requirement was made prior to the timing analysis of these systems. This chapter describes these requirements.

- Chapter 4: An exchange of timing related information among these tools was studied. A sample implementation was made in order to minimize the work and speed up the interaction between tools. Chapter 4 describes this analysis.

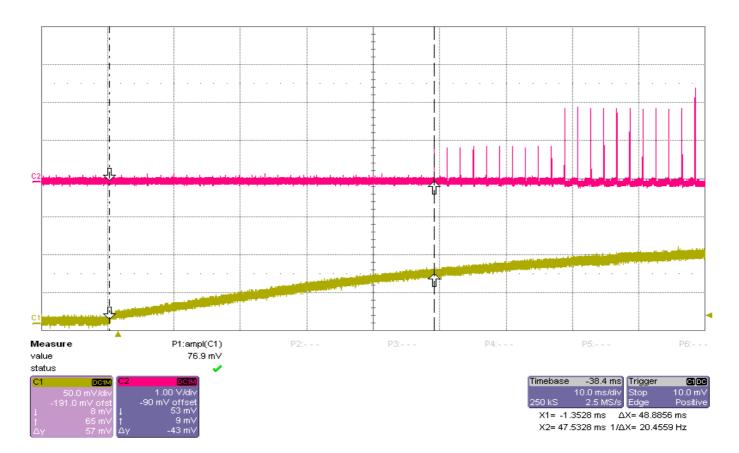

- Chapter 5: Using some of the tools selected from the tool inventory, timing models were developed for validation and verification of the validator systems. Chapter 5 describes these timing models and gives a comparative study of the results obtained from these models and from the real system.

- Chapter 6: This chapter describes the heuristic develop for creating timing models for two different abstraction levels. These heuristics are list of steps to be followed while developing a timing model of embedded system.

- Chapter 7: It is the summary chapter that summarizes all the work carried out in this thesis project.

- Chapter 8: This chapter gives the conclusions drawn from this thesis work

- Chapter 9: This chapter mainly describes future works that can be planned for improving the results.

# 2. BACKGROUND

A number of modeling approaches are currently used for automotive embedded systems. Some of these modeling approaches are general purpose and some of them are very specific to the domain. However handling timing problems has not been a well developed feature in many of these modeling approaches. Considering the timing importance in automotive systems, it is always been a desired feature.

# 2.1. Modeling Automotive Embedded System

This section lists out some of the currently used modeling approaches in automotive industry and describes how these approaches have handled the issues faced while handling timing problems. The list is an overview of the modelling approaches described in [41].

#### 2.1.1. UML

UML has long been used as a modeling language in automotive industries. It includes technique for using graphical notation to create abstract models. UML employed methods specify, visualize and document the facts related to an object-oriented system development. UML can be used throughout the software development life cycle while implementing different technologies. Graphical notations are used by UML to describe a specific system model. Graphical representation includes two main categories 1) Structural Diagram 2) Behavioural diagram. The structural diagram mostly includes class, component, component structure object, package and deployment diagrams, the behavioural diagram include active, behaviour and usecase diagrams.

Though UML can efficiently describe the structure, behaviour and interaction of a system, it has the draw back of not being very specific to domain and thus fails to define every aspects of system domain. Timing behaviour analysis is something that has never been a concerning matter in UML. To overcome the draw backs of such a generalized modeling language many improved version of UML like SysML has been developed to make it more domain specific.

#### **2.1.2. AUTOSAR**

AUTOSAR is a partnership of automotive OEMs, suppliers and tool vendors for creating and establishing an open standard for automotive system architectures. AUTOSAR aims at providing a basic infrastructure that meets all requirements of automotive application domains. AUTOSAR use a component based software design model for a vehicular system design. It provides a layered architecture that separates the system functionalities from hardware and software components. The basic abstraction layers in AUTOSAR are Basic Software (BSW) Layer, Real Time Environment (RTE) and Application Layer. Basic Software Layer provides the hardware dependent and independent services to the upper layer i.e. the RTE. The RTE acts as a bridge between the software components of the application layer to the respective hardware component of the BSW layer.

However Timing still needs to draw attention in AUTOSAR. Some of the attempts made in order to bring timing feature for software components and connectors were not successful. Approaches on abstract levels also failed [4].

#### 2.1.3. EAST-ADL2/ATESST (ETAS)

EAST-ADL [12] is an architecture description language, developed by ITEA cooperative project for automotive embedded systems. It defines an information model in order to capture all relevant

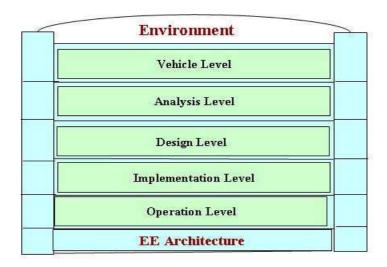

engineering information in a standardized way. The language is structured in five abstraction levels as show in Figure 2 below. These abstraction levels reflect different stages of an engineering process.

Figure 2: EAST-ADL Abstraction levels [12]

- Vehicle layer: It describes the features of vehicle.

- Analysis Level: It describes the functional definition of a vehicle.

- Design level: It is mainly concerned with describing the functional features of the vehicle along with the hardware with more details.

- Implementation levels: The hardware and Software components are described in this Implementation level.

- Operational Level: The embedded components are described with all specification in the operational Level.

EAST-ADL2 language supports the modeling requirements by tracing all modeling entities. EAST\_ADL has relevance to AUTOSAR mainly in the implementation level. Timing relevant information is seen as an issue of non-functional requirements and a specialization of quality requirements.

#### 2.1.4. SysML

SysML is an open source project, founded by the SysML Partners. SysML is a Domain-Specific Modeling language that can support analysis, design, verification and validation of engineering systems [35]. It is defined as a dialect or profile of UML 2.0 and thus can provide mechanisms to collaborate software intensive systems models. It fulfils additional requirements of UML 2.0 with its extended features for reducing the software centric restrictions in UML, supporting tabular notation and features for requirement managements etc.

Being a improved modeling language and a system specific, it also does not include any timing features like UML 2.0.

#### 2.1.5. MARTE

UML continued to be a general purpose modelling language for a long time. It was most obvious to extend UML to the field of real-time embedded systems by providing more precise expression of domain specific phenomena (e.g., mutual exclusion, concurrency, deadlines etc.). OMG, one of the principal international organizations promoting standards supporting the usage of model-based software and systems development a UML profile named as Schedulability, Performance and Time (SPT). Although SPT could provide concepts for model based schedulability analysis and performance analysis, it could not over come the shortcomings of flexibility and expressiveness. Hence a new UML called MARTE (Modeling and Analysis of Real-Time and Embedded systems) [6] was developed to over come the shortcomings of SPT.

MARTE provides different computational paradigms such as asynchronous, synchronous, and time. Analysis part in MARTE provides facilities to annotate models with information for model specific analysis, like performance and schedulability analysis.

#### 2.1.6. MATLAB/Simulink

Simulink [32] is an environment for Model-Based Design which can be used for dynamic and embedded systems with multi-domain simulation and interactive graphical environment. It provides features for designing, simulating, implementing and testing range systems. Its tight integration with MATLAB environment helps to analyze and visualize results and to test data.

Simulink has been considered mainly as a modeling and simulating environment of automotive embedded systems so far.

### 2.1.7. AADL (Architecture Analysis & Design Language)

AADL [1] is an architecture modeling notation specifically designed to support modeling of embedded systems. Its goal is to provide a standard and ways for modeling embedded real-time system architecture with support for analysis and validation of its functional and non-functional properties. It focuses on avionics and automotive domain, where embedded should be able to tolerate faults and guarantee high levels of assurance.

AADL does not contain any mechanisms for specification of timing issues like intervals or dates.

#### 2.1.8. Timing Definition Language

TDL [38] is a programming model for hard real-time systems, thus considered as a Domain Specific lanagauge. Timing properties of a hard real-time system can be described with its language constructs in a descriptive way. It separates the timing aspect of such applications from the functionality which must be described using an imperative programming language such as Java, C or C++. TDL is concepts are based on Giotto, a time triggered modelling language. The textual notation feature of TADL helps to define the timing behaviours.

#### 2.1.9. Timed Petri Nets

Petri Net is a mathematical modeling language to describe discrete distributed systems. When Petri net get associated with time it is known as Timed Petri Net [9]. The modeling protocol is by using Petri-Nets. For analysing timing timed automata is used. However not very clear on how it will contribute to timing analysis of automotive systems.

### 2.1.10. SystemVerilog

SystemVerilog [26] is a combined Hardware Description Language (HDL) and Hardware Verification Language based on extensions to Verilog. Most of the verification functionality is based on the OpenVera language from Synopsys SystemVerilog is based on a behavioural semantics for discrete event simulation comparable to VHDL, SystemC, and SpecC.

Currently timing problems are mostly dealt with late in the development process which is addressed by means of measuring and testing.

# 2.2. Results from TIMMO Project

TIMMO develops a Timing Augmented Descriptive Language (TADL), a modelling language and methodology for using this language in order to handle timing problems that may arise in all phases of development of modern automotive.

A brief description about these results is given in the following section.

#### 2.2.1. TADL

Following section explains TADL concepts and elements with example. The related work to TADL explained here might have changed. Updated information on TADL and Methodology can be found in TIMMO homepage [39].

### 2.2.1.1. Concepts involved in TADL

The modeling concept of TADL is based on EAST\_ADL2 and AUTOSAR while extending the structural concepts with time related information. TADL follows the five abstraction levels as described in section 2.1.3 for EAST\_ADL. The structural modelling in TADL is performed as defined in EAST-ADL2 mainly on higher abstraction level whereas AUTOSAR modeling is performed on implementation level. The augmentation is done by adding information related to timing and events referring to structural elements [42].

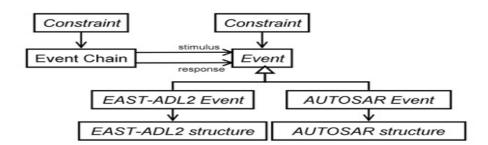

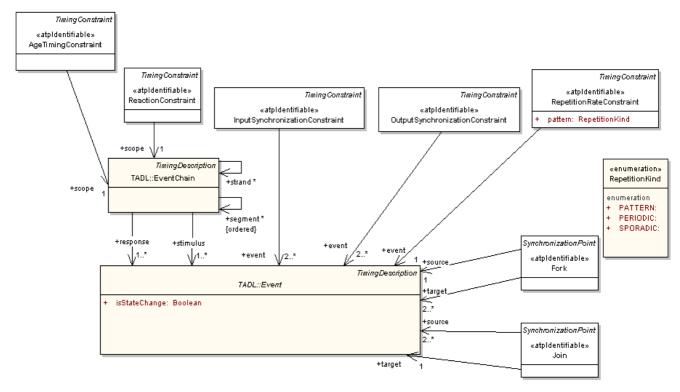

Figure 3: Simplified UML meta-model showing the relationship between events, event chain, constraints and structural elements in TADL.

The TADL constraints are defined being separated from the structural modeling and referring to structural elements via event chains and events, as shown in Figure 3 above. The events are tailored to refer to specific elements in the structural model, i.e. different sets of events are available for the EAST-ADL model and the AUTOSAR model [42].

#### 2.2.1.2. TADL Elements

#### Event:

Any function occurrence that either stimulates an execution, or is caused by an execution is known as an Event. An event is either a Stimulus or a Response (R). An event either indicates that a state change or a current state.

#### Event Chain:

An Event Chains describes the temporal behaviour of a number of steps taken to respond to one or more events. Such events are categorized into stimuli and responses. Time chains can refer to other time chains which are then called time chain segments.

#### Mode:

Modes determine the state of the system, a hardware entity, or an application. The use of modes can be used to filter different views of the model.

#### ModeGroup:

The set of Modes in a ModeGroup are mutually exclusive. This means that only one Mode of a ModeGroup is active at any point in time.

#### Timing:

Timing is the collection of timing constraints and their descriptions in the form of events and event chains.

#### TimingDescription:

It describes the timing events and their relations within the model.

#### TimingConstraint:

TimingConstraint denotes a requirement entity that allows giving bounds on system timing attributes, i.e., end-to-end delays, periods, etc. Different types of timing constraints described in TADL are 1) AgeTimingConstraint 2) ArbitraryRepetitionConstraint 3) Fork 4) InputSynchronizationConstraint 5) Join 6) OutputSynchronizationConstraint 7) ReactionConstraint 8) RepetitionKind 9) RepetitionRateConstraint 10) SynchronizationPoint [41]. The following Figure 4 shows these timing constraints relating to an event

Figure 4: Timing Constraints from TADL [41]

# 2.2.1.3. An Example on TADL

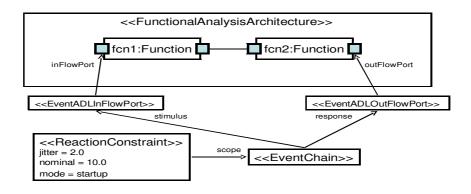

All TADL constraints carry a timing bound and a mode. Figure 5 shows an example with some of the timing constructs.

Figure 5: Conceptual diagram of the design modeled in TADL.

Function 1 and Function 2 in Figure 5 represent any two activities taking place in the system, where function 1 takes the event stimulus as an input and the resulted output comes out from function 2 as a response. These two functions together form an event chain. This event chain also has a desired timing constraint with properties given by jitter, nominal and mode values as shown in this figure.

# 2.2.2. TIMMO Methodology

### 2.2.2.1. Methodology Adaptation

TIMMO being closely associated with AUTOSAR has adopted SPEM [33]. SPEM is the underlying standard for the development of the AUTOSAR Methodology, for development of its own Methodology. SPEM is for modelling software and development processes. Though it is based on UML, it is better suited for software domain and system process engineering than generic UML. SPEM encourages a clear separation of the "method content" from the definitions of either reusable capability patterns or full delivery processes.

TIMMO Methodology adopts itself to the Meta-models derived from EAST-ADL2 and AUTOSAR.

### 2.2.2.2. Methodology Representation

A Meta model such as SPEM cannot be applied without a tool support. For this reason, TIMMO uses Eclipse Process Framework (EPF) Composer, an open source version of the IBM Rational Method Composer. The EPF Composer allows modelling the SPEM method content, capability patterns, and delivery processes. As a result, TIMMO Methodology is available as an XML export library along with a hypertext documentation accessible in web browsers.

#### 2.2.2.3. Methodology Overview and Example

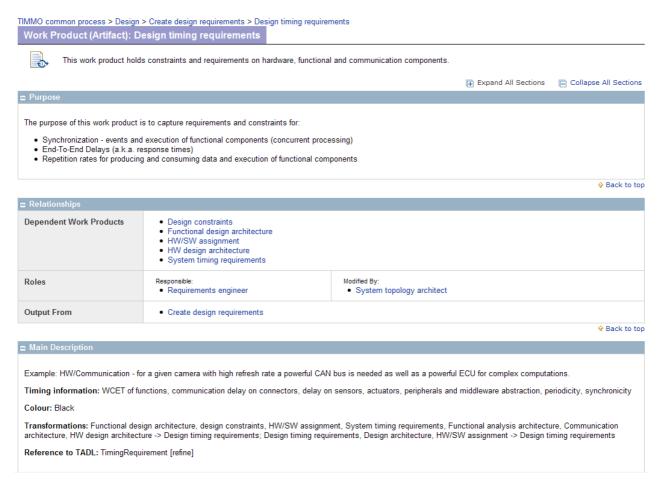

TIMMO Methodology is mainly inspired by the V-Model development approach. The method contents are tasks, work products, roles, and their interrelations. These elements can be linked with tools suitable for performing tasks or by templates, guidelines, or check-lists. Figure 6 shows the TIMMO methodology applied to one of the task in the Design phase called "Create Design Requirements that produces an output work product "Design timing requirements". The table in the main description of the task states that "Design timing requirements" contains timing properties like WCET of the functions, communication delay on the connectors, delay on sensors, periodicity and synchronization.

Figure 6: TIMMO Methodology applied in Design Phase

### 2.3. Validation of TIMMO Results

#### 2.3.1. Validation Process in TIMMO

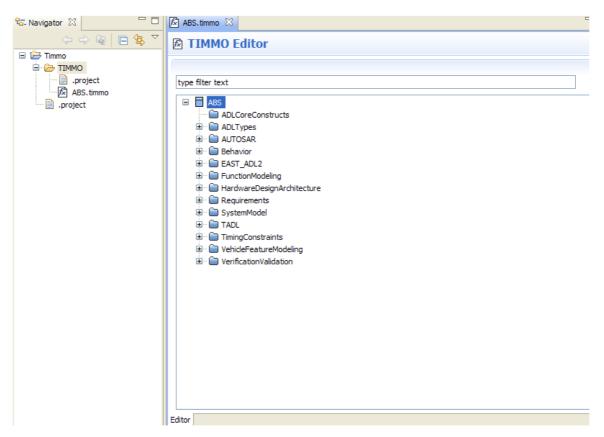

The validator developed in TIMMO is to evaluate TIMMO methodology and use of selected elements of the Timing Augmented Description language (TADL). Each of the validators implements a real-world application with real-time constraints. Each of these validators represents different areas for the validation. These validator systems are examples of real automotive embedded systems like Anti-Lock Brake Systems, Steer-By-Wire, Engine management, Transmission Control and Security System. The main interest in validation was to detect and to handle timing problems when are detected. Hence, the validation processes mainly involved refinement of timing information and timing constraints. For studying these timing behaviour it was necessary to involve timing analysis techniques.

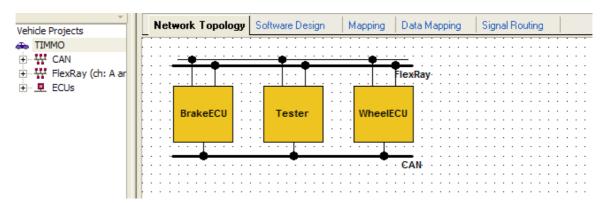

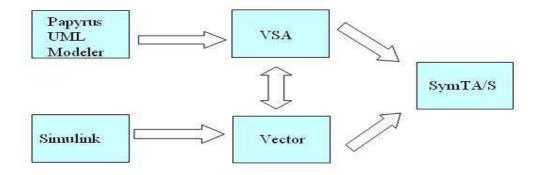

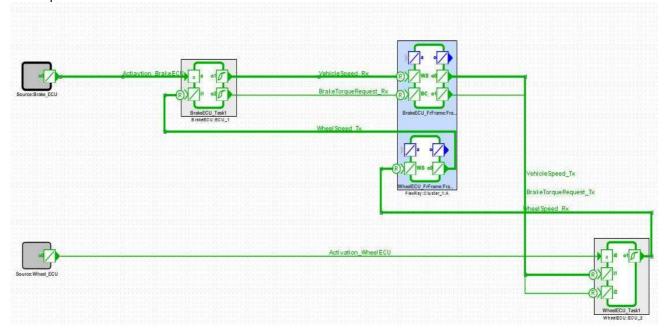

One of validators used in validation process of TIMMO was developed at Volvo Technology, which was a distributed brake-by-wire application with anti-lock braking functionality. The system is modelled according to TADL, EAST-ADL2 and AUTOSAR. A sensor attached to the brake pedal reads the pedal angle, which is used to compute the desired brake torque. A wheel speed sensor is used together with a brake torque to compute the actual brake torque to be applied to the wheel. Using tools like Papyrus and VSA, user models are produced on Vehicle, Analysis and Design levels. A single wheel implementation of the system is built for demonstration. The practical applicability of TIMMO methodology and TADL in designing distributed control systems is shown by this validator system.

### 2.3.2. Techniques Used for Timing Analysis

There are different techniques available for timing analysis. Some of these technologies are studied for applying to TIMMO validators. Below is the list some of the timing analysis techniques studied before any timing analysis performed in validation process.

#### **Model Checking**

Model checking [13] is an automated approach for checking weather a system description (model M) satisfies a given specification. It is mainly applied to hardware design. The system description is given as source code of a hardware descriptive language, which can be modeled by a Finite State Machine (FSM). FSM consists of graphs with nodes representing states of a system. There are two different algorithms for model checking

- 1. Explicit model checking: it checks the model by building transition system of the given system description and verifies the system using graph search algorithms.

- 2. Symbolic model checking: It is based on Binary decision diagrams (BDD) for CTL formulas or on SAT solvers.

#### **Scheduling Analysis**

Scheduling is mainly concerned with assigning time slots to the available computational resources such as processors or hardware/software objects to executable entities (e.g. task) in order to meet the system constraints. Off-line scheduling refers to the scheduling made before the tasks are available on the other hand On-line scheduling refers to a scheduling is generated whiles the tasks are executing.

Scheduling is governed by different classes of constraints such as timing constraints (e.g. deadlines, periodicity), precedence constraints (enforced task ordering) and exclusion constraints (while accessing shared objects).

#### **Real-Time Queuing Theory**

Real-time Queuing Theory (RTQT) [21] provides an approximation method for computing the fraction of tasks that miss their deadlines in systems with high average-case utilization. RTQT takes timing constraints of tasks into account while computing the service times of tasks.

The scheduling policy in RTQT was originally derived from earliest-deadline-first (EDF) policy. EDF results can be used to provide results for other scheduling policies, like static priority approaches or FIFO. RTQT predicts whether an arriving task will miss its deadline or not in a case the task workload exceeds the mean of the deadline distribution.

#### **WCET-Analysis**

WCET is the maximum time taken by a task or a runnables to execute on a particular CPU. Tasks and runnables are the time consuming elements in any OSEK and AUTOSAR execution models. WCET analysis involves mainly two steps which are program analysis and architecture modeling. Program analysis step analyses the execution path through out the control flow where as Architecture modeling determines the time spend on that path in a particular CPU architecture. WCET analysis [45] is different than other techniques as it does not suggest the feasibility of a system rather the results obtained from this analysis are used as input for schedulability analysis, i.e. for finding out whether a real-time embedded system meets all its timing constraints or not.

# 3. TOOL SURVEY AND INVENTORY

One way of doing timing analysis can be by using already existing timing analysis tools that are build on timing analysis techniques. A survey of such tools available for timing analysis was made. These tools were further analyzed for a selection of appropriate tool set on the basis of their provided automotive support.

# 3.1. Tool Survey for Timing Analysis In TIMMO

# 3.1.1. List of Surveyed Timing Analysis Tools

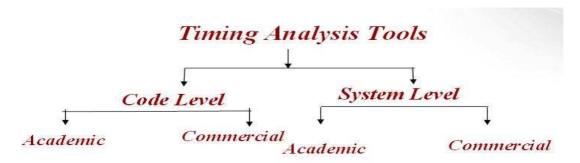

From the survey, tools supporting timing analysis techniques were identified. These tools are present either as commercial or as free academic tools. These tools can be further divided into two main categories based on their performed levels of timing analysis.

- 1. Static Method timing analysis tools: Code Level

- 2. Schedulability analysis tools: System level

Static level timing analysis is based on the code level of the system which basically includes WCET analysis. The broad categorization of timing analysis tools in given in

Figure 7: categorization of timing analysis tools

### 3.1.1.1. Code Level Timing Analysis

Code level timing analysis mainly includes safe upper bounds computation on WCET of sequential tasks. These analyses are performed based on static methods for timing analysis which do not rely on executing code on real hardware or on a simulator, rather obtains upper bounds by taking the task codes into account and combining it with some (abstract) model of the system. Static methods include methods like value analysis, Control flow analysis, Process flow analysis, WCET estimation and symbolic simulations etc.

#### 3.1.1.1.1. Academic *Tools*

#### Heptane:

#### About Heptane [16]:

• Heptane is a timing analysis tool which is licensed under the terms of GNU General Public License (GPL). The software and its source code is licensed free of charge, but any developed version of it should also be released under same GPL licence.

#### Features:

- It computes WCET by static analysis.

- It is designed to read/write XML files.

- It can analyze C source code while taking into account pipeline and instruction caches.

#### Limitations:

• It only supports microcontrollers of Pentium I, MIPS architecture and Hitachi H8/300.

#### SymTA/P

#### About SymTA/P [14]:

• SymTA/P Tool from TU Braunschweig, Germany.

#### Features:

- Obtains upper and lower Execution time bounds of C programs running on microcontrollers.

- The longest and shortest paths in the control flow graph are found by Implicit Path Enumeration Technique (IPET).

#### Limitations:

• The measurement on an evaluation board is more accurate if the program paths between measurements points are longer. If many basic blocks are measured individually, the added time delays to cover pipelining effects would lead to pessimistic WCET.

#### **SWEET**

#### About SWEET [36]:

- It is a prototype tool for WCET analysis developed by the Mälardalen WCET research group

- It is free software, but still a prototype tool (not completely developed as a tool kit).

- Licence is unknown.

#### Features:

- Can handle full ANSI-C programs including pointers, unstructured code, and recursion.

- Integrated with a compiler and performs code flow analysis on the intermediate representation (IR) of the compiler.

- Supports the NECV850E and ARM9 processors.

- Supports three different calculation methods: fast path-based method, global IPET method, and hybrid clustered method.

- Runs on Solaris, Linux and Windows system.

#### calc\_wcetC\_167:

About calc\_wcetC\_167 [44]:

- It was developed by TU-Vienna (University of Vienna). It is a WCET analysis framework that allows analyzing programs given as C source code (written in wcetC, a special dialect developed for WCET analysis) and also as assembly code.

- Initially developed to analyze code for the C167CR processor from Siemens.

- WCET calculation tool are currently only targeted to the C167CR processor from Siemens.

#### Features:

• Calculates WCET on code level. WCET-compiler for wcetC provides a WCET analysis framework that interfaces to the user at source code level. Plain assembly files can be analyzed by adding the required path annotations and calling the low-level WCET analysis tool directly.

#### Limitations:

- At the time of writing this report this tool was under construction.

- Processor specific (currently developed to analyze code for C167CR processor from Siemens).

#### OTAWA:

### About OTAWA [2]:

- This tool is from the Traces Research group on Architectures and Compilers for Embedded Systems at IRIT (University of Toulouse, France). It is freely available under the LGPL licence; hence the latter developed version could be released as free or proprietary software. It is a framework of C++ classes dedicated to static analyses of programs in machine code and computation of WCET.

- Used in several research projects

- 1. MASCOTTE (ANR5), Num@Tec Automotive cluster).

- 2. MORE (ANR).

- 3. MERASA (European project)

#### Features:

- Provides state-of-art WCET analysis like IPET, facilities to work on binary programs (control flow graphs, loop detection and so on).

- Supports architectures like PowerPC, ARM or M68HCS.

### Limitations:

• Works only on Linux (Ubuntu).

#### Tu-Bound:

#### About Tu-Bound [14]:

- Developed at Vienna University of Technology.

- No information on license.

#### Features:

- Tool for worst-case execution time (WCET) analysis of C++ programs.

- Allows high-level annotations to be placed at the source code and has support for static analysis.

- User interface to support the timing analysis with domain-specific knowledge.

• A textual intermediate representation for automatically generated results generated by the static program analysis component.

#### Limitations:

• At the time writing this thesis this tool was not a completely developed as a tool set for timing analysis still a conceptual one.

#### Chronos

#### About Chronos [10]:

- Developed by The Chronos Research Prototype from National University of Singapore.

- Released under GNU GPL and hence a freely available software.

#### Features:

• Supports the analysis of (i) out-of-order pipelines, (ii) various dynamic branch prediction schemes, (iii) Instruction caches, and the interaction among these different features to compute a tight upper bound on the execution times.

#### Limitations:

- Does not analyze data caches.

- Performs limited data flow analysis to compute loop bounds.

#### 3.1.1.1.2. Commercial Tools

#### aiT:

#### About aiT [5]:

- A commercial tool developed by AbsInt GmbH.

- It has WCET Analyzers to compute WCET bounds of tasks in real-time systems.

- Directly analyzes binary executables and takes the intrinsic cache and pipeline behaviour into account.

#### Features:

- Analyzes binary executables.

- Independent of the compiler and source code language used.

- ullet aiT supports integration with state-of-the-art development tools like SCADE Suite, ASCET, SymTA/S, WCC, RT-Druid,

Limitations:

• Evaluation versions of aiT are available for the following processor combinations: ARM7, HCS12/STAR12, PowerPC 555/565/755, C16x/ST10, TMS320C3x, TriCore 1796

#### BoundT:

#### About BoundT [7]:

• Space Systems Finland Ltd (SSF) developed Bound-T at first for the European Space Agency and used it in space projects. Tidorum Ltd is now making Bound-T commercially available.

#### Features:

- BoundT computes bounds on execution time, bounds on stack usage, Control flow graphs and call trees, bounds on counter-type loops.

- Static analysis of machine code covers all cases.

- Context-sensitive: loop-bounds can use parameters.

- Independent of programming language.

#### Limitations:

• Bound-T execution-time analyzer has been adapted to the following target processors: Intel-8051 Series, SPARC V7, Analog Devices ADSP-21020

#### RapiTime:

About RapiTime [29]:

- A commercial tool developed by Rapita Systems.

- A software toolkit that provides solution to the problem of worst-case execution time analysis and performance profiling, a solution that works for complex software running on advanced embedded microprocessors.

#### Features:

- RapiTime supports automatic instrumentation on target testing and execution, Hardware traces capture, Code coverage analysis, Performance profiling.

- It also supports WCET analysis: 1). Determines WCET. 2) Visualizes the contribution of each function to the overall worst-case 3) Examines worst-case execution frequencies 4) Identifies code on the worst-case path 5) Explores the variability in execution times due to hardware effects.

- Targeted optimisation.

- Support for C and Ada.

#### 3.1.1.2. System Level Timing Analysis

System level timing-analysis is done by executing task sets on the given hardware or a simulator with given set of inputs, and measuring the execution time of the tasks. This mainly includes approaches for End-to-end measurements of a subset of all possible executions, measure the execution times of code segments, typically of CFG (Control flow graphs) basic blocks, bound calculation, to produce estimates of the WCET or BCET, schedulability of task set.

The measurements made in static methods can be necessary inputs for system level analysis.

#### 3.1.1.2.1. Academic Tools

#### Cheddar

About Cheddar [46]:

Cheddar is developed and maintained by LISyC Team, University of Brest. It is written in Ada. Graphical editor is made with GtkAda. It runs on win32 boxes, Solaris, Linux. Cheddar is a free real-time Scheduling tool that analyzes systems in AADL [1] or any Cheddar specific languages.

#### Features:

- It supports Scheduling Simulations with real-time schedulers:

- Rate Monotonic Analysis [22] (RMA, RM, RMS), Earliest Deadline First (EDF), Deadline Monotonic (DM, Inverse Deadline), Least Laxity First (LLF).

- Scheduling and queuing policies.

- It provides information for study of real-time Systems: Worst /Best/Average Blocking time, Worst /Best/Average Response time, Number of preemptions, of context switches, Deadlocks, priority inversions, Missed Deadlines.

- It also facilitates applying feasibility tests: Tests based on EDF, LLF, RM, DM, Bound on response time and on blocking times, Support for shared resources, Partitioning tools to assign tasks on multiprocessors.

- It has relevance with Automotive Domain:

- Support for distributed embedded system.

- CAN, LIN, FlexRay

- No particular feature to support AUTOSAR.

#### MAST:

#### About MAST [19]:

- Modelling and Analysis Suite for real-Time Applications.

- a free software

#### Features:

- Worst-case response time schedulability analysis (RTA)

- Calculation of blocking times of Single processor, Remote blockings for multi-processor, Assignment of optimum priority ceilings and pre-emption levels.

- Relevance with Automotive Domain:

- Support for distributed embedded system.

- CAN, LIN, FlexRay.

- No particular feature to support AUTOSAR.

#### 3.1.1.2.2. Commercial Tools

#### SymTA/S:

SymTA/S [34] is developed and maintained by Symtavision. It is used for budgeting, scheduling verification and optimization for processors, electronic control units (ECUs), communication buses, networks and complete integrated systems.

#### Features:

- Scheduling Analysis Engine is the core component.

- It has support for sensitivity analysis and design space exploration.

- It has automotive analysis libraries available for: OSEK, AUTOSAR OS, CAN and FlexRay

- Calculates signal and message delay and jitter on a bus.

- Determines end-to-end signal delay and jitter for gated networks.

- Exploring various protocol and COM parameters to optimize bus and network performance.

- It provides optimization of CAN scheduling.

- It also provides path analysis with

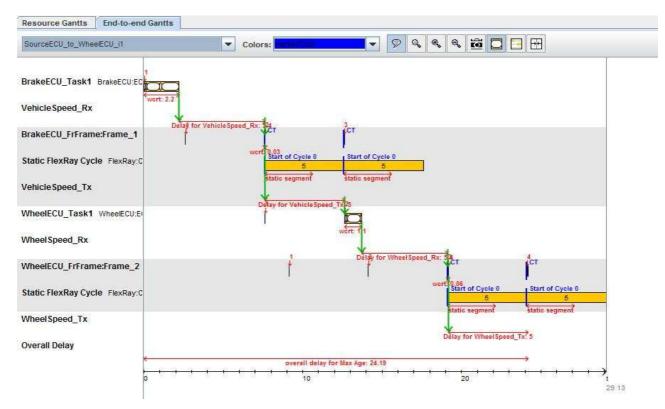

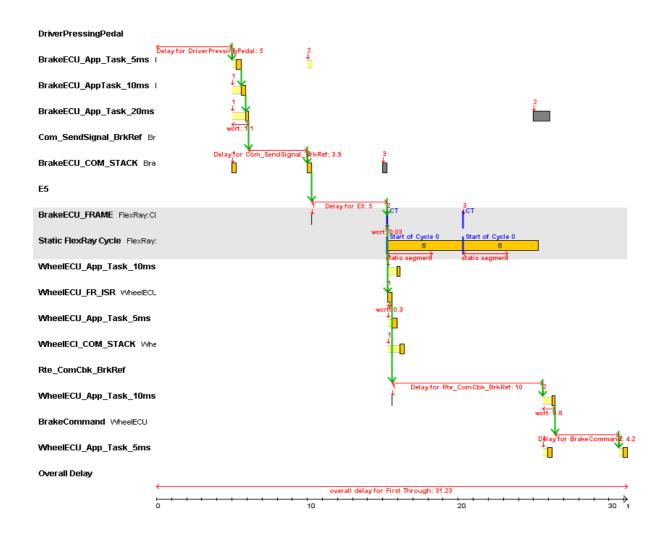

- *Maximum Age:* the maximum path delay is determined with respect to the oldest data (maximum age) that can traverse through the path. Earlier read accesses to the same data are ignored if they do not contribute to the worst-case path delay [27].

- First Through: the maximum path delay is determined with respect to the first signal that can traverse through the End-to-End signal path. Later read accesses to the same data are ignored if they do not contribute to the worst-case path delay [27].

- Relevance with Automotive Domain:

- Support for distributed embedded system.

- CAN, LIN, FlexRay

- No particular feature to support AUTOSAR

- It has multi processor support:

#### RapidRMA:

RapidRMA [28] is a commercial tool based on research conducted at the University of Illinois at Urbana-Champaign. It is a product by Tri-Pacific Software.

#### Features:

- Timing and scheduling analysis environment

- Utilizes Rate Monotonic Analysis (RMA) methodology, Deadline Monotonic Analysis (DMA) and Cyclic Executive Analysis.

- End-to-end analysis for single-node and multiple-node architectures

- Multi Processor support.

- Design Space exploration

#### Relevance with Automotive Domain:

- Support for distributed embedded system.

- CAN, LIN, FlexRay

- AUTOSAR support

#### RT-Druid:

#### About RT-Druid:

RT-Druid [30] is a development environment for ERIKA Enterprise which is based on Eclipse composed by a set of plug-in for the Eclipse Framework.

#### Features:

- It supports fixed priority schedulability analysis technique

- It has multi processor support:

#### Relevance with Automotive Domain:

- Support for distributed embedded system.

- CAN, LIN, FlexRay

- AUTOSAR support

#### SCADE Suite:

#### About SCADE [31] Suite:

- Model based development environment dedicated to embedded software from Esterel Technologies. It is used most heavily in the aerospace and defence domains.

- It claims to serve transportation, automotive, energy, and heavy equipment software development environments.

#### Features:

- Integration of aiT and Stack Analyzer, SCADE is the embedded-software development environment featuring WCET analysis and stack usage analysis at the model level.

- It has a graphical and textual editor, Simulator

- Auto code generation of C code with properties of safety critical system.

- It has gateways for Simulink, UML/ SysML,[24].

# 3.1.2. Required Tool Properties for Timing Analysis

The basic requirement for timing analysis in TIMMO is mainly the hardware and software support. The most suitable tools for this timing analysis are the one that has the required hardware and software supports matching TIMMO requirements. Following is the list of H/W and S/W support required in TIMMO:

# 3.1.2.1. For Static Method Timing Analysis

- <u>Compiler support:</u> any C compiler,

- Architecture support: PowerPC

- Requirements in Timing analysis aspects: WCET calculation

- C code analysis support

- Operating System: OSEK/AUTOSAR OS

# 3.1.2.2. For System Level Timing Analysis

- Architecture support: PowerPC

- Microcontroller: MCP5517G(Freescale)

- Requirements in Timing analysis aspects: real-time algorithmic analysis support, jitter calculation, scedulability analysis, end to end timing analysis.

- <u>Automotive domain support:</u> AUTOSAR

- Operating System: OSEK / AUTOSAR OS

- Network Protocol support: CAN ,FlexRay

- Multi-processor analysis support.

# 3.1.3. Tool Evaluation with TIMMO Requirements

Table1 gives comparative study of tools on basis of TIMMO requirements. The list of requirements can be considered as a complete list for all abstraction levels defined in TADL.

| Timing analysis Requirements for TIMMO | Tool supporting requirements                                 |

|----------------------------------------|--------------------------------------------------------------|

| C Compiler support                     | Heptane, SWEET, calc_wcetC_167, OTAWA, aiT, BoundT, RapiTime |

| Architecture support(PowerPC)          | OTAWA, RapiTime, SymTA/S, SCADE Suite                        |

| Microcontroller: (freescale:           | SymTA/S, SCADE Suite                                         |

| MCP5517G)                                                                             |                                                                       |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| WCET calculation                                                                      | Heptane, SWEET, calc_wcetC_167, Chronos, OTAWA, aiT, BoundT, RapiTime |

| C code analysis support                                                               | Heptane, SWEET, calc_wcetC_167, OTAWA, aiT, BoundT, RapiTime          |

| Operating System (OSEK / AUTOSAR OS)                                                  | SymTA/S                                                               |

| Jitter calculation, end to end timing analysis, response time analysis, scedulability | Cheddar, SymTA/S, SCADE Suite                                         |

| AUTOSAR support                                                                       | SymTA/S                                                               |

| Network Protocol support(CAN, FlexRay, LIN)                                           | SymTA/S                                                               |

| Multi-processor analysis support                                                      | SymTA/S                                                               |

Table 1: Evaluation of Timing Analysis Tools

### 3.1.4. Tool Selection

The selection is done either by comparing the tool features with actual requirement or by creating a timing analysis model. The methods are elaborated as follows.

# 3.1.4.1. Selection by Requirement Analysis

From Table 1, we can have a clear view of the tools that fulfil the main requirements. From this requirement analysis, a selection of the most suitable ones is made. For static method of timing analysis most of the tools fulfil the basic requirements like the binary code analysis support, WCET calculation, C code analysis support etc. The tools that are not completely developed or are still conceptual are not taken it consideration. Hence the final selections of the tools that are actually suitable for static method of timing analysis are **Heptane**, **OTAWA**, **aiT**, **RapiTime and BoundT**.

For System level timing analysis most of the tools were evaluated on the basis of AUTOSAR, OSEK and different prototype support. The most suitable ones thus found out to be **Cheddar**, **MAST**, **SymTA/S**, **RT-Druid** and **SCADE** suite.

# 3.1.4.2. Selection by Modeling of Real System

The previous selection of tools was still evaluated by making a timing analysis of a real system example. For code level timing analysis RapiTime trial version is used for timing analysis and the necessary WCET calculation were obtained. For System level timing analysis Cheddar, MAST and SymTA/S were used for timing analysis of the system and for schedulability analysis. Especially SymTA/S was used for modelling the system and analysing the timing aspects of TIMMO.

# 3.2. Tool Inventory

TIMMO aims at adding timing information in all development phases of an automotive electronic system. Thus the Time Augmented Descriptive Language (TADL) developed in TIMMO allows describing timing aspects in such systems and specifies itself as a UML metamodel. The TIMMO methodology is developed in order to give highlighted timing issues in exchanging and communicating timing aspects in TADL. The methodology is based on a development process induced by EAST-ADL and AUTOSAR generally consists of tasks and their work products.

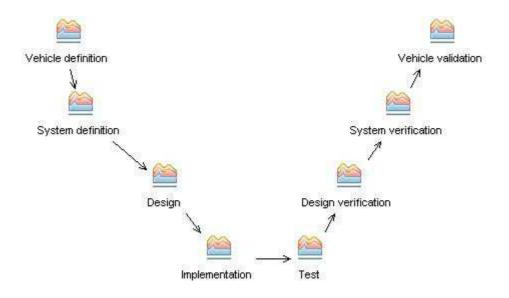

Figure 8 is the V model followed in TIMMO methodology. The selected tools in section [3.1.4] were evaluated according to the timing relation studied in these tasks and their work products.

Figure 8: TIMMO work Break down Structure

# 3.2.1. Tool Inventory of Task

Following tables, different tasks and their work products are discussed at different phases of development with regards to the timing issues faced and the tools that may support to analyse these timing issues.

#### 3.2.1.1. Vehicle Definition Phase

In Vehicle Definition phase, the requirements of the proposed vehicle are collected by analyzing the users' need. This phase is concerned about establishing the performance of an ideal system; however it is not concerned with determining issues related to system design. The information is collected from users' view of the system; hence the identified requirements are from the perspective of external stakeholders only. The system is then documented in terms of functional, physical, interface, performance, data, security requirements etc and then it is used by the business analysts to communicate their understanding of the system back to the users. After careful review of this document by users, this document serves as the guideline for the system designers in the system definition phase.

| TIMMO tasks                  | Task Output(s)                        | Timing Relations of<br>Output(s)           | Possible timing analysis tool(s) to be used |

|------------------------------|---------------------------------------|--------------------------------------------|---------------------------------------------|

| Create vehicle feature model | Vehicle feature model                 | None                                       | N.A                                         |

| Create vehicle requirements  | Vehicle feature model                 | None                                       | N.A                                         |

|                              | Vehicle timing requirements: External | External end-to-end delay between features | SymTA/S                                     |

|                              | end-to-end delay                                       |                                               |                                           |

|------------------------------|--------------------------------------------------------|-----------------------------------------------|-------------------------------------------|

|                              | Vehicle timing requirements: Internal end-to-end delay | Internal end-to-end<br>delay between features | SymTA/S,<br>Cheddar                       |

|                              | Vehicle timing requirements: Internal end-to-end delay | End-to-end delay                              | SymTA/S                                   |

|                              | Vehicle timing requirements: Synchronization feature   | Synchronisation between features              | SymTA/S                                   |

|                              | Vehicle timing requirements: Synchronization feature   | Synchronisation between features              | SymTA/S                                   |

| Validate timing requirements | Timing requirement validation report                   | Validated timing requirements                 | BoundT, aiT,<br>Cheddar,<br>SymTA/S, MAST |

Table 2: Tool Inventory in Vehicle Definition Phase

# 3.2.1.2. System Definition Phase

In Systems Definition Phase user requirements document is analyzed by system engineers. The feasibility and techniques of the user requirements to be implemented is found out. The user is informed, if any of the requirements are not feasible. The user requirement document is edited after a resolution is found. The end product of this phase is the system definition document which contains the general system organization, structures.

| TIMMO tasks                                                       | Task Output(s)                   | Timing Relations of<br>Output(s)                                                     | Possible timing analysis tool(s) to be used |

|-------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------|

| Analyse and verify timing in the functional analysis architecture | Control performance report       | Verified End-to-end<br>delay, Verified<br>Synchronisation,<br>Verified Timing budget | Cheddar,<br>SymTA/S, MAST                   |

| Analyse control performance with respect to timing                | Control performance report       | Verified End-to-end<br>delay, Verified<br>Synchronisation,<br>Verified Timing budget | Cheddar,<br>SymTA/S, MAST                   |

| Analyse user ergonomics with respect to timing                    | User ergonomics report           | Analyse user ergonomics with respect to timing?                                      | Cheddar,<br>SymTA/S, MAST                   |

| Create functional analysis architecture                           | Functional analysis architecture | none                                                                                 | N.A                                         |

| Create system requirements                                        | Functional analysis architecture | none                                                                                 | N.A                                         |

|                                                                   | System timing requirements       | End-to-end delay,<br>Synchronisation ,<br>Timing budget                              | SymTA/S                                     |

# 3.2.1.3. Design Phase

This phase is depicted as the high-level design phase.

| TIMMO tasks                                                           | Task Output(s)                         | Timing Relations of<br>Output(s)                                                                                                                                        | Possible timing analysis tool(s) to be used            |

|-----------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Analyse application timing                                            | Performance report                     | none                                                                                                                                                                    |                                                        |

| Analyse response times                                                | Response time analysis report          | Response time corresponding to each timing requirement                                                                                                                  | SymTA/S, SCADE<br>Suite                                |

| Assess resource consumption                                           | Resource consumption assessment report | An answer to whether an identified set of functions can be scheduled on the identified target                                                                           | Cheddar,<br>SymTA/S                                    |

| Assign design timing properties                                       | Design timing properties               | WCET of functions,<br>communication delay on<br>connectors, delay on<br>sensors, actuators,<br>peripherals and<br>middleware abstraction.                               | BoundT,<br>RapiTime, aiT,<br>Cheddar,<br>SymTA/S, MAST |

| Assign functionality<br>to HW or SW                                   | Design constraints                     | End-to-end timing requirements, Control rate, Input data age, Synchronisation of input and output                                                                       | SymTA/S                                                |

|                                                                       | HW design architecture                 | Computation rate                                                                                                                                                        |                                                        |

| Create design                                                         | Design architecture                    | none                                                                                                                                                                    | N.A                                                    |

| requirements                                                          | Design timing requirements             | WCET of functions,<br>communication delay on<br>connectors, delay on<br>sensors, actuators,<br>peripherals and<br>middleware abstraction,<br>periodicity, synchronicity | BoundT, aiT,<br>Cheddar,<br>SymTA/S, MAST              |

| Create functional                                                     | Functional design architecture         | none                                                                                                                                                                    | N.A                                                    |

| design architecture                                                   | Middleware abstraction                 | none                                                                                                                                                                    | N.A                                                    |

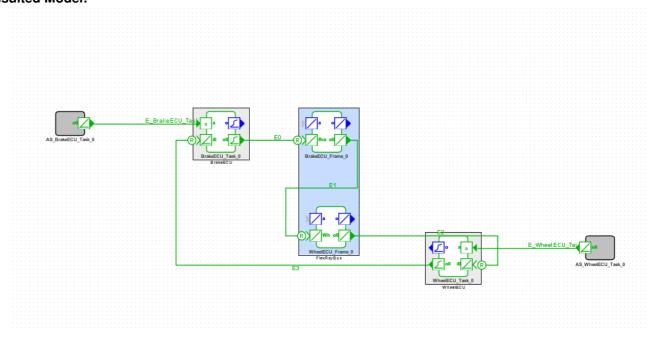

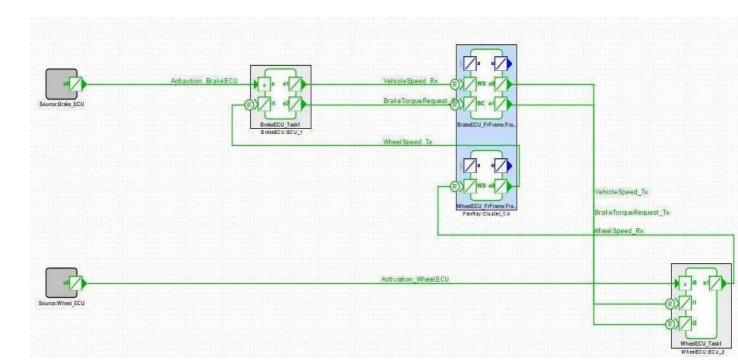

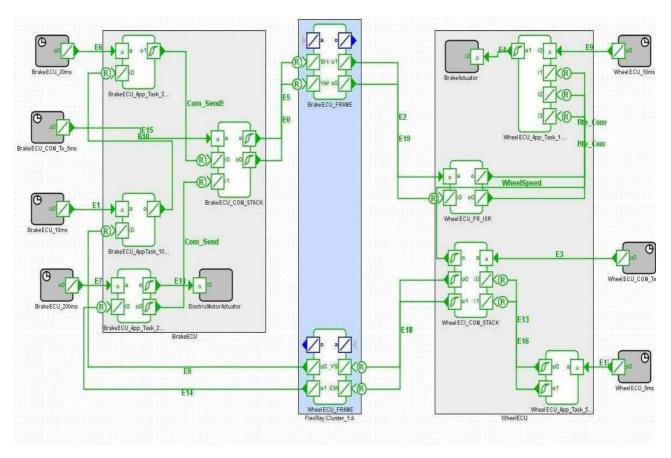

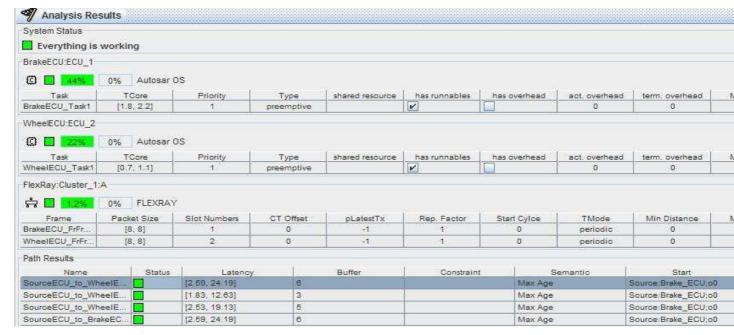

| Create HW design<br>and communication<br>design<br>architectures      | HW design architecture                 | Computation rate?                                                                                                                                                       |                                                        |